一、实验要求

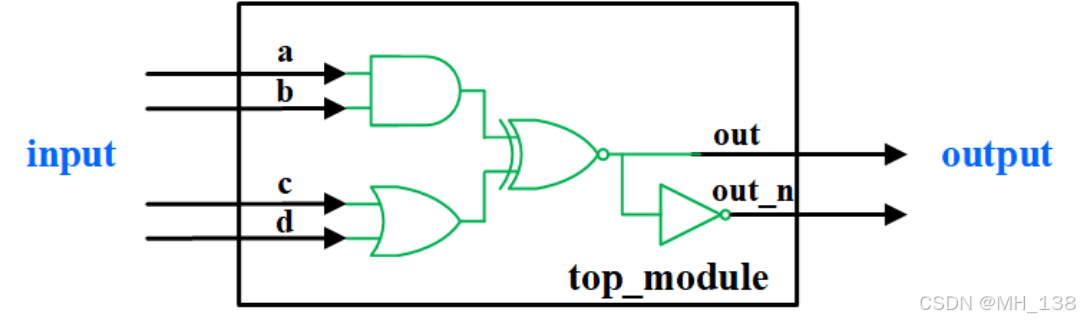

- 第5关 内部信号:请参考下图,声明必要的内部信号,采用持续赋值语句assign完成电路的建模。

- 第7关 向量域选(2):一个32位向量信号in由4个字节组成(in[31 : 24],in[23 : 16],in[15 : 8],in[7 : 0]),请采用向量域选实现字节顺序的颠倒。

二、实验内容及步骤(包括设计过程,逻辑图,电路图)

- 第5关 内部信号:

- 图片分析:

在给出的电路图中,我们可以看到,输入信号a\b间是一个与门,c\d间是一个或门,在经过两个门后,我们定义信号经过两门后分别变为and_out和or_out,两者来到一个异或门,经过异或门后,信号的直接输出为out,再经历一个非门后输出为out_n。

- 成功代码:

module wire_decl (

input a, b, c, d,

output out, out_n

);

// 代码量预计5行

wire and_out, or_out;

assign and_out=a&b;

assign or_out=c|d;

assign out=~((and_out&(~or_out))|((~and_out)&or_out));

assign out_n=~out;

endmodule

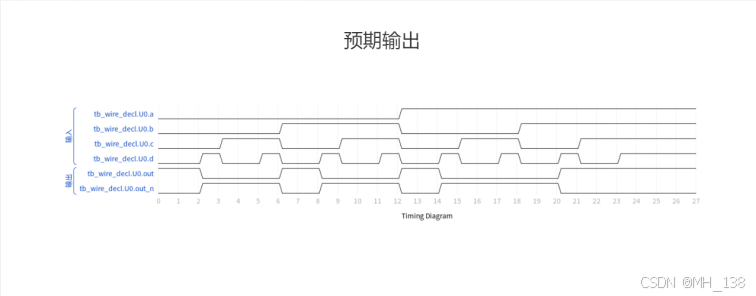

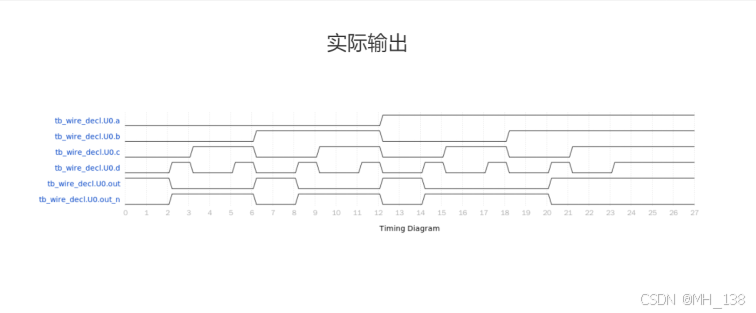

- 输出信号对比:

- 第7关 向量域选(2):

- 输入输出定义:

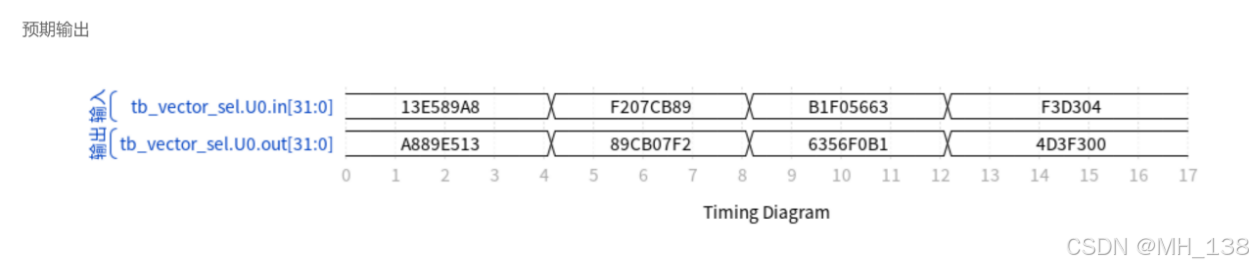

在本代码中,事先在定义中给出的in是32位输入信号,由4个字节(in[31:24]、in[23:16]、in[15:8]、in[7:0])组成;out是颠倒字节顺序后的32位输出信号。

- 成功代码:

module vector_sel (

input [31 : 0] in,

output [31 : 0] out

);

// 代码量预计4行

assign out[31:24]=in[7:0];

assign out[23:16]=in[15:8];

assign out[15:8]=in[23:16];

assign out[7:0]=in[31:24];

endmodule

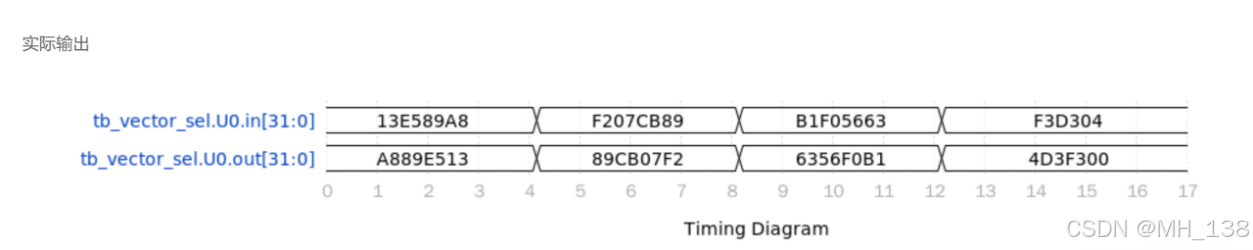

- 输出结果对比:

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?