今天学到了全加器的进位机制。分为串行和并行两种 。串行进位链的高位进位依靠低位进位,进位逐级产生,每个进位产生需两个与非门,假设与非门的门级延迟为Ty,则n位全加器产生全部进位的延迟为:2n*Ty。并行进位链可以同时产生多个进位。若所有进位全部产生,则延迟为2Ty,问题为:电路异常复杂,折中方法有两个:单重分组跳跃进位和双重分组跳跃进位。

单重分组跳跃进位:

将n位全加器分为k组,每组内的进位并行产生,小组间为串行进位。

双重分组跳跃进位:

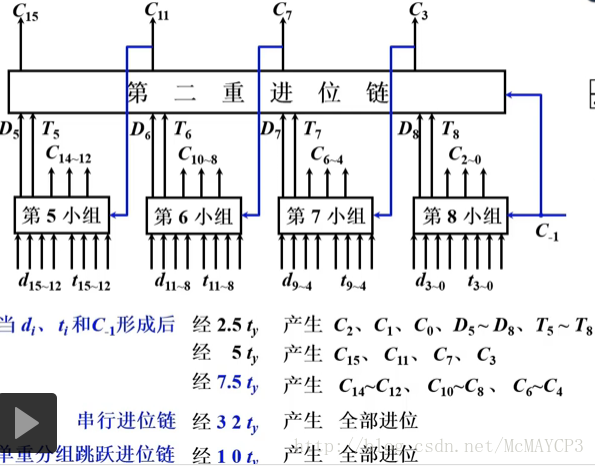

将n位全加器分为k大组,每大组内包含若干小组,每个大组内的各个小组的高位进位同时产生。大组之间串行进位。

如下图所示:

上图演示的是n=32,分为2个大组时第2个大组的进位产生电路。分为两级:

第一级为:各个小组内通过与非门加非门产生Ti, Di;如下图所示:

本文介绍了全加器的串行和并行进位机制,重点讨论了单重分组跳跃进位和双重分组跳跃进位的原理。双重分组跳跃进位通过将n位全加器分为k大组,每个大组内部并行产生高位进位,大组间串行进位,显著减少了延迟时间,例如n=32时,仅需10Ty即可完成全部进位。

本文介绍了全加器的串行和并行进位机制,重点讨论了单重分组跳跃进位和双重分组跳跃进位的原理。双重分组跳跃进位通过将n位全加器分为k大组,每个大组内部并行产生高位进位,大组间串行进位,显著减少了延迟时间,例如n=32时,仅需10Ty即可完成全部进位。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

465

465

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?