简介

先列出几个要用到的寄存器:

- LOCKCON0

- LOCKCON1

- OSCSET

- MPLLCON

- EPLLCON

- EPLLCON_K

这6个寄存器控制着2个内部的PLL锁相环,一个外部的晶体振荡器。这两个独立的PLL锁相环的输出值分别由MPLLCON和EPLLCON的设置值来决定。锁相环的稳定输出时间由LOCKCON0和LOCKCON1决定。晶体振荡器的稳定时间由OSCSET决定。

通常情况下,锁相环再被打开后,回向系统各个模块提供输出,但在稳定输出前,会有一些小抖动输出,为了过滤这些抖动输出,就需要在PLL被打开后,延迟一段时间再对各模块输出时钟,这里用到的延时值设置寄存器就是LOCKCON0和LOCKCON1,这两个分别设置MPLL和EPLL的稳定输出前的延时值。通常情况下,延时都至少大于300us。

而晶体振荡器要稳定的时间要得按照手册推荐值设置。

1.先设置锁相环的输出,包括MPLLCON、EPLLCON

1.1 配置主时钟MPLLCON

根据数据手册中的推荐值的设定,分别将MDIV设置成400,PDIV设置成3,SDIV设置成1,这样MPLLCON的值就=0x00640061,即PLL输出为800MHZ。因为接下来要用MPLL,所以打开了MPLL的输出。

0000 0000 0110 0100 0000 0000 0110 0001

即,MPLLCON = 0x00640061

1.2 配置副时钟EPLLCON

根据数据手册中的推荐值的设定,分别将MDIV设置成32,PDIV设置成1,SDIV设置成2,这样MPLLCON的值就=0x01200102,即EPLL输出为96MHZ

因为用不到,所以在bootstrap.bin中关闭了EPLL的输出。

0000 0001 0010 0000 0000 0001 0000 0010

即,EPLLCON = 0x01200102

1.3 配置主时钟的稳定输出缓冲延时时间值

LOCKCON0 = 0x0000ffff

1.4 配置副时钟的稳定输出缓冲延时时间值

LOCKCON1 = 0x0000ffff

2.配置各模块时钟,包括ARMCLK、HCLK、PCLK、SCLK

上面设置了锁相环的输出之后,接下来设置各模块的时钟值,PLL只是稳定输出,至于每个模块用到的时钟,我们需要分别设置各个模块需要用到的分频器和与分频器的值。

- CLKSRC

- CLKDIV0

- CLKDIV1

- CLKDIV2

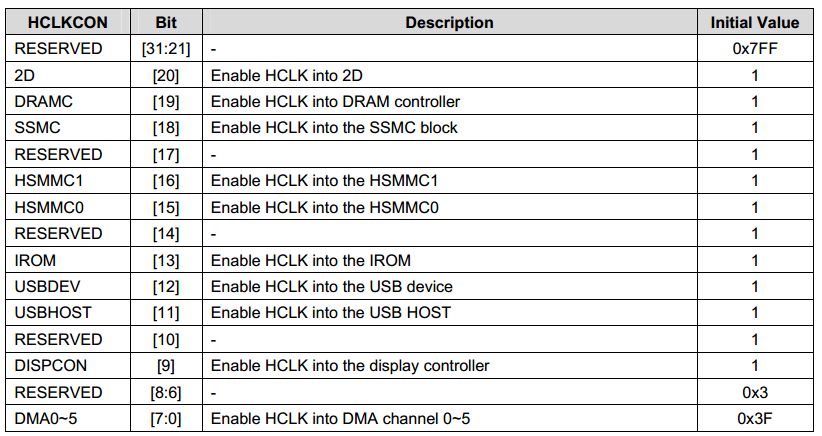

- HCLKCON

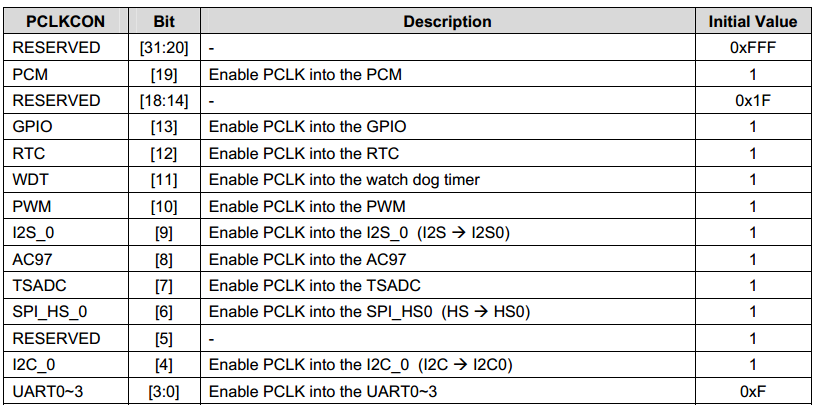

- PCLKCON

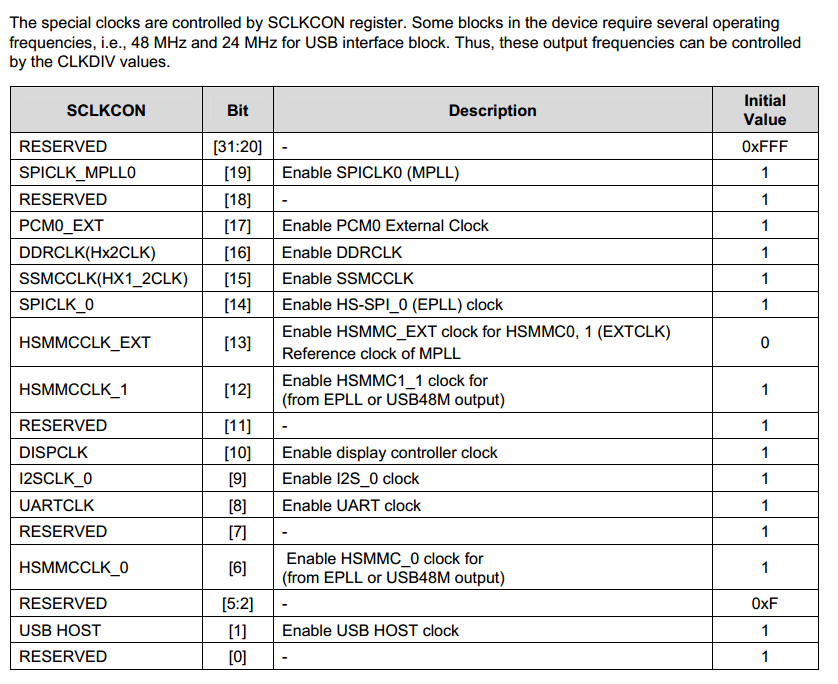

- SCLKCON

2.1 设置CLKSRC,选择时钟源

0000 0000 0000 0000 0000 0001 0101 1000

即, CLKSRC = 0x00000157

2.2 设置CLKDIV0,该寄存器将设置MPLL各模块时钟的预分频系数值

0000 0000 0000 0000 0000 0010 0010 1101

即,CLKDIV0=0x0000022d

这样设置后,基于MPLL=800MHZ的输出,得到了ARMCLK=400MHZ,HCLK=133MHZ PCLK=66MHZ

2.3 设置CLKDIV1,该寄存器将设置EPLL各模块时钟的预分频系数值

0000 0000 0000 0000 0000 0000 0000 0000

即,CLKDIV1=0x00000000

2.3 设置CLKDIV2,该寄存器将设置HSMMC各模块时钟的预分频系数值

0000 0000 0000 0000 0000 0000 0000 0000

即,CLKDIV2=0x00000000

2.4 设置HCLKCON, 根据用到的外设进行对应的时钟使能

根据你用到的来使能,默认是全部使能的

1111 1111 1111 1111 1111 1111 1111

即,HCLKCON=0xffffffff

2.4 设置PCLKCON, 根据用到的外设进行对应的时钟使能

1111 1111 1111 1111 1111 1111 1111

即,PCLKCON=0xffffffff

2.4 设置SCLKCON, 根据用到的外设进行对应的时钟使能

1111 1111 1111 1101 1111 1111 1111

即,SCLKCON=0xffffdfff

3. 懒得看过程的,直接看结果放这里

MPLLCON = 0x00640061

EPLLCON = 0x01200102

LOCKCON0 = 0x0000ffff

LOCKCON1 = 0x0000ffff

CLKSRC = 0x00000157

CLKDIV0=0x0000022d

CLKDIV1=0x00000000

CLKDIV2=0x00000000

HCLKCON=0xffffffff

PCLKCON=0xffffffff

SCLKCON=0xffffdfff

上面的配置结果是,将ARMCLK设置成400MHZ,HCLK=133MHZ,PCLK=66MHZ 所有外设全部使能。

842

842

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?