一、 实验目的

1、掌握基于 Verilog 语言的 diamond 工具设计全流程。

2、熟悉、应用 Verilog HDL 描述数字电路。

3、掌握 Verilog HDL 的组合和时序逻辑电路的设计方法。

4、掌握“小脚丫”开发板的使用方法。

二、 实验原理

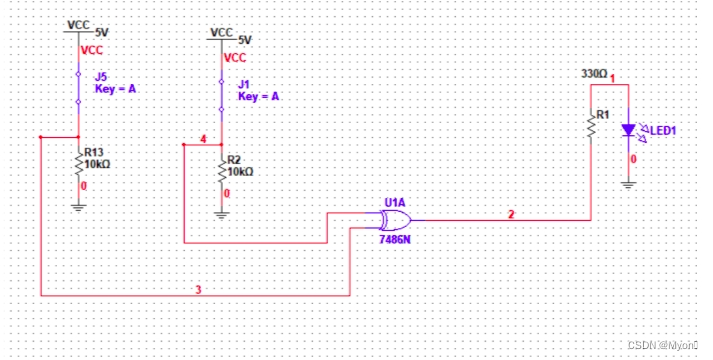

与门逻辑表达式:Y=AB

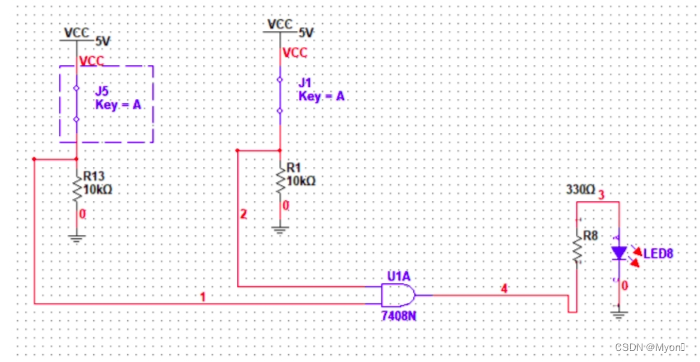

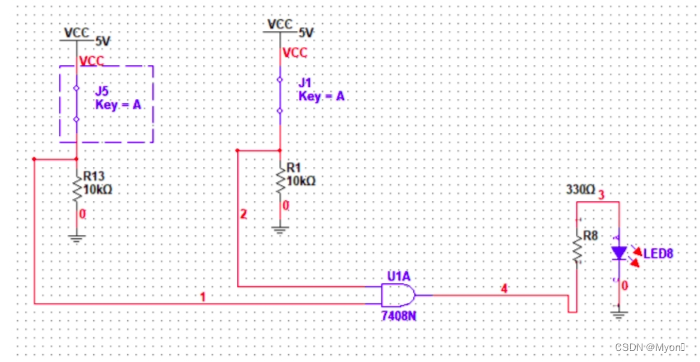

原理仿真图:

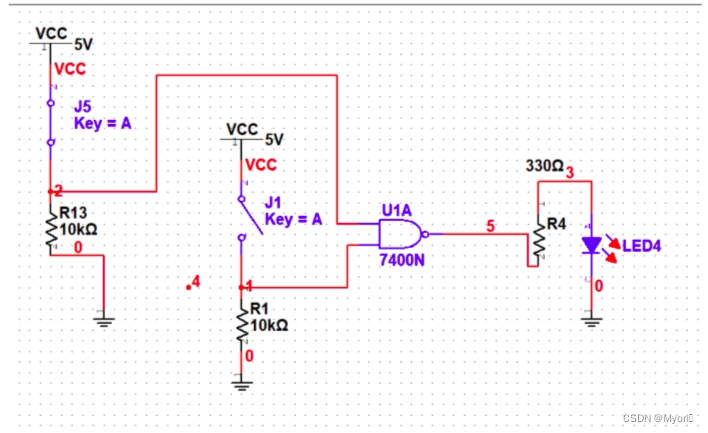

2 输入与非门逻辑表达式:Y=(A·B)'=(A')+(B')

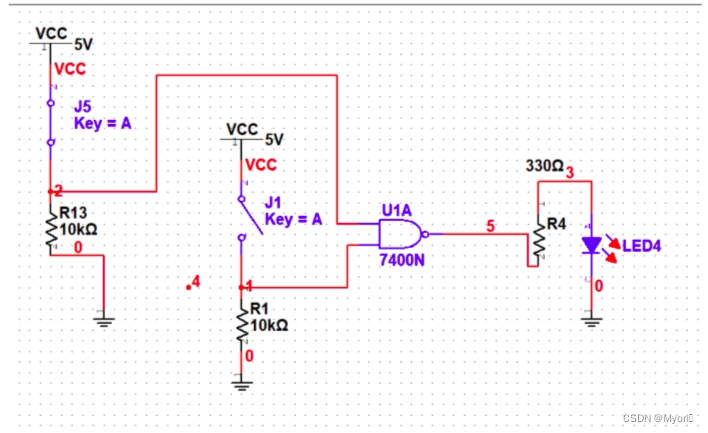

原理仿真图:

4 输入与非门逻辑表达式:Y=A’+B’+C’+D’

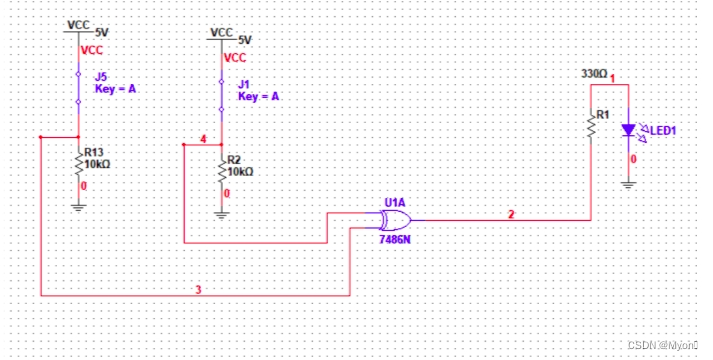

原理仿真图:

1、掌握基于 Verilog 语言的 diamond 工具设计全流程。

2、熟悉、应用 Verilog HDL 描述数字电路。

3、掌握 Verilog HDL 的组合和时序逻辑电路的设计方法。

4、掌握“小脚丫”开发板的使用方法。

与门逻辑表达式:Y=AB

原理仿真图:

2 输入与非门逻辑表达式:Y=(A·B)'=(A')+(B')

原理仿真图:

4 输入与非门逻辑表达式:Y=A’+B’+C’+D’

原理仿真图:

555

555

538

538

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?