一、实验目的

1、掌握用SSI(小规模集成电路)逻辑器件设计组合电路的方法。

2、掌握组合逻辑电路的调试方法。

3、学会分析和解决实验中遇到的问题。

4、学会用FPGA实现本实验内容。

二、实验原理

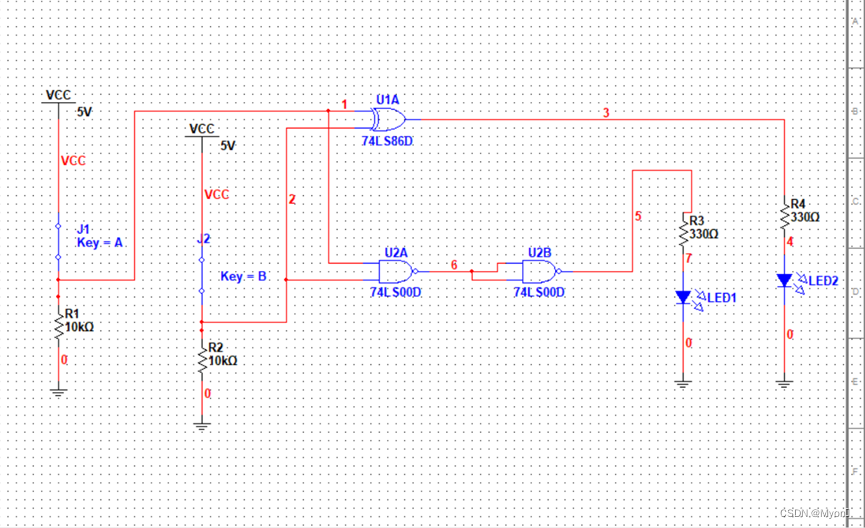

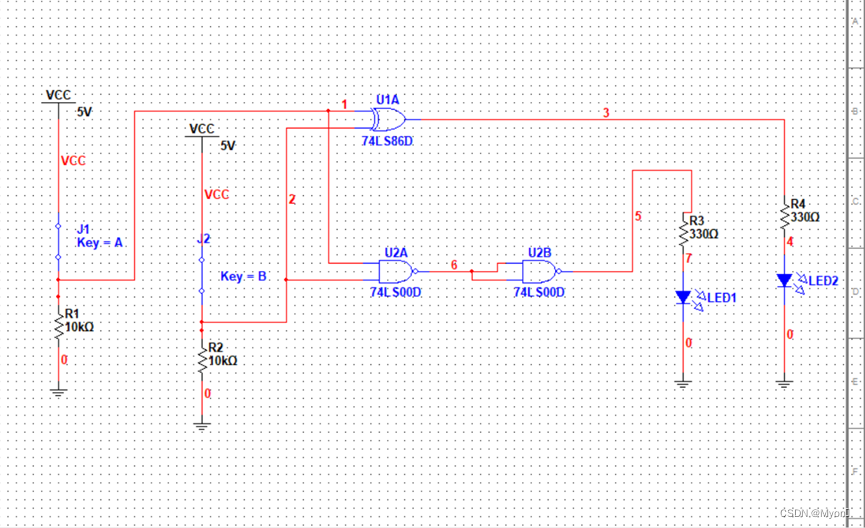

包括:原理图绘制和实验原理简述

1、1位半加器

一、实验目的

1、掌握用SSI(小规模集成电路)逻辑器件设计组合电路的方法。

2、掌握组合逻辑电路的调试方法。

3、学会分析和解决实验中遇到的问题。

4、学会用FPGA实现本实验内容。

二、实验原理

包括:原理图绘制和实验原理简述

1、1位半加器

2230

2230

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?