规模的整数加法在数字信号处理和图像视频处理领域应用很多,其对资源消耗很多,如何能依据FPGA物理结构特点来有效降低加法树的资源和改善其时序特征是非常有意义的。本篇论文是基于altera公司的FPGA,利用其LUT特点,探索设计最大程度利用LUT以及改善时序的compressor树的结构。

01

半加器和全加器

半加器是两个输入bit相加,输出结果S和进位C。表达式为:

全加器是三个bit相加,有进位参与,表达式为:

![]()

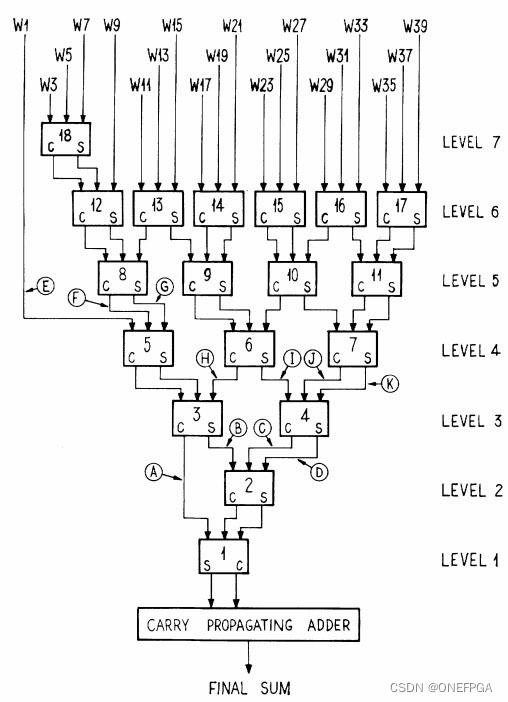

Compressor树就是在全加器的基础上建立的,通过全加器的S和C结果相互连接形成多层树状结构,其相比于普通的进位加法树消耗更少资源。普通进位加法树是用两个或者三个加法模块连接成树,形成多层结构来计算多输入加法。放一张wallace树的经典文献中的图片来大致了解一下compressor树的结构。

图1.1 compressor树结构

02

Compressor树

Compressor树就是在图1.1中carry propagating a

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

8207

8207

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?