小猫爪:i.MX RT1050学习笔记7-Power Supply电源设计

1 前言

在前面文章《小猫爪:i.MX RT1050学习笔记6-Low Power电源设计》中我们介绍了RT1050的电源模块,可以给RT1050提供非常丰富的电源管理操作,因为RT内部电源模块设计的复杂,所以外部电源的supply也相应的变得复杂,接下来我们就来简单介绍一下RT1050关于外部电源的设计。

2 与电源相关的引脚

下表列出了RT1050中与Power Supply有关的引脚。

| 电源引脚名称 | 最小值 (V) | 典型值 (V) | 最大值 (V) | 说明 |

|---|---|---|---|---|

| VDD_SOC_IN | 0.925 | — | 1.3 | 内核供电电源 |

| VDD_HIGH_IN | 2.8 | 3.3 | 3.6 | VDD_HIGH_IN电源电压 |

| DCDC_IN | 2.81 | 2.91 | 3.31 | DCDC电源 |

| VDD_SNVS_IN | 2.4 | 3 | 3.6 | SNVS和RTC电源 |

| USB_OTG1_VBUS USB_OTG2_VBUS | 4.4 | 5 | 5.5 | USB VBUS电源 |

| VDDA_ADC | 3 | 3.3 | 3.6 | 12位ADC电源 |

| VDDA_IN | 3 | 3.3 | 3.6 | 12位ADC电源 |

| NVCC_SD0 | 3 1.65 | 3.3 1.8 | 3.6 1.95 | SDIO1组中的GPIO电源(3.3V模式) SDIO1组中GPIO电源(1.8V模式) |

| NVCC_SD1 | 3 1.65 | 3.3 1.8 | 3.6 1.95 | SDIO2组中GPIO电源(3.3V模式) SDIO2组中GPIO电源(1.8V模式) |

| NVCC_EMC | 3 1.65 | 3.3 1.8 | 3.6 1.95 | EMC组中GPIO IO电源(3.3V模式) EMC组中GPIO IO电源(1.8V模式) |

| NVCC_GPIO | 3 | 3.3 | 3.6 | GPIO IO电源 |

(注:对于A0芯片,DCDC_IN电压域为2.8 V-3.0 V,而对于A1版本及以后的芯片的DCDC_IN,电压域为2.8 V-3.6 V。)

下图列出了其他与RT1050 Power Supply有关的引脚。

| 引脚名称 | 说明 |

|---|---|

| POR_B | 可以产生一个复位信号 |

| ON/OFF | 可以产生一个上电请求信号 |

| TEST_MODE | NXP内部使用,可直接接地 |

| WAKEUP | 可以产生唤醒信号 |

| DCDC_PSWITCH | 内部DCDC供电开关 |

| PMIC_ON_REQ | SNVS上电后产生一个高电平信号 |

3 上电和掉电序列

因为RT1050里面有很多电压源,所以在上电和掉电需要遵循一定的序列(特别是上电)来保证RT1050的正常启动。

下图显示了RT1050的上电和掉电序列。

在对RT1050设计电源时应该严格按照上图显示的上电和掉电序列进行电源设计,下面我们结合NXP的官方DEMO开发板来对这个上电序列进行一个简单的介绍。下图为MIMXRT1050-EVK板子电源设计的结构图(详细原理图大家可以去NXP的官网去获取)。

根据结构图我们可以知道上电过程为:

①当5V输出接入时,SNVS首先通过外部LDO产生的电源先上电

②待SNVS上电稳定后,PMIC_REQ_ON自动置高,使能外部DC/DC电源为其他电源域供电。

③外部DCDC同时输出电源为RC进行充电,这样DCDC_PSWITCH信号则会延迟1ms上电,从而将内部DCDC延迟1ms打开。

④DCDC_OUT输出,为VDD_SOC_IN供电。

⑤ON/OFF按钮用于打开/关闭PMIC_REQ_ON以控制电源模式。

掉电过程我们则是可以通过外部按钮或者看门狗或者普通IO拉低来实现。

(注:对于A0版本芯片,需要用2.8 V-3.0 V电源为SNVS域和DCDC_IN供电,否则片上DCDC模块将无法正常工作。)

4 关于片内DCDC模块

RT1050片内的DCDC模块有效的提高了电源的效率,在使用其过程中我们需要注意一下几点:

- 外部电感的推荐值约为4.7u-10uH,饱和电流大于1A,ESR小于0.2Ohm;

- 外部降压电容值总计约33uF,包括DCDC_OUT和VDD_SOC_IN上使用的所有电容;

- DCDC_PSWITCH相对于DCDC_IN延迟1ms,其目的是等待DCDC_IN稳定,直到DC/DC启动为止;

- 如果不需要使用内部DCDC而是通过外部电源给VDD_SOC_IN上电的话,仍需要为DCDC_IN供电并将DCDC_PSWITCH接地,同时保持DCDC_LP浮空;

- 使DC/DC电流环路尽量小,避免EMI问题;

5 特殊引脚的处理

下面列举了一些特殊引脚的处理:

| 项目 | 建议 |

|---|---|

| BOOT_CFG[11:0] | BOOT_CFG信号是确保功能和运行正常的必备条件,不得浮空。有关正确启动配置的信息,请参阅芯片参考手册中“System Boot”一章。请注意,不正确的设置可能会导致不正确的启动序列。 |

| BOOT_MODE[1:0] | 对于BOOT_MODE1和BOOT_MODE0,使用以下选项之一以实现逻辑0: • 通过任意值的外部电阻连接到GND • 直接连接到GND 实现逻辑1,请使用以下选项之一: • 直接连接到NVCC_GPIO_XX电源 • 通过外部10kΩ电阻连接到NVCC_GPIO_XX电源。 对于高噪声环境,首选值为4.7kΩ。 如果需要开关控制,则不需要使用外部下拉电阻。只需将SPST开关直接连接到NVCC_GPIO_XX电源即可。 |

| BOOT_CFG和BOOT_MODE信号与LCD信号多路复用 | 外围设备可能要求对LCD信号采用一个外部或片上电阻以尽量减少信号浮动。如果使用启动信号会影响外围设备,则要用模拟开关、开路集电极缓冲器或等效器件隔离该路径。 |

| POR_B | 如果使用外部POR_B信号控制处理器POR,则必须在上电时立即拉低POR_B信号,直到VDD_HIGH_CAP和VDD_SNVS_CAP电源稳定为止。在POR_B拉低期间,VDD_SOC_IN可以随时上电,没有特别要求。如果没有外部复位电路的话,则内部POR模块获得控制权。 |

| ON/OFF | 对于便携式应用,ON/OFF输入可以连接到ON/OFF SPST按钮。该管脚有片上消抖功能,此输入有片上上拉电阻。如果未使用,ON/OFF可为无连接。当电流损耗很严重时,可以使用4.7kΩ至10kΩ的串联电阻。 |

| TEST_MODE | TEST_MODE输入内部连接到片上下拉器件。既可将此信号浮空,也可将其连接到GND。 |

| GPANAIO | GPANAIO必须为无连接。 |

| NC引脚 | NC触点为无连接且应浮空。 |

6 RT系列芯片由于电源波动导致芯片卡死的问题

根据目前客户的反馈来说,一般电源状态机在有电源波动的时候容易导致DCDC的状态机锁死,具体原因是因为当出现电源波动时,DCDC_IN的电压在下降到一个阈值(2.6V)会让DCDC关闭,当电压再次恢复到3.3时,这个时候就相当于RT芯片经历一次上电重启,而这种短时间的下电和上电会破坏RT芯片的上电时序,所以会导致RT芯片的DCDC的状态发生错误而锁死。

短时间的下电和上电情况破坏的其实DCDC_PSWICTH的时序,如下图:

DCDC_PSWICTH可以理解成DCDC的开关,或者叫使能引脚,只有当DCDC_PSWICTH为高时,DCDC才打开,开始工作。

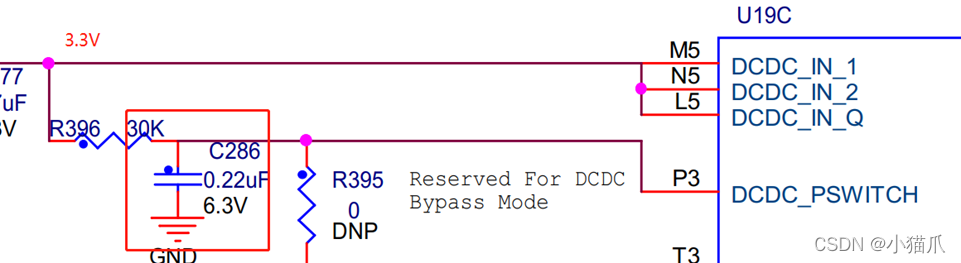

正确的时序应该是,当3.3V接到DCDC_IN时(),由于C286的存在,3.3V会给C286充电,导致的结果就是DCDC_PSWICTH拉高的时间会比DCDC_IN延迟2ms左右,这样做的目的是确保DCDC_IN处的实际输入电压达到3.3V稳态,再使能DCDC模块让其工作。

而短时间的下电和上电,因为这两者间隔时间太短,所以在第二阶段上电过程,C286没有来得及放电导致DCDC_PSWITCH的电压为高,而这个时候就会导致DCDC_IN的实际输入电压还没达到DCDC的正常工作电压范围内就提前使能了DCDC模块,这个时候DCDC的状态机就会锁死。

而为了解决这个问题,唯一的做法就是在每一次上电前,都必须保证DCDC_PSWITCH处的电压在0.5V以下,所以在每一次下电后都需要让C286快速放电至0V或者快速将DCDC_PSWITCH拉低到0V。我们一般推荐的做法都是可以加一个三极管或者加一个电压监控芯片来达到这个效果。

END

本文档详细介绍了i.MXRT1050微控制器的电源设计,包括与电源相关的引脚说明、上电和掉电序列、片内DCDC模块的使用注意事项,以及解决因电源波动导致芯片卡死的方法。

本文档详细介绍了i.MXRT1050微控制器的电源设计,包括与电源相关的引脚说明、上电和掉电序列、片内DCDC模块的使用注意事项,以及解决因电源波动导致芯片卡死的方法。

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?