一封深夜短信

——凌晨2点,技术部张经理收到一封邮件:

【DeepSeek安全中心】

检测到您的账号在境外异常登录,请立即处理。

他下意识点开链接,页面与官网几乎一致——动态LOGO、公司标语、甚至底部备案号都分毫不差,输入账号、密码、验证码——直到页面跳转回官网,才惊觉自己刚刚亲手交出了核心数据库的钥匙。”

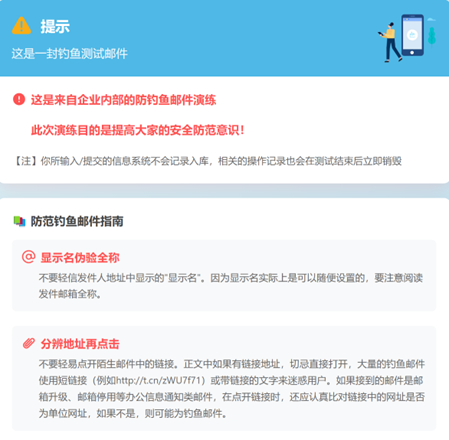

这不是电影情节,而是一场真实的钓鱼攻防演练。

当攻击者用“1:1复刻”的页面、紧迫话术和心理操控发起进攻时,90%的安全防线往往从“人”的疏忽开始崩塌。

1、 为什么“高智商”团队也会中招?

我们近期观察到一种新型钓鱼模式:利用企业对DeepSeek等工具的强依赖性,伪造“账号风险”实施精准诈骗。

攻击者的三大“隐形武器”:

场景真实化:从短信模板到登录页面,域名、LOGO、排版与官方几乎无差异;

情绪操控:用“账号冻结”“数据丢失”等关键词制造恐慌,阻断理性思考;

痕迹隐匿:输入信息后自动跳转真实官网,受害者甚至无法察觉已被盗号。

而更值得警惕的是:

许多员工会因“页面太逼真”而放松警惕;

大部分的人从未检查过链接域名后缀(如“.com”与“.net”的差异)。

防御漏洞,或许正藏在“我以为”里 当攻击者用“真实感”麻痹警惕性,传统培训的漏洞暴露无遗。

2、 如何让安全意识成为“肌肉记忆”?

面对不断进化的钓鱼攻击,实战经验比理论更重要。如何实战?与其等待黑客侵入,不如自行演练,摸排可能的风险。工欲善其事,必先利其器。易念科技的钓鱼演练平台应时而出,它能够

还原真实场景:覆盖短信、邮件、即时通讯工具,内置“DeepSeek异常登录”“会议链接诈骗”等160+高频钓鱼模板;每天演练不重样。

实时感知风险:员工点击链接、输入敏感信息的瞬间,系统自动预警并生成行为热力图;后台数据精准定位每个“粗心”的人。

闭环教育机制:对高风险员工自动触发定制化课程,从“哪里跌倒”就在“哪里学习”;进一步提升员工安全防范意识。

量化安全水位:一键导出团队安全意识评分、漏洞分布、改进进度报告,让管理有据可依,让汇报1分钟搞定。

现在,你面临两个选择

A 继续依赖“听课+考试”,等待某天员工在真实攻击中失误;

B 用一套经过150+头部企业,500多万名员工验证的工具,把钓鱼攻击关进“演练沙盒”。

如果选择后者,可立即锁定一项限时权益:

详细了解钓鱼演练内容,欢迎试用易念科技E-Phishing™钓鱼演练平台

加群注册免费版账户,可免费获得10个员工管理权限、160+标准模板、AI模板生产调用权限, 一个月使用期,期间发送次数不限。更有企业网络钓鱼防范素材分享~

上海易念信息科技有限公司(易念科技)是成立于2012年的网络安全意识教育企业,在组织开展国家网络安全周宣传教育工作基础上,完成教育内容标准化、教育方式平台化、运营服务体系化;公司秉承教育改变认知,意识决定安全的核心理念,致力于“打造网络空间安全人脑防火墙”。已为央企、外企、金融、能源、医疗、互联网、公用事业、先进制造等200+单位提供了优质的安全意识教育内容、平台与专业服务,累计受众500多万名员工。

3551

3551

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?