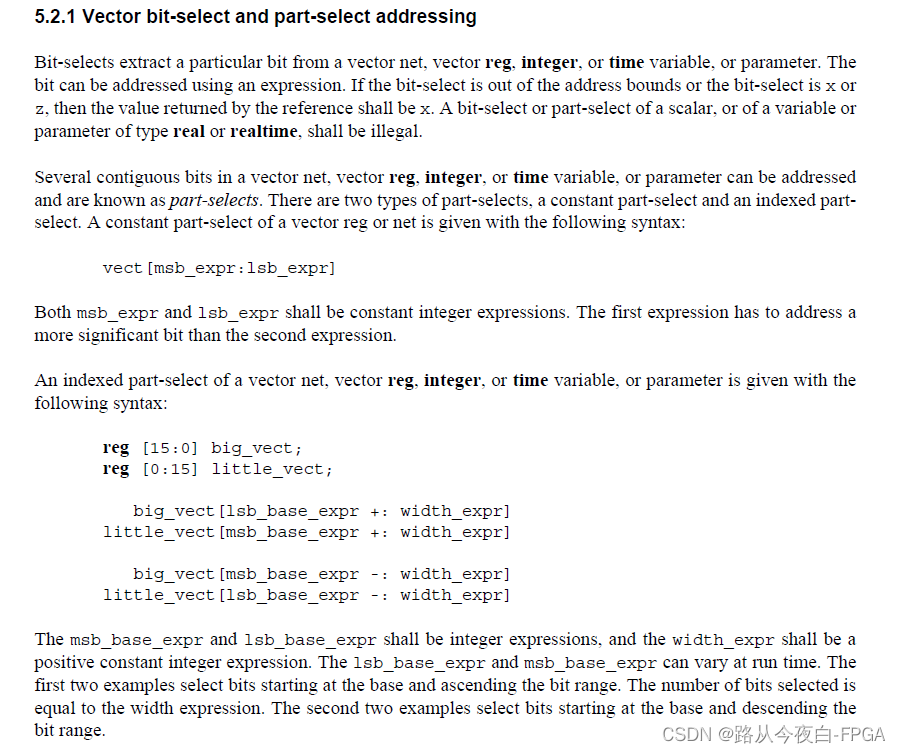

如图,IEEE Verilog标准中这样描述!

parameter width = 4;

reg [15:0] big_vect; //大端

reg [0:15] little_vect; //小端

reg [2:0] start;

wire [3:0] a,b,c,d;

initial begin

big_vect = 16'b1010_1100_1011_1111;

little_vect = 16'b1010_1100_1011_1111;

start = 3'b111;

end

assign a = big_vect[start+:width];

assign b = big_vect[start-:width];

assign c = little_vect [start+:width];

assign d = little_vect [start-:width];其中start为变量,可进行操作,width为常数。

a = 'b1001;

b = 'b1011;

c = 'b0101;

d = 'b0011;注意 +: 表示升序,-:表示降序,但也要注意被截取信号的定义方式!

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?