riscv 32单周期处理器cpu,工程基于vivado,指令集rv32i,systemverilog编写,结构简单,指令存在ram中,可仿真,代码结构清晰,适合初学者学习,并赠送包括riscv中文手册和riscv指令集文档的中文版本

因工程文档

ID:34100630808886065

云赐记

RISC-V是一个开源的指令集架构,近年来在处理器设计领域引起了广泛关注。本文将介绍一个基于RISC-V 32位单周期处理器CPU的工程,该工程使用Vivado进行设计开发。该处理器的指令集采用RV32I,使用SystemVerilog语言编写。整个处理器的结构简单,适用于初学者学习和理解处理器设计的基本原理。

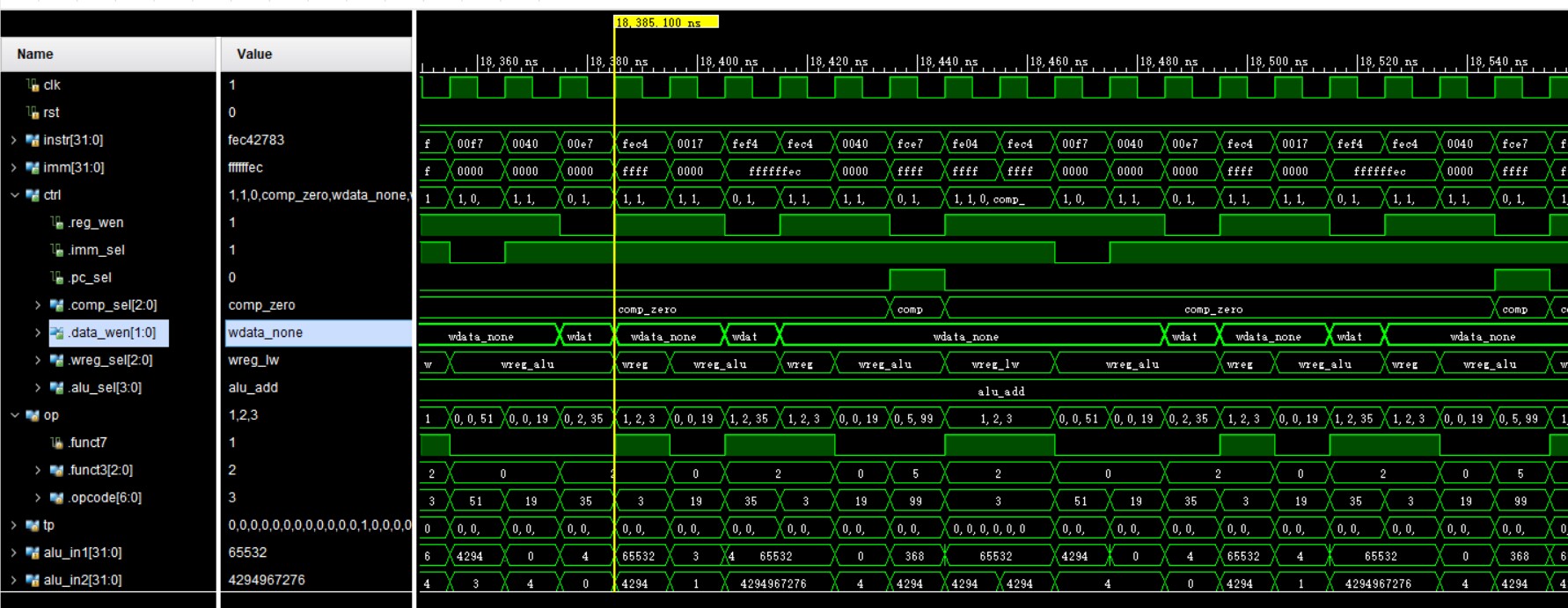

工程中的指令以RAM的形式存储,这样可以方便进行仿真和测试。通过这个工程,初学者可以通过仿真和调试来逐步理解处理器的工作原理。本文将详细介绍该处理器的设计思路,包括数据通路和控制单元的设计、指令解码和执行过程、寄存器的读写以及存储器的操作等。

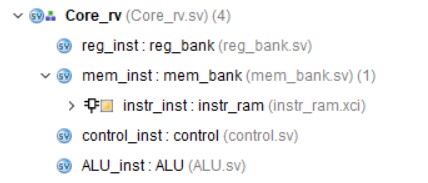

在工程的设计过程中,开发者需要清晰地规划处理器的数据通路,包括寄存器、ALU、控制单元等组件的连接和交互。通过建立合适的信号传输路径,确保数据在处理器中的正确流动,从而实现指令的正确执行。本文将详细介绍数据通路的设计与实现,并通过时序图和状态转换图展示其工作过程。

除数据通路外,控制单元也是处理器设计中不可或缺的部分。本文将介绍控制单元如何解析指令,提取需要的操作码和操作数,并通过适当的控制信号来控制数据通路中各个组件的工作。同时,我们还将探讨如何处理异常和中断,并设计相应的处理方法。

在工程的编码结构方面,本文将提供一个清晰的目录结构,以便初学者快速理解和定位所需的文件。同时,我们还将介绍一些常用的编码规范和技巧,以帮助读者编写出结构清晰、易于阅读和维护的代码。

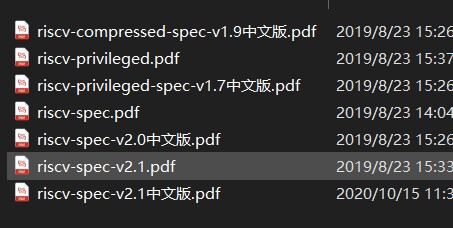

为了更好地辅助初学者学习和使用该处理器,我们还将附赠一份RISC-V中文手册和RISC-V指令集文档的中文版本。这些文档包含了RISC-V指令集的详细说明和使用示例,以及对应的中文翻译。读者可以通过这些文档更深入地了解RISC-V指令集的各种特性和用法。

总之,本工程提供了一个简单易懂的RISC-V 32位单周期处理器CPU设计,适合初学者进行学习和实践。通过对该工程的学习,读者可以掌握处理器设计的基本原理和方法,并深入理解RISC-V指令集的各种特性和用法。同时,附赠的中文手册和指令集文档将进一步帮助读者更好地使用和应用RISC-V技术。希望本文对读者在处理器设计和RISC-V学习方面提供帮助和指导。

(以上为机器生成的文章开头,仅供参考)

以上相关代码,程序地址:http://matup.cn/630808886065.html

本文详细介绍了一款基于RISC-V32指令集的简单处理器设计,使用Vivado工具,适合初学者。内容涵盖指令集、结构、仿真、数据通路和控制单元设计,附赠中文手册和文档资源。

本文详细介绍了一款基于RISC-V32指令集的简单处理器设计,使用Vivado工具,适合初学者。内容涵盖指令集、结构、仿真、数据通路和控制单元设计,附赠中文手册和文档资源。

636

636

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?