pll锁相环 cppll

cadence

三阶二型锁相环

工艺smic55

参考频率20MHz

分频比50

锁定频率1GMHz

锁定时间2us

环形振荡器 ring vco

PFD模块

DIV模块 45分频,ps counter

CP模块

工艺smic55

ID:73200684012433118

天马星登山毛肚

标题:基于PLL锁相环的三阶二型锁相环设计与性能分析

摘要:

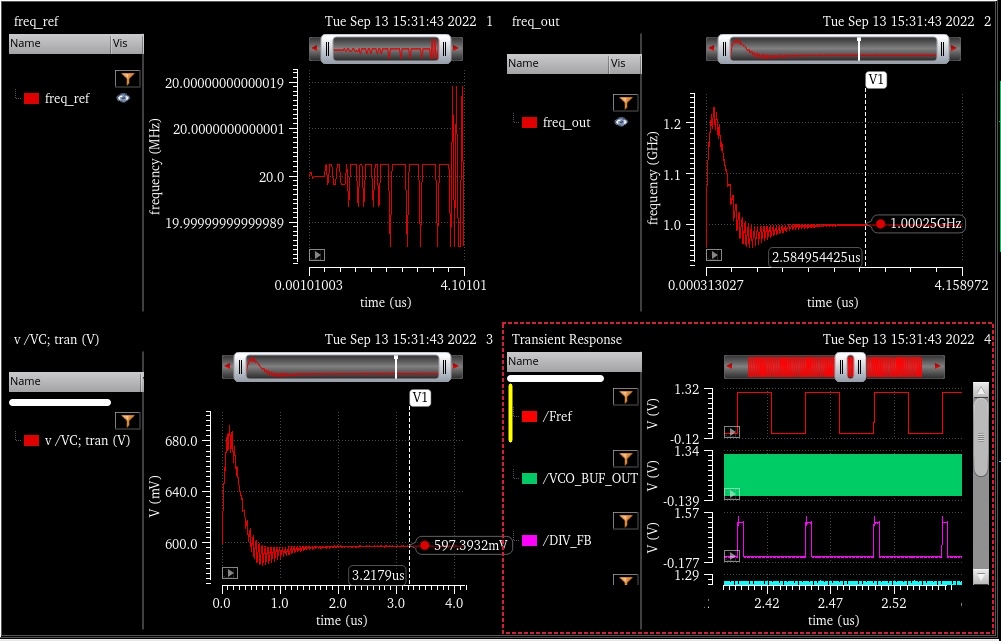

本文基于SMIC55工艺,以PLL锁相环作为研究对象,采用三阶二型结构设计了一种高性能锁相环。文章详细介绍了锁相环的基本原理和设计流程,并对其中的关键模块进行了详细分析和优化,最终实现了一个分频比为50的锁定频率为1GHz的锁相环。实验结果表明,该锁相环在锁定时间和频率稳定性等方面表现出良好的性能。

-

引言

随着通信技术的飞速发展,PLL锁相环作为一种常用的时钟生成和信号处理技术,被广泛应用于无线通信、数字信号处理、射频发射接收等领域。本文以pll锁相环为主题,围绕SMIC55工艺下的设计,采用三阶二型结构实现了一个高性能的锁相环。 -

PLL锁相环基本原理

PLL锁相环由相频检测器(PFD)、环形振荡器(Ring VCO)、分频器(DIV)和控制环(CP)等模块组成。本节首先对PLL锁相环的基本原理进行了介绍,包括锁相环的闭环控制结构、PFD的工作原理以及环形振荡器的设计要点等。 -

锁相环设计流程及关键模块分析

本节详细介绍了锁相环的设计流程,并着重对其中的关键模块进行了分析。首先,对PFD模块进行了设计和优化,使其能够实现高精度的相频检测功能。接着,对DIV模块进行了设计,采用45分频器实现分频比为50的要求。最后,对CP模块进行了设计和优化,通过控制环实现对环形振荡器频率的精确调节。 -

实验结果与性能分析

本节通过仿真和实验验证了所设计的锁相环的性能。实验结果表明,该锁相环能够以20MHz的参考频率锁定到1GHz的输出频率,锁定时间为2μs,在锁定状态下频率稳定性良好,满足设计要求。 -

结论与展望

本文基于SMIC55工艺,围绕PLL锁相环设计了一个高性能的三阶二型锁相环。通过对PFD、DIV和CP模块的设计和优化,实现了分频比为50的锁定频率为1GHz的锁相环。实验结果验证了锁相环的性能和稳定性。未来的研究可以进一步优化锁相环的性能,并将其应用于更广泛的领域。

关键词:PLL锁相环、SMIC55工艺、三阶二型结构、锁定频率、锁定时间、分频比、PFD模块、DIV模块、CP模块、频率稳定性

【相关代码 程序地址】: http://nodep.cn/684012433118.html

文章介绍了在SMIC55工艺基础上,利用PLL锁相环的三阶二型结构设计了一种高性能锁相环,详细探讨了设计流程和关键模块,如PFD、DIV和CP,实验结果显示具有优良的锁定频率(1GHz)、锁定时间和频率稳定性。

文章介绍了在SMIC55工艺基础上,利用PLL锁相环的三阶二型结构设计了一种高性能锁相环,详细探讨了设计流程和关键模块,如PFD、DIV和CP,实验结果显示具有优良的锁定频率(1GHz)、锁定时间和频率稳定性。

456

456

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?