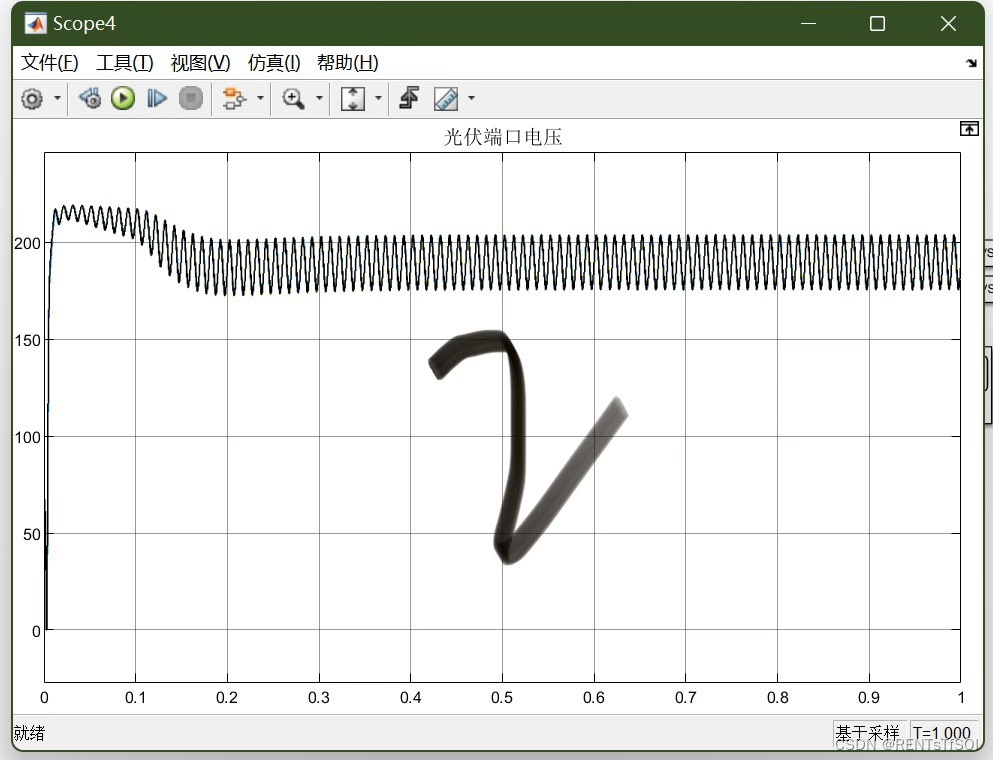

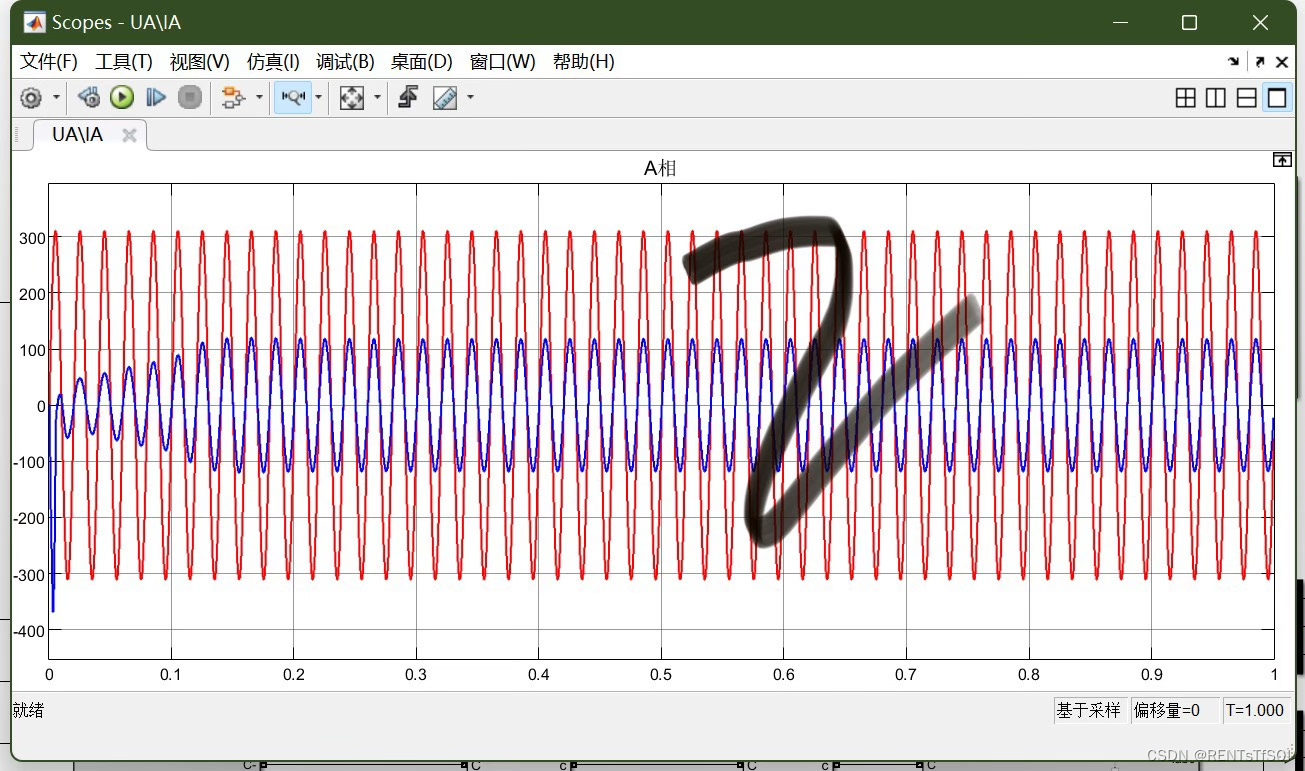

多电平级联H桥_三相级联H桥逆变器光伏并网系统

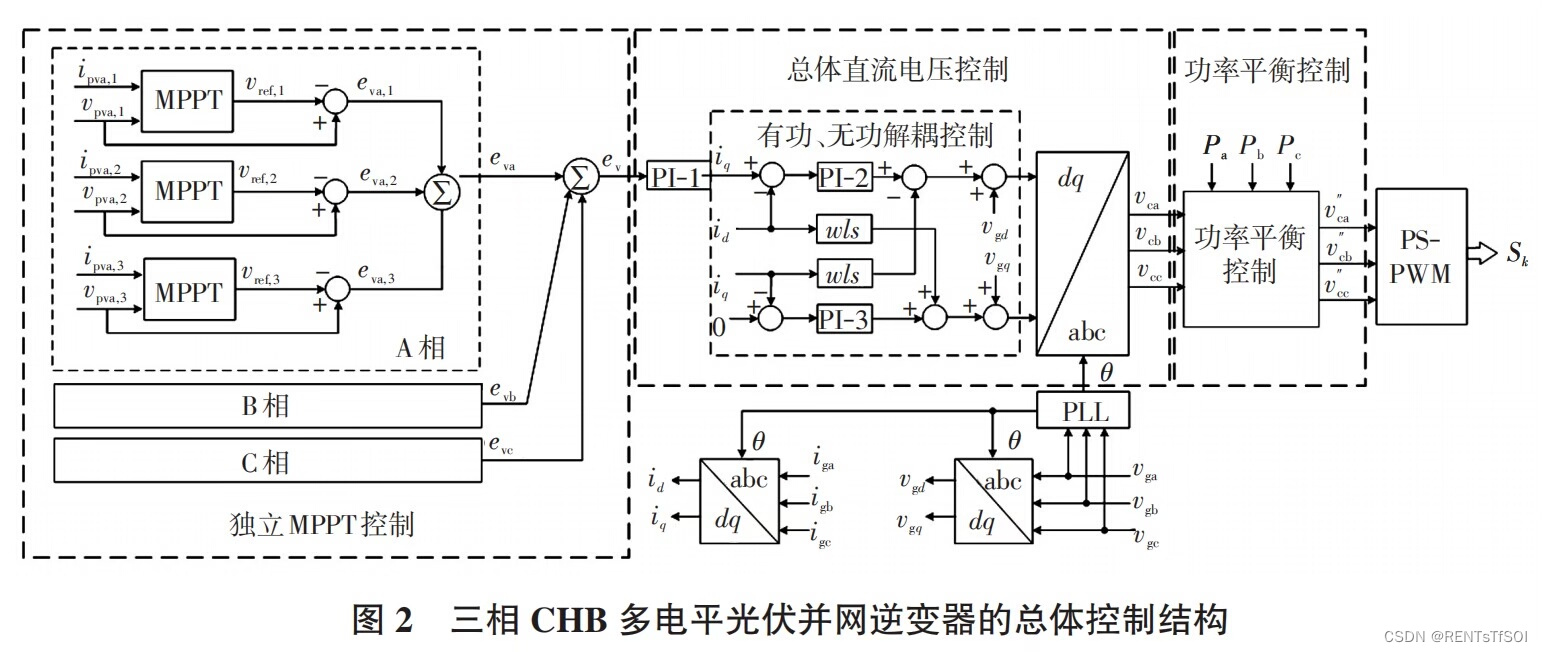

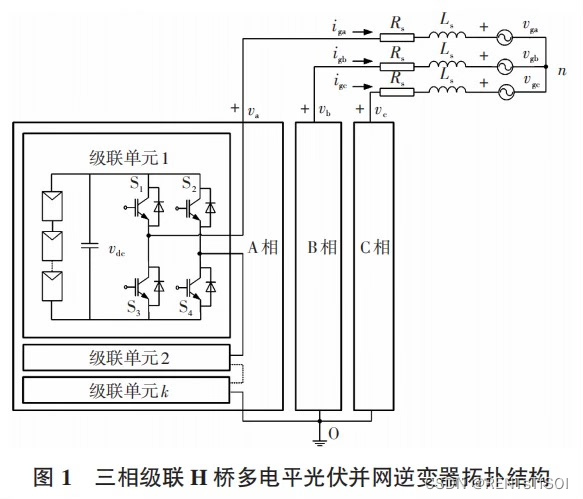

控制如下图所示。

控制主要包含:载波移相调制,MPPT,电压电流双闭环。

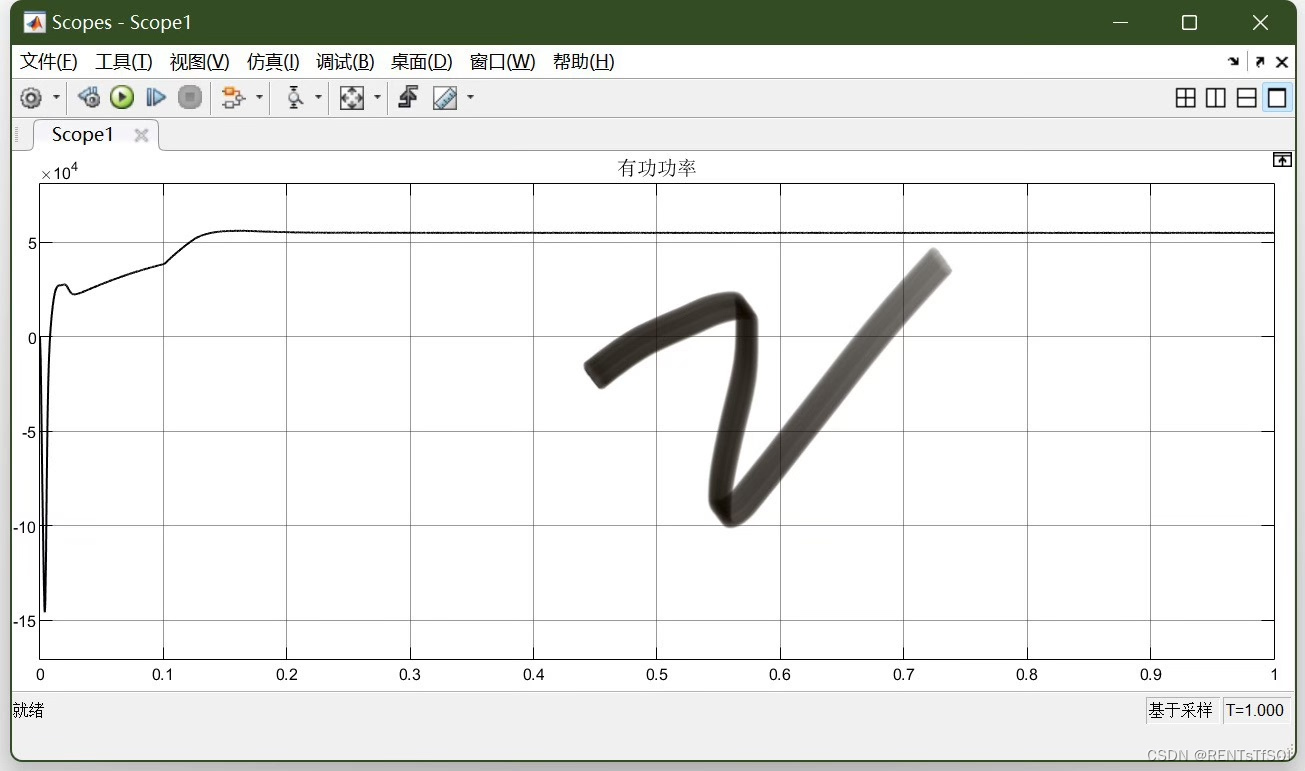

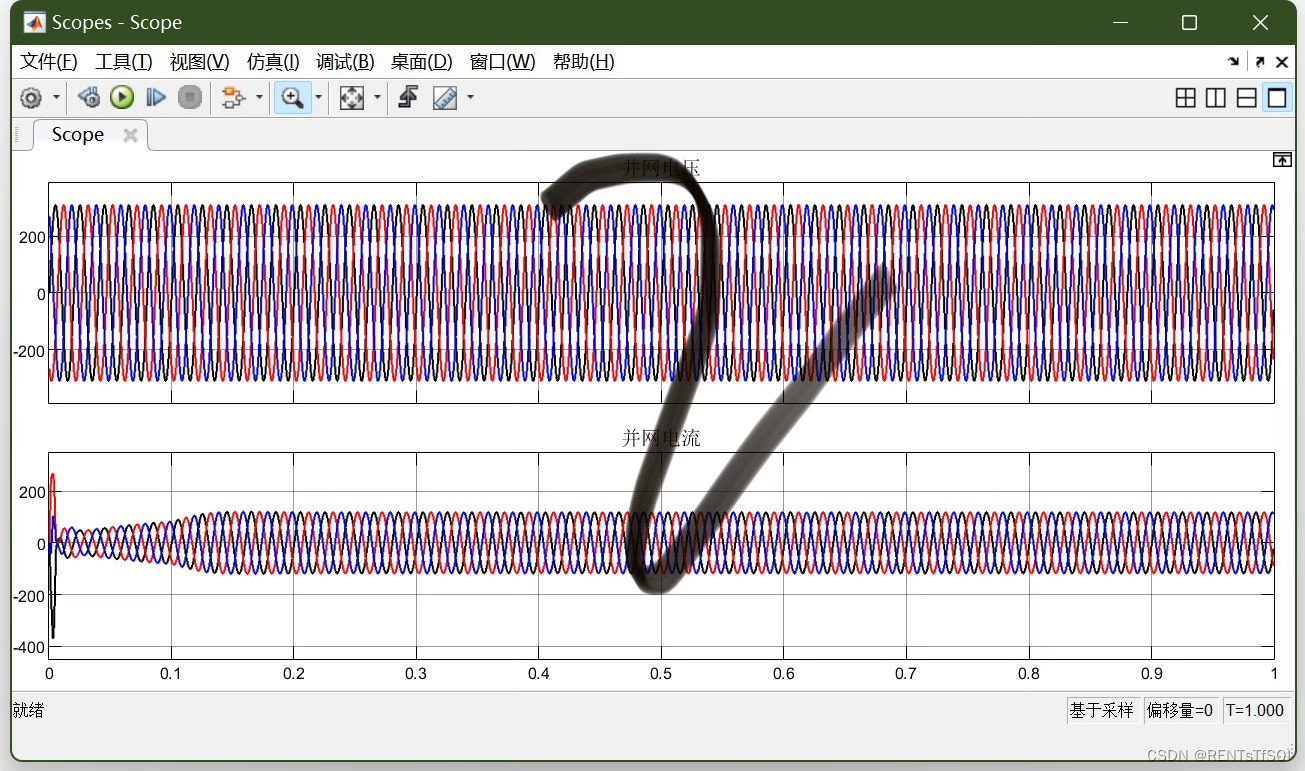

波形如图所示,波形完美系统动态特性良好。

有参考文献

Matlab为2021b。

基于纯Verilog FPGA的双线性差值视频缩放技术

摘要:本文介绍了一种基于纯Verilog FPGA的双线性差值视频缩放技术,该技术可实现PC端HDMI输入视频的缩小或放大,并通过HDMI输出显示。本文详细介绍了双线性差值算法的原理和实现方式,以及在FPGA平台上的硬件设计和移植方法。通过手写RAM和FIFO代码,该技术可以轻松地移植到其他平台上实现视频缩放功能。

1. 引言

随着高清视频的普及,视频缩放技术在实际应用中起到了重要的作用。双线性差值是一种常用的图像缩放算法,其原理是通过对原始图像的像素进行插值计算,从而实现图像的放大或缩小。本文将介绍如何在基于纯Verilog FPGA的硬件平台上实现双线性差值视频缩放技术,并提供了硬件设计和移植方法。

2. 双线性差值算法原理

双线性差值算法是一种基于像素级插值的图像缩放算法。其原理是根据原始图像中的四个最近像素点的灰度值和与目标图像像素点位置相关的权重值进行加权平均计算,从而得到目标图像中像素点的灰度值。具体而言,对于目标图像中的每个像素点P,通过以下公式计算其灰度值:

P = w1 * A + w2 * B + w3 * C + w4 * D

其中A、B、C和D分别表示原始图像中的四个最近像素点的灰度值,w1、w2、w3和w4为与目标图像像素点位置相关的权重值。通过将原始图像中的像素点与目标图像中的像素点一一对应,即可实现图像的缩放功能。

3. 硬件设计和移植方法

为了在FPGA平台上实现双线性差值视频缩放技术,需要进行硬件设计和移植。首先,根据双线性差值算法的原理,设计缩放模块,其中包含DDR IP、RAM和FIFO代码。DDR IP用于存储原始图像和目标图像的像素数据,RAM用于存储原始图像中的四个最近像素点的灰度值,FIFO用于实现数据的输入和输出。

在硬件设计中,需要考虑到FPGA平台的资源限制和性能要求。根据具体平台的技术规格,合理分配资源和配置参数,以保证缩放模块的性能和稳定性。同时,还需要利用EDA平台(如efinity)进行逻辑综合、布局布线和时序优化,以确保硬件设计的正确性和可靠性。

在移植过程中,需要根据目标平台的硬件规格和编程环境,对硬件设计进行相应的调整和修改。根据易灵思ti60f225平台的特点,可以进行IP核的替换和时序调整,以适应目标平台的要求。通过合理的移植方法,可以较为轻松地将双线性差值视频缩放技术移植到其他平台上。

4. 实验结果与讨论

为了验证双线性差值视频缩放技术的有效性和性能,进行了一系列实验。实验结果显示,基于纯Verilog FPGA的双线性差值视频缩放技术能够实现PC端HDMI输入视频的缩小或放大,并通过HDMI输出显示。通过对不同分辨率和比例的视频进行缩放,可以得到清晰、流畅的图像效果。实验还表明,该技术在易灵思ti60f225平台上的性能稳定和资源利用率较高。

5. 结论

本文介绍了一种基于纯Verilog FPGA的双线性差值视频缩放技术,该技术通过双线性差值算法实现了PC端HDMI输入视频的缩小或放大,并且可通过HDMI输出显示。在易灵思ti60f225平台上进行了硬件设计和移植,通过手写RAM和FIFO代码,实现了轻松地移植到其他平台的可能。实验结果验证了该技术的有效性和性能,为实际应用提供了一种可行的解决方案。

关键词:双线性差值、视频缩放、Verilog FPGA、HDMI、DDR IP、RAM、FIFO、易灵思ti60f225、efinity

相关代码,程序地址:http://imgcs.cn/lanzoun/750989751928.html

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?