Our implementation of SEQ consists of

包含了:

combinational logic and

two forms of memory devices :

clocked registers (the program counter and condition code register),

and random-access memories (the register file, the instruction memory, and the data memory).

We are left with just four hardware units that require an explicit control over their sequencing—

四个需要时序控制的模块,也称之为 state element

the program counter,

the condition code register,

the data memory,

and the register file.

下图

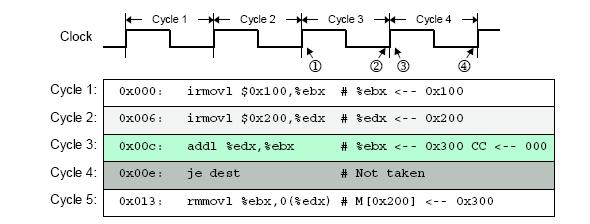

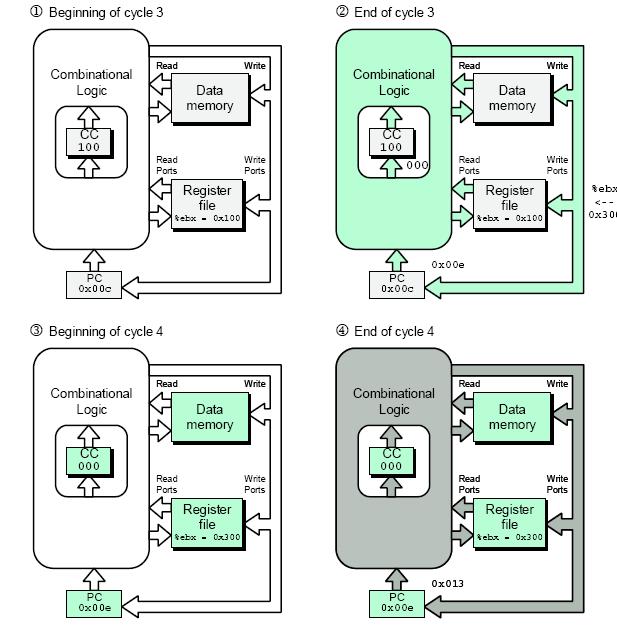

Figure 23 shows how the SEQ hardware would process the instructions at lines 3 and 4 in the following

code sequence, shown in assembly code with the instruction addresses listed on the left:

1 0x000: irmovl $0x100,%ebx # %ebx <-- 0x100

2 0x006: irmovl $0x200,%edx # %edx <-- 0x200

3 0x00c: addl %edx,%ebx # %ebx <-- 0x300 CC <-- 000

4 0x00e: je dest # Not taken

5 0x013: rmmovl %ebx,0(%edx) # M[0x200] <-- 0x300

6 0x019: dest: halt

理解的部分就是说

state element的四个部件,在时钟的上升沿发生改变

其他的组合逻辑,在时钟周期内发生变化。

5009

5009

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?