概叙

科普文:软件架构Linux系列之【从硬件角度了解内存DRAM和DDR5】_dram density和容量-CSDN博客

科普文:软件架构Linux系列之【并发问题的根源:CPU缓存模型详解】-CSDN博客

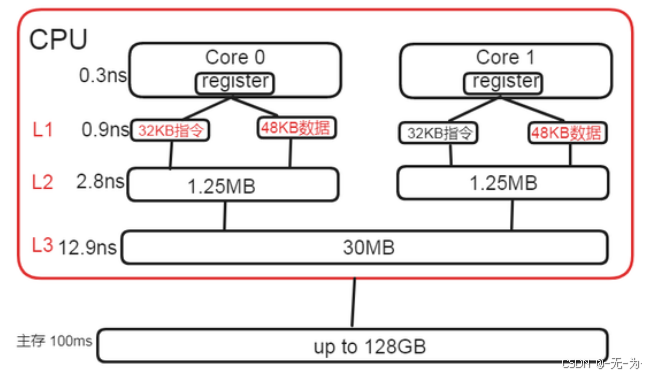

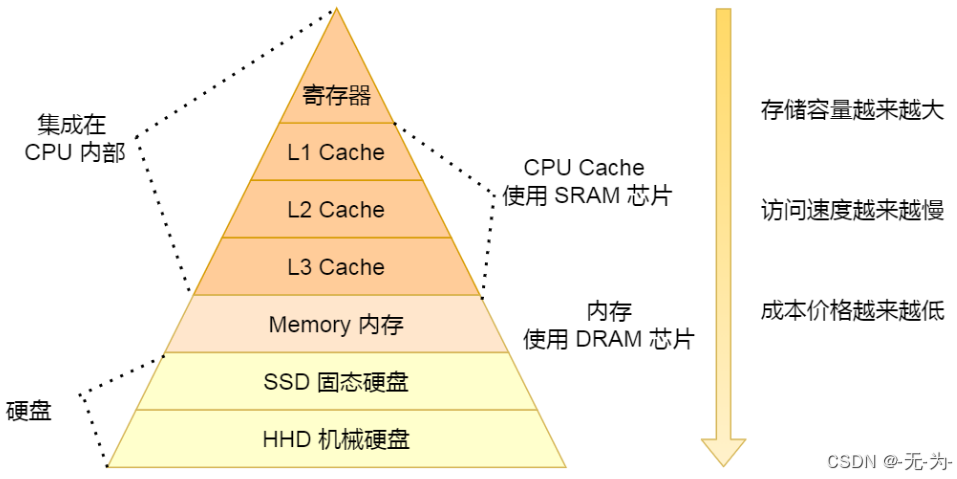

前面提到并发问题的根源就是cpu太快,计算机其他模块远远跟不上cpu的速度。所以就有了cpu的三级缓存,这也导致了cpu和内存的数据一致性问题。

为了让cpu缓存更多的指令和数据,AMD EPYC 霄龙处理器:引入3D缓存,直接将三级缓存容量扩展到1152MB!

正好,我们来看看Zen微架构CPU锐龙和霄龙。

Zen架构

Zen架构是AMD开发的一种微处理器架构,首次推出于2017年,标志着AMD在高性能处理器市场的强势回归。

该架构基于14nm工艺制造,引入了全新的“[Ryzen”品牌,旗下的锐龙7 1800X和锐龙5 1600X在消费市场上取得了成功,而基于Zen架构的EPYC处理器也开始在服务器市场上获得青睐。

Zen架构的推出带来了显著的性能提升,每个时钟周期的指令集提高了40%,现代化的设计和多线程技术使其能够与英特尔的产品竞争。在此基础上,AMD不断进行优化和改进,推出了Zen+和Zen 2架构,分别在2018年和2019年发布。Zen+采用了12nm工艺,进一步优化了功耗和频率,而Zen 2则采用了7nm工艺,带来了更高的性能和更低的功耗。

Zen架构的应用领域广泛,不仅在消费市场上表现出色,还在服务器市场上获得了认可。其高吞吐量的同步多线程技术和对DDR4的兼容性,使得Zen架构的处理器能够提供优异的性能和能效。

此外,Zen架构的处理器支持PCIe Gen 3、USB 3.1 Gen2 10Gbps、NVMe和SATA Express等技术,进一步提升了平台的扩展性和兼容性。

Zen架构优点

性能

“Zen”架构是一种可持续改进的可扩展架构:核心引擎支持多线程并行处理以高效运行面向未来的工作负载;出色的高速缓存系统和神经网络预测能够有效实现更低的延迟;注重能效打造出色的性能功耗比。

可扩展性

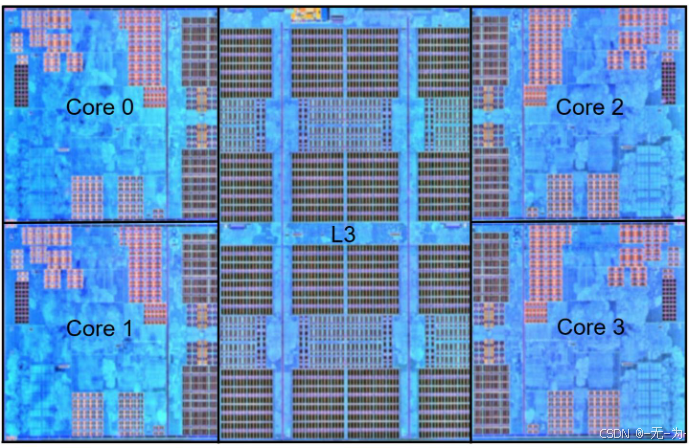

AMD 在 x86 处理器中大胆采用全新的小芯片设计。AMD 没有选择使用大型单片式芯片,而是采用了称为小芯片的处理器构建块。每个小芯片都包含许多基于“Zen”的核心,而且封装的小芯片越多,处理器性能就越强。

效率

AMD 致力于不断优化核心设计。将核心和 I/O 开发流程区分开来有助于缩小 CPU 芯片,并针对多种情况优化性能或能效。从处理器到平台,每个晶体管的放置以及每微瓦功率的分配无不彰显了 AMD 对提升能效的承诺。

Zen架构CPU

Ryzen锐龙

EPYC霄龙

AMD Zen架构进化:从Zen 1到Zen 5的辉煌历程

AMD是来自美国加州的超微半导体品牌。AMD专门为计算机、通信和消费电子行业设计和制造各种创新的微处理器(CPU、GPU、APU、主板芯片组、电视卡芯片等),以及提供闪存和低功率处理器解决方案。

Zen架构在过去十几年间已经经历了多次迭代和进化。起初,Zen架构的诞生是为了扭转AMD当时在高性能处理器市场上的劣势。在经历了前几代架构的挫折之后,Zen的推出无疑是AMD的一次重大技术突破。自Zen 1发布以来,AMD的市场占有率和技术成熟度不断提升,逐步成为Intel在处理器市场上的强大竞争对手。

Zen 1:重塑AMD形象的开端

Zen 1于2017年正式发布,以其全新的Microarchitecture赢得了市场的广泛关注。

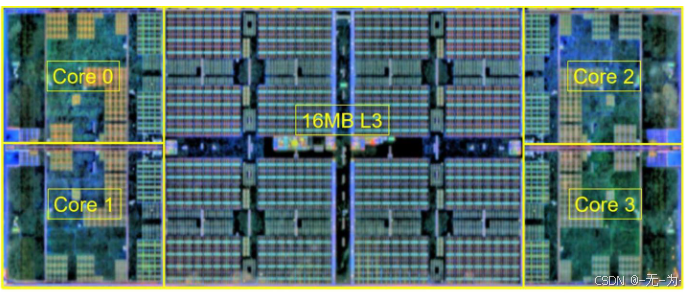

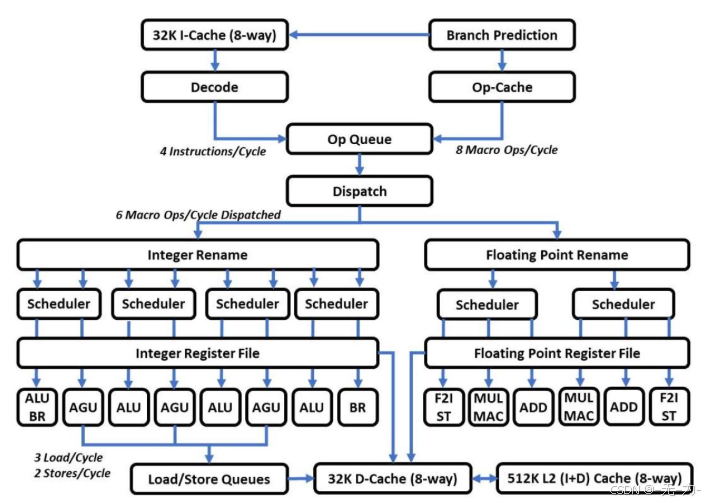

AMD 的下一代高性能 x86 核心代号为“Zen”,面向服务器、桌面和移动客户端应用程序。采用 Global Foundries 的节能 14nm LPP FinFET 工艺,44mm² Zen 核心复合单元 (CCX) 具有 1.4B 晶体管,并包含共享的 8MB L3 缓存和四个核心。7mm² Zen 内核包含专用的 0.5MB L2 缓存、32KB L1 数据缓存和 64KB L1 指令缓存。每个内核都有一个数字低压差 (LDO) 稳压器和数字频率合成器 (DFS),可在不同电源状态下独立改变频率和电压。

Zen 1架构凸显了AMD在多核处理能力上的优越性,在全面提高指令执行效率的同时,显著降低了功耗。这使得一些高负载场景如科学计算、3D渲染和游戏等应用场景下,AMD处理器有了更加出色的表现。

与此前的Bulldozer架构相比,Zen 1在分支预测器、指令解码器、整数和浮点单元等核心技术上都进行了重大提升,使得单核心性能显著增强。

在市场反响上,Zen 1助力AMD实现了重新崛起,成功地吸引了一大批发烧友和专业用户的关注。

Zen 2:跨时代的性能飞跃

Zen 2于2019年发布,是基于Zen 1架构的重大改进版本。

AMD 下一代高效核心代号为“Zen 2”,采用 x86-64 设计,采用节能的台积电 7nm FinFET 工艺制造。与 AMD 的上一代核心(代号为“Zen”[1])类似,该版本中具有 4 个核心的核心复合单元(CCX)广泛用于客户端、半定制、嵌入式和 服务器细分市场。475M 晶体管核心片尺寸为 7.83mm2,具有 0.5MB 二级缓存和 4MB 共享三级缓存。该设计采用新的定制电路和存储器设计技术来实现指定的性能和功耗。

Zen 2采用了7nm工艺技术,使得晶体管密度和能效比大幅度提升。

这一系列改进不仅使Zen 2在能效方面大幅领先,还提升了整体计算能力。更为重要的是,Zen 2引入了chiplet设计,使得芯片设计更加灵活和可扩展。

通过这种设计,AMD可以在一个处理器中集成更多的核心,从而提高多线程处理性能。

Zen 2还支持PCIe 4.0接口,进一步增强了数据传输速率,使得高性能计算和存储应用的性能得到极大提升。

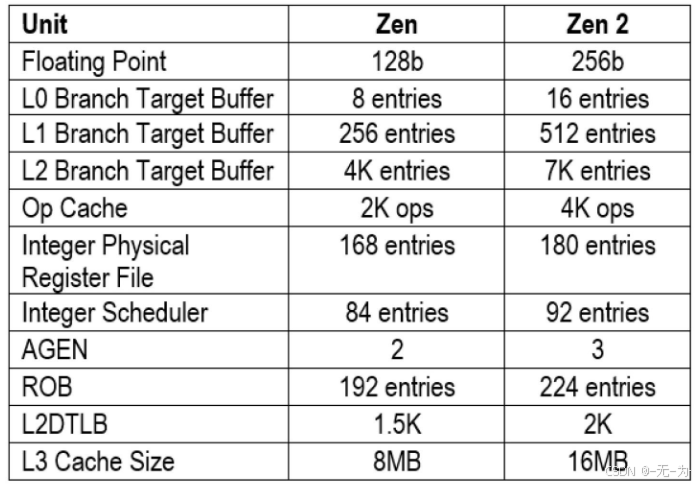

Zen 2 设计比 Zen1有许多设计改进,包括平均单线程应用程序的每周期指令 (IPC) 提高 15%,同时降低技术中立的每周期开关电容( CAC)9%。前端采用新的分支预测方法,分支目标容量增加近一倍。整数物理寄存器文件将其条目从 168 个增加到 180 个。地址生成单元可以调度 3 个存储 AGEN,而 Zen 上只能调度 2 个。整数调度器从 84 个条目增加到 92 个条目,并且退出重新排序缓冲区从 192 个条目增加到 224 个条目。这些架构增强在各种工作负载上产生了有意义的 IPC 改进,而不会导致动态功耗成比例增加,从而带来更好的性能功耗比。

Zen 3:全面优化与新高度

Zen 3架构于2020年发布,再次为AMD带来了市场的好评。Zen 3在架构上进行了重新设计,以进一步提高性能和能效比。

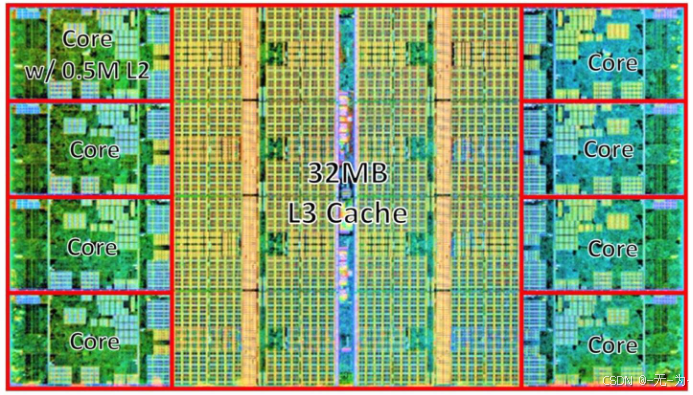

“Zen 3”是 AMD Zen 系列微处理器中首次重大微架构重新设计。鉴于与上一代“Zen 2”核心[1]相同的7纳米工艺技术以及相同的平台基础设施,“Zen 3”的主要设计目标是提供:1) 每周期指令 (IPC) 显着提升,2) 频率显着提升,3) 电源效率持续提高。核心复合体单元(CCX)由 8 个“Zen 3”核心组成,每个核心具有 0.5MB 私有 L2 缓存和 32MB 共享 L3 缓存。除了 IPC 和频率改进之外,在上一代中增加 4 核和 16MB L3 还可以提供额外的性能提升。“Zen 3”CCX 包含 68mm2 的 4.08B 晶体管,广泛应用于客户端、服务器和嵌入式细分市场。

据AMD官方数据,Zen 3架构的每时钟周期指令数(IPC)较Zen 2显著提升了19%。相比之前的架构,Zen 3在游戏性能和高负载工作环境中表现尤为突出。

Zen 3采用共同缓存设计,不再区分单个核心的专用缓存,所有核心共享L3缓存,这大幅提高了缓存命中率和数据存取速度。

借助这一系列改进,Zen 3迅速成为了高性能处理器市场中的佼佼者。

存储管道。重排序缓冲区增加了32个条目,达到256个,而在浮点单元中,问题宽度从4个增加到6个,FMAC延迟从5个减少到4个周期。在负载-存储单元中,最大负载带宽和存储带宽分别增加了1到3和2,并且通过增加4个表漫步器增强了翻译暂存缓冲区(TLB),使其总数达到6个。总体而言,在25个单线程行业基准测试和游戏应用程序中,“Zen 3”内核比“Zen 2”提供了+19%的平均IPC提升,一些游戏的表现超过了+30%[2]。

Zen 4:继续进化中的新里程

在Zen 3的基础上,2022年发布的Zen 4架构进一步提升了AMD在CPU市场的竞争力。

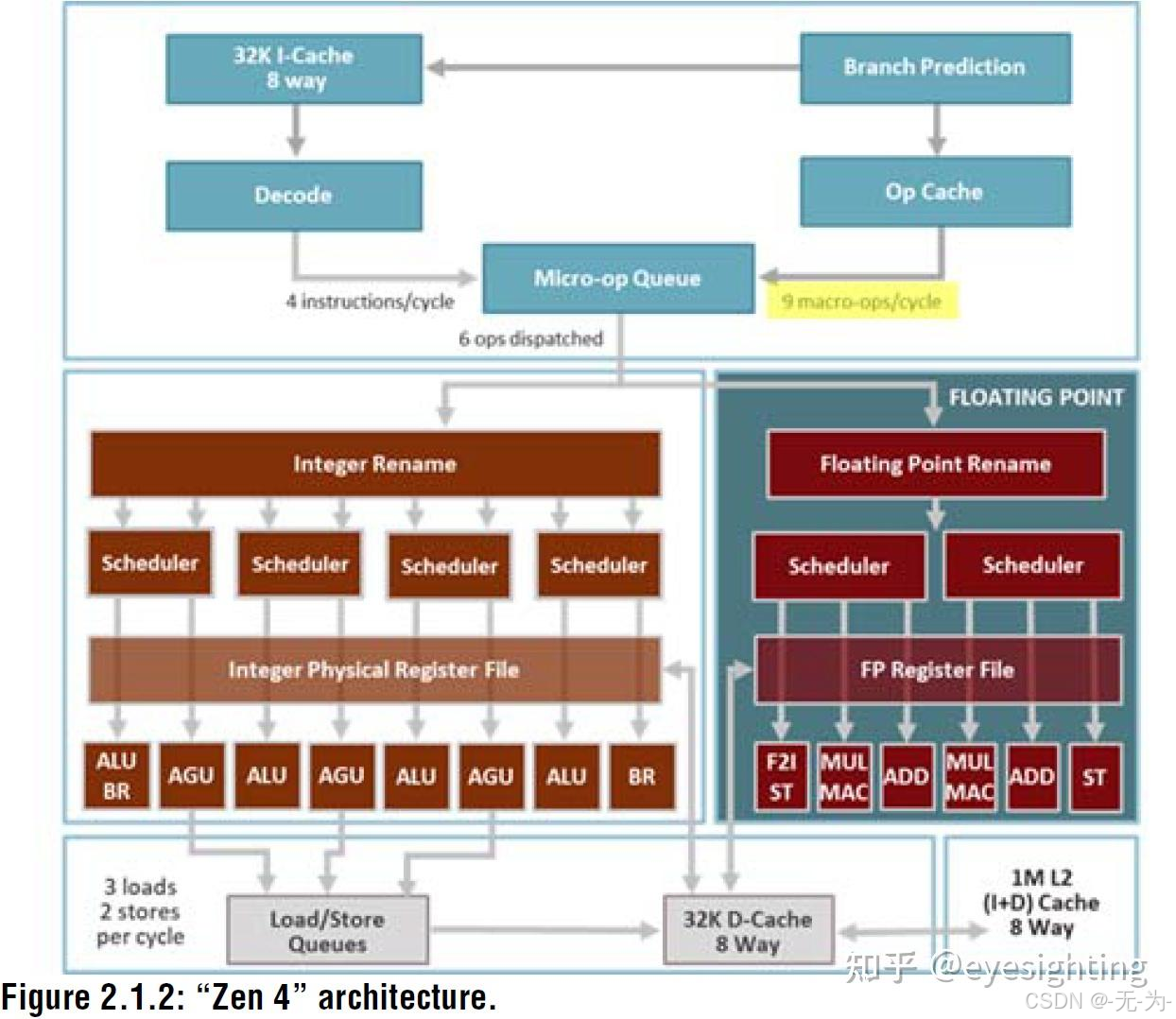

“Zen 4”是 AMD 的下一代 x86-64 微处理器核心,采用 5nm FinFET 工艺制造。设计团队和台积电之间的密切合作实现了相对于“Zen 3”使用的 7nm 工艺的优化工艺和出色的工艺扩展[1]。

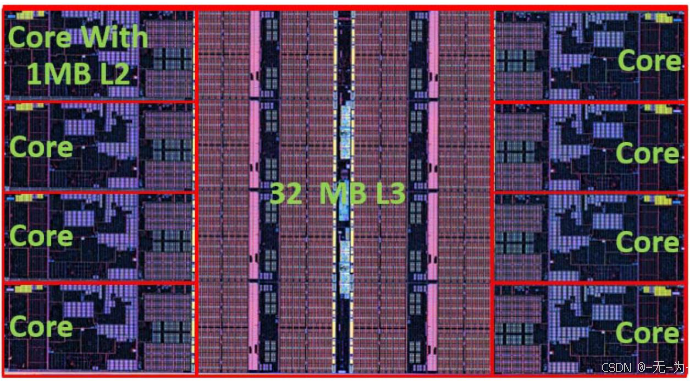

55mm2 核心复合体 (CCX) 在 8 个核心上包含 6.5B 晶体管,与上一代的 8 核心 CCX 类似。每个核心包含 1MB 私有二级缓存,是上一代的两倍,八个核心共享 32MB 三级缓存。与“Zen 3”相比,该设计还提供了过程中立的性能提升:每周期指令数 (IPC) 增加,物理设计提高了与进程无关的频率,并进行了一些更改以提高电源效率,从而最大限度地提高多线程工作负载中的单线程性能和每瓦性能。对核心微架构的增量改进使得平均单线程桌面应用程序的 IPC 比上一代提高了 13%。“Zen 4”核心的运行频率高达 5.7GHz,单线程性能比一代提升了 29% 以上。

Zen 4采用5nm工艺,使晶体管密度和功耗性能比进一步提升。新一代的架构在支持最新接口和指令集(如DDR5和PCIe 5.0)上进行了重大更新。

Zen 4不仅在性能上有显著提升,还在多核处理和高算力任务中显示出了强大的优势。根据测试数据,

Zen 4在游戏和专业工作站场景中的表现远超前代产品,使其成为市场上备受青睐的选择。

最多可以分派六个整数操作,最多支持三个负载和两个存储,并且分支预测精度比“Zen 3”有所提高。该设计还增加了整个核心的缓冲区大小。结构大小的增加包括更大的指令操作缓存、退役队列和整数寄存器文件。浮点寄存器文件大小也增加了,并且使用256b数据路径增加了对512b高级矢量扩展(AVX 512)浮点指令的节能支持。通过添加部分写入一级数据缓存项的能力,可以减少一级数据缓存银行冲突。对dcache存储阵列中使用的标准单元进行布局优化,将与添加部分写入功能相关的面积成本降低了20%以上。

Zen 5及未来发展

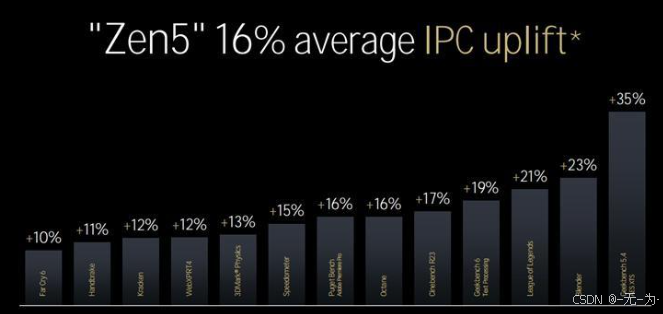

在2024年的Hot Chips大会上,AMD正式展示了其最新一代处理器架构——Zen 5。

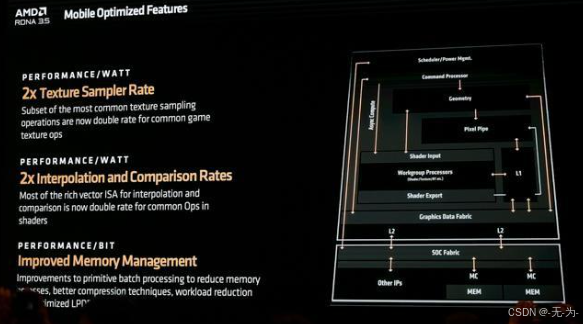

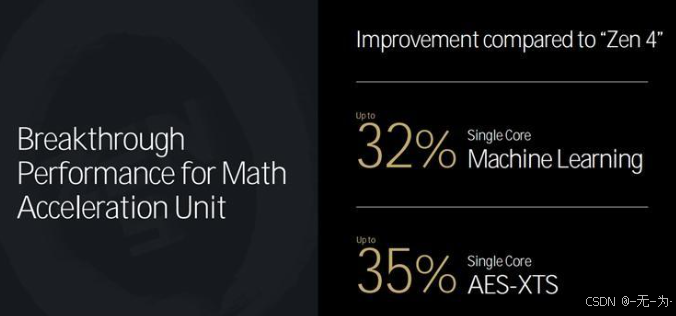

Zen 5在既有架构的基础上进行了进一步优化,通过引入更高效的指令解码、更先进的分支预测和更高效的整式和浮点运算单元,极大提高了整体性能。新的架构还引入了更大的L1数据缓存和全面支持AVX-512指令集,使性能和能效比达到新的高度。

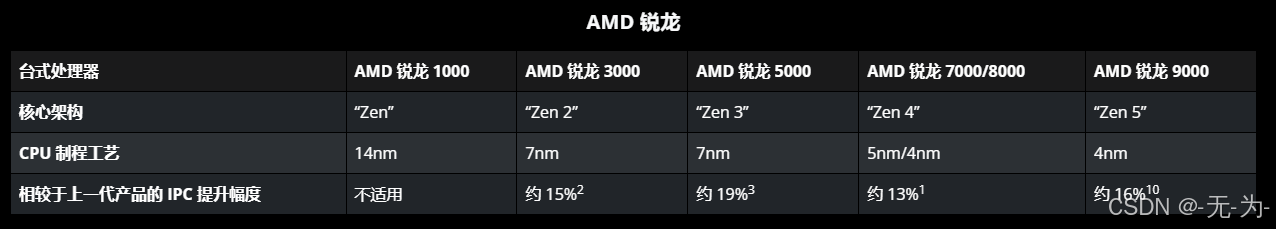

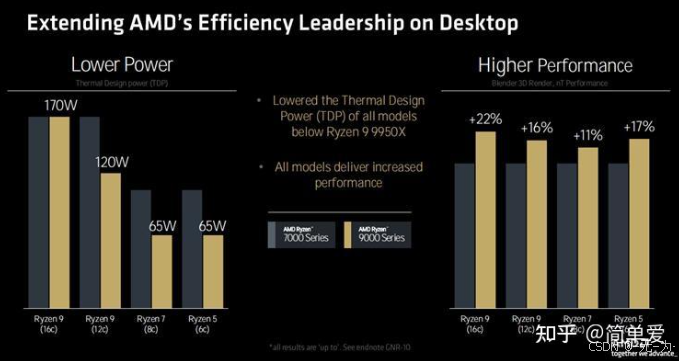

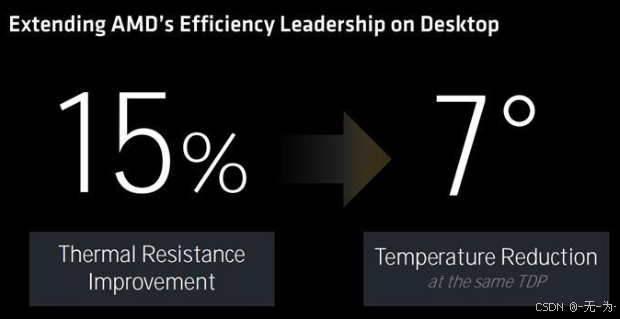

值得注意的是,与移动处理器有所不同的是,AMD锐龙9000桌面处理器并没有加入NPU,预计未来桌面CPU的主要功能还是与GPU打配合,从而满足复杂的AI应用。具体到大家关心的性能数据上,AMD Zen5的IPC相比较Zen 4提升了16%左右,这个成绩还是相当令人满意的,毕竟除了IPC之外,基于Zen 5打造的锐龙9000系处理器在频率上同样有所提升。

针对低功耗应用场景,AMD还推出了Zen 5c核心,为移动计算设备和嵌入式系统提供了更多选择。

AM4和AM5接口的承接

除了架构本身的进化,AMD在处理器接口上的策略也为其赢得了许多赞誉。

自2016年末发布AM4接口以来,AMD在八年间推出了五代CPU架构和四代制造工艺,AM4接口实现了一次次硬件的跨代兼容。近年来,尽管AM5接口已经推出,但AM4接口的处理器依然在市场上销售,并且具有非常高的性价比。AMD还宣布AM5接口将至少持续到2027年,为用户提供了更长久、更稳定的硬件支持。这种策略不仅显示了AMD的技术优势,也凸显了其用户导向的市场策略。

回顾AMD Zen架构的发展史,我们可以清晰地看到AMD在技术创新和市场战略上所取得的巨大成功。

从Zen 1的初步崛起,到Zen 2和Zen 3的飞跃,再到Zen 4和Zen 5的不断优化和进化,AMD一次次在高性能处理器市场上取得重大突破。凭借其先进的工艺技术、灵活的产品设计和用户友好的市场策略,AMD已经成为全球处理器市场的重要玩家。

未来,随着Zen架构的继续演进和新的技术突破,AMD有望在更广泛的应用领域内继续提高其市场份额和影响力。

2405

2405

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?