时序逻辑电路的设计的一般思路

1.对设计要求进行抽象,制作原始状态图和状态表

-

建立原始状态图

假定一个初始状态,由这个状态出发,每加入一个输入信号,就记录其次态,并标记其相应的输出值。

-

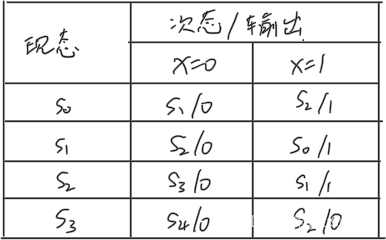

Mealy型状态表 形如

-

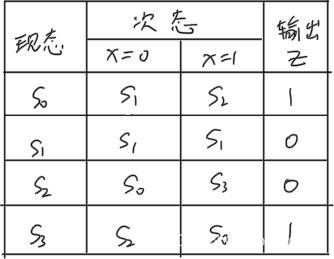

Moore型状态表 形如

- PS:有些题目可以直接写出状态表,可以省略状态图

2.化简原始状态表

1.完全确定的状态表的化简步骤

- 隐含表法化简

2.不完全确定的状态表的化简步骤(存在不确定的次态或输出)

- 隐含表法化简

- 作状态合并图,求最大相融类

- 作最小闭覆盖

3.状态分配

- 四条原则(优先级分前后)

- 相同输入,次态相同,现态应相邻

- 相邻输入,同一现态,次态应相邻

- 输出完全相同,现态相邻

- 出现次数最多的状态或初始状态应该分配为逻辑0。

4.选定触发器

- 一般题目会指定触发器,若为指定触发器,最好选用JK触发器(功能最全)

5.求输出函数和激励函数表达式

- 两种方法

- 根据次态方程来确定

- 根据激励表来确定

6.作逻辑电路图

7.分析是否有挂起状态

- 在用卡诺图化简激励函数表达式时,圈到的d(不确定状态)设为1,未圈到的设为0.

- 将状态带回到状态表中,通过状态图来分析是否有挂起状态。

本文详述了时序逻辑电路设计的关键步骤,包括抽象需求、制作状态图与状态表、化简与分配、触发器选择、输出函数确定,以及检查挂起状态。通过实例演示,理解Mealy和Moore型状态表区别,以及如何运用隐含表法和状态合并图进行化简。

本文详述了时序逻辑电路设计的关键步骤,包括抽象需求、制作状态图与状态表、化简与分配、触发器选择、输出函数确定,以及检查挂起状态。通过实例演示,理解Mealy和Moore型状态表区别,以及如何运用隐含表法和状态合并图进行化简。

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?