FPGA以太网 TOE TCP/IP协议栈 源码

千兆,万兆

ping,arp,igmp,udp,tcp,dhcp……

提供k7板卡测试工程,纯hdl的,轻松移植到任意fpga

ID:565000628302200124

上升沿

FPGA以太网千兆和万兆速率下的TOE(TCP Offload Engine)是网络通信领域中的重要技术。它通过硬件实现TCP/IP协议栈的功能,提供了高性能和低延迟的网络通信能力。本文将从源码角度深入探讨FPGA以太网TOE TCP/IP协议栈,并介绍了相关的测试工程和移植方法。

一、TOE技术概述

FPGA以太网TOE(TCP Offload Engine)是一种在FPGA上实现的高性能以太网传输协议栈。它通过硬件实现TCP/IP协议栈中的核心功能,如IP分组的封装和解封、TCP连接的建立和维护、数据包的分片和重组等。TOE技术将这些功能从软件层面抽离出来,通过硬件加速的方式提供更高的性能和更低的延迟。

二、TOE技术在千兆和万兆速率下的应用

在千兆和万兆速率下,TOE技术能够有效提高网络通信的吞吐量和响应速度。通过使用硬件加速的方式处理TCP/IP协议栈,TOE技术可以实现更高的数据传输速率和更低的延迟。此外,TOE技术还可以减轻主机处理器的负载,提升整体系统的性能。

三、TOE技术的关键实现:源码分析

TOE技术的关键在于源码的实现。通过分析TOE的源码,我们可以深入了解TOE的工作原理和实现细节。TOE的源码包含了对于各种协议的支持,例如ping、arp、igmp、udp、tcp、dhcp等。通过分析这些协议的源码,我们可以进一步理解TOE的实现原理。

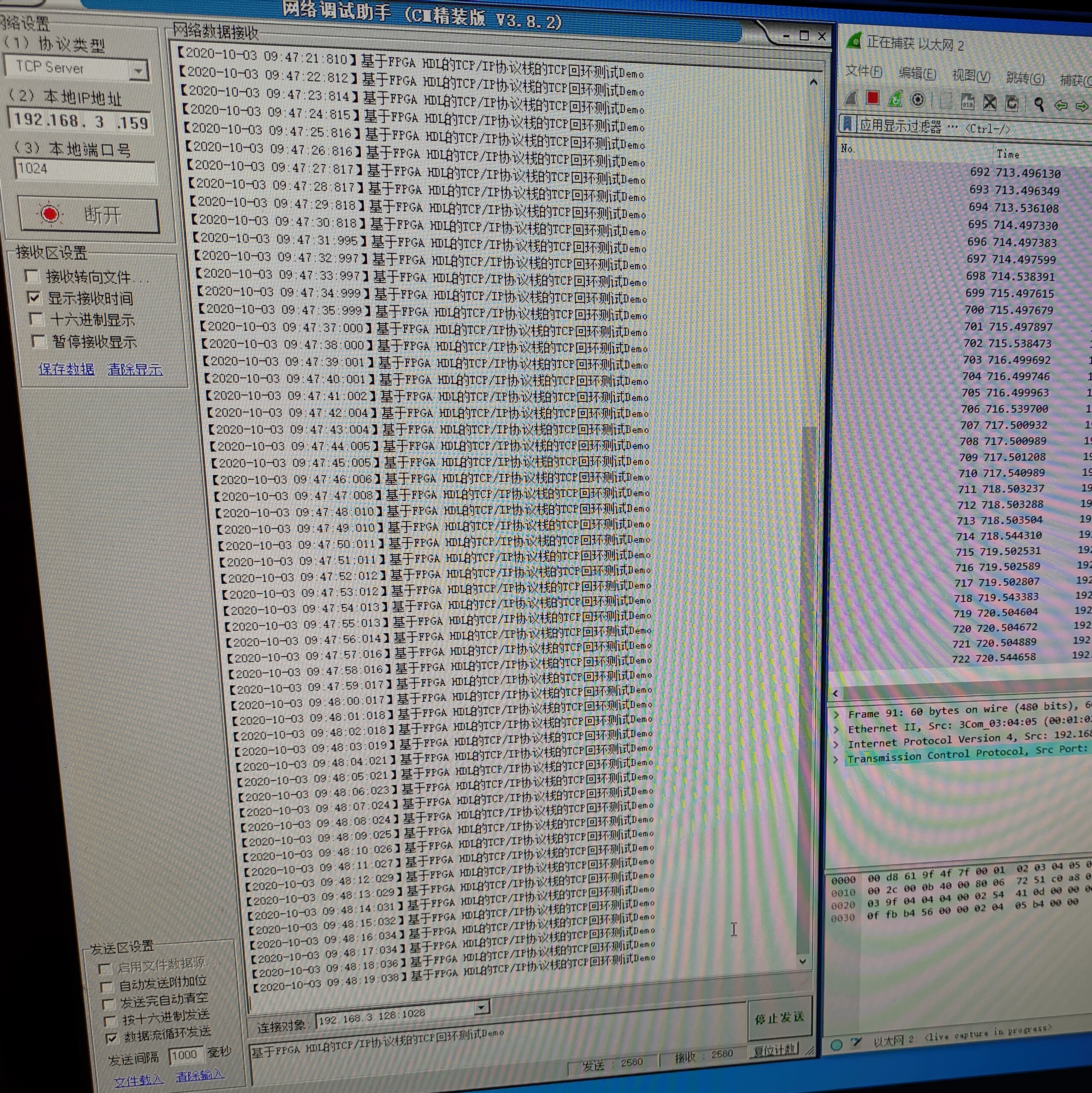

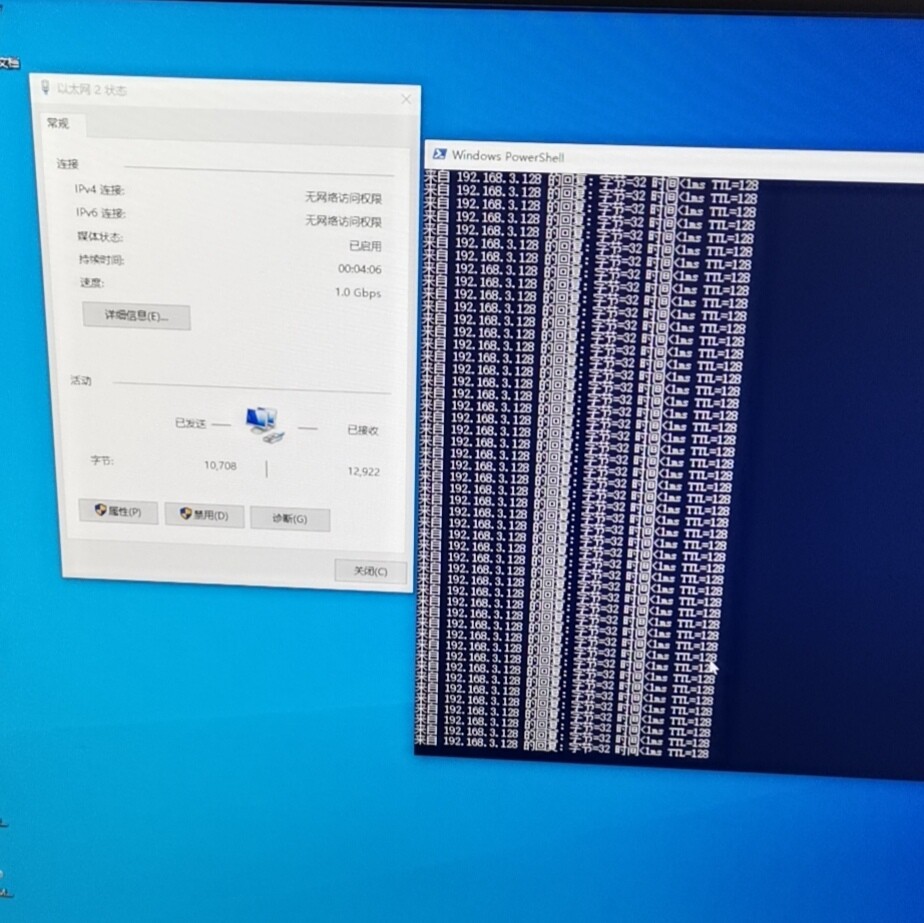

四、TOE技术的测试工程

为了验证TOE技术的正确性和性能,我们提供了k7板卡的测试工程。这个测试工程是纯HDL的,可以轻松移植到任意FPGA平台上进行测试。通过这个测试工程,我们可以对TOE技术进行全面的测试和评估,确保其在实际应用中的稳定性和性能。

五、TOE技术的移植方法

在实际应用中,我们经常需要将TOE技术移植到不同的FPGA平台上。为了简化移植过程,我们提供了一种轻松的移植方法。这种方法基于纯HDL的测试工程,通过修改少量的参数和接口,就可以将TOE技术移植到任意FPGA平台上。这大大减少了移植的复杂性和工作量,提高了开发效率。

六、总结

本文围绕FPGA以太网TOE TCP/IP协议栈展开了详细的分析和讨论。我们从源码角度深入探讨了TOE技术的工作原理和实现细节,介绍了相关的测试工程和移植方法。通过本文的阐述,希望读者对FPGA以太网TOE TCP/IP协议栈有更加深入的了解,并能够在实际应用中灵活运用。

相关的代码,程序地址如下:http://imgcs.cn/628302200124.html

821

821

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?