一、引入

在计算机系统中,CPU负责执行指令,而存储器系统为CPU存储指令和数据。

存储器系统是一个具有不同容量、成本和访问时间的存储设备的层次结构。如下图:

越接近高层,存储器的访问速度越快,存储能力越小,造价越高。

二、存储技术的介绍

1.寄存器:

寄存器是CPU内部用来存放数据的一些小型存储区域,用来暂时存放参与运算的数据和运算结果。

2.随机访问存储器

随机访问存储器又名为RAM,其分为两类:

- 静态RAM,SRAM

如上图层数 L1、L2、L3

- 动态RAM,DRAM

如上图层数 L4

静态RAM(SRAM)比动态RAM(DRAM)更快,但也贵得多。SRAM用来作为高速缓存存储器。DRAM用来作为主存以及图形系统的帧缓冲区。

(1)静态RAM,SRAM

SRAM将每个bit位的信息存储在双稳态结构的存储器单元中,如下图。每个存储器单元需要六个晶体管实现。这个电路有这样一个属性,它可以无限期地保持在两个不同的电压配置( configuration)或状态( state)之一。其他任何状态都是不稳定的,在不稳定状态时,电路会迅速转移到两个稳定状态的一个。

由于SRAM存储器单元的双稳态特性,只要有电,它就会永远地保持它的值。即使有干扰(例如电子噪音)来扰乱电压,当干扰消除时,电路就会恢复到稳定值。

(2)动态RAM,DRAM

DRAM的原理是电容充电,DRAM将每个位存储为对一个电容的充电。每个单元由一个电容和一个访问晶体管组成。但是,与SRAM不同,DRAM存储器单元对干扰非常敏感。当电容的电压被扰乱之后,它就永远不会恢复了。暴露在光线下会导致电容电压改变。

并且DRAM会因为很多原因导致漏电,所以内存系统只有通过不断的读出数据,不断刷新内存每一位数据,才能保持数据。

总结:

只要有供电,SRAM就会保持不变。与DRAM不同,它不需要刷新。SRAM的存取比DRAM快。SRAM对诸如光和电噪声这样的干扰不敏感。代价是SRAM单元比DRAM单元使用更多的晶体管,因而密集度低,而且更贵,功耗更大。

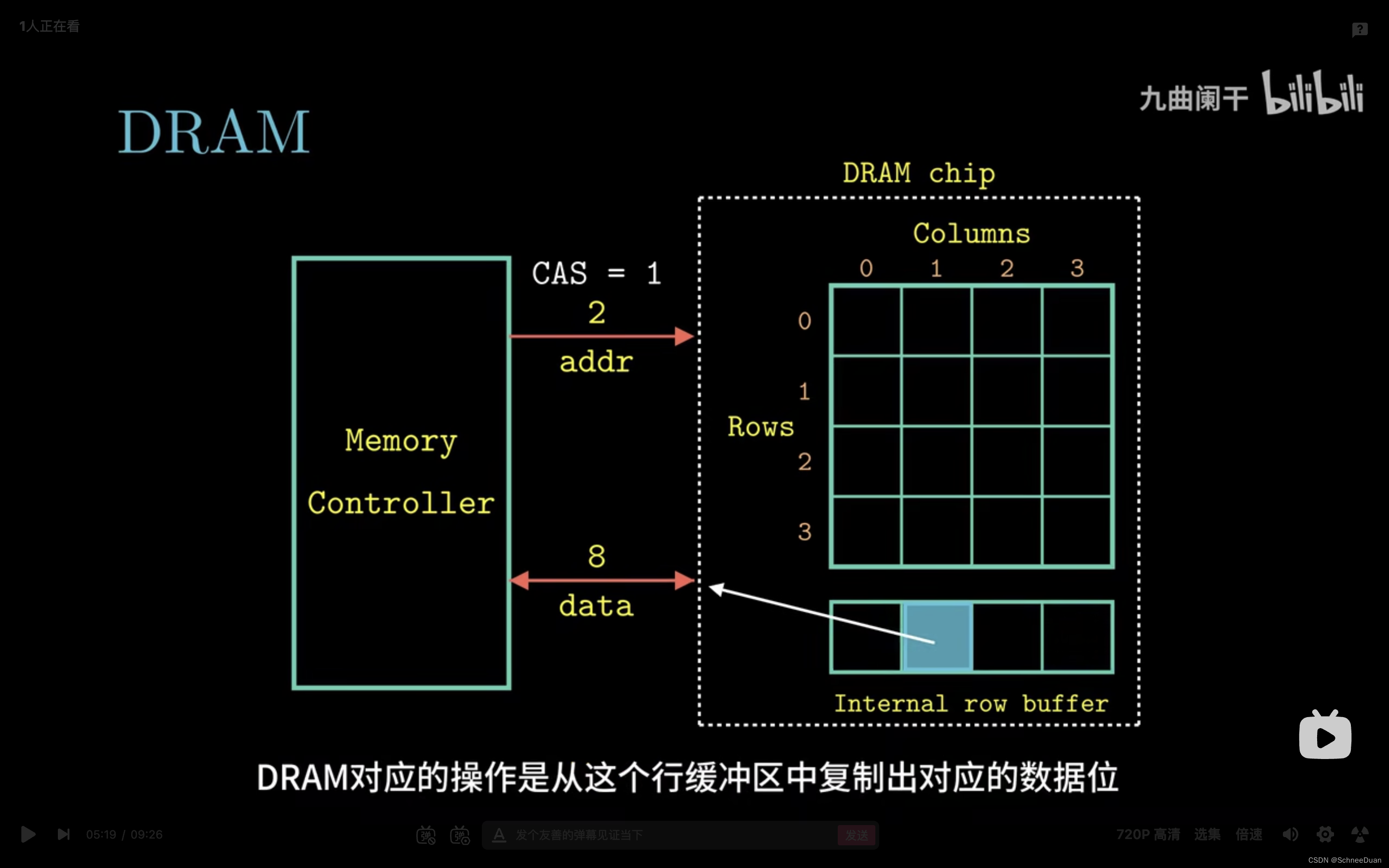

传统的DRAM:

如下图,展示的是16*8的DRAM芯片(16为超单元的个数、8为每个超单元可以存储8个bit的数据)。

可以将芯片看成二维数组的形式,通过行i列j来寻找指定的超单元。

信息通过称为引脚(pin)的外部连接器流入和流出芯片。每个引脚携带一个1位的信号。下图给出了两组引脚:8个data引脚,它们能传送一个字节到芯片或从芯片传出一个字节,以及2个addr引脚,它们携带2位的行和列超单元地址。其他携带控制信息的引脚没有显示出来。

内存控制器 依次将行地址和列地址发送给 DRAM,DRAM 将对应的超单元的内容发回给内存控制器以实现读取数据。

具体实现:

首先内存控制器 Memory Controller 发送行地址2到DRAM芯片,然后DRAM芯片将第二行的数据放到缓存区Internal row buffer 中。

接着内存控制器 Memory Controller又发送列地址1到DRAM芯片中,然后DRAM芯片将缓存区Internal row buffer的数据发送到内存控制器Memory Controller。

DRAM的内存模块:

简单来说就是,将多个DRAM芯片叠在一起,然后通过读取每一个的相同行列(i,j)的数据,每个数据在拼凑在一起得到最终的数据。

3.磁盘

磁盘在存储系统中为L5。

随机访问存储器一般在不断电的情况下才能保存数据,但是磁盘可以在断电的情况下保存数据。其中主流的磁盘分为两类:

- 机械磁盘

- 固态硬盘

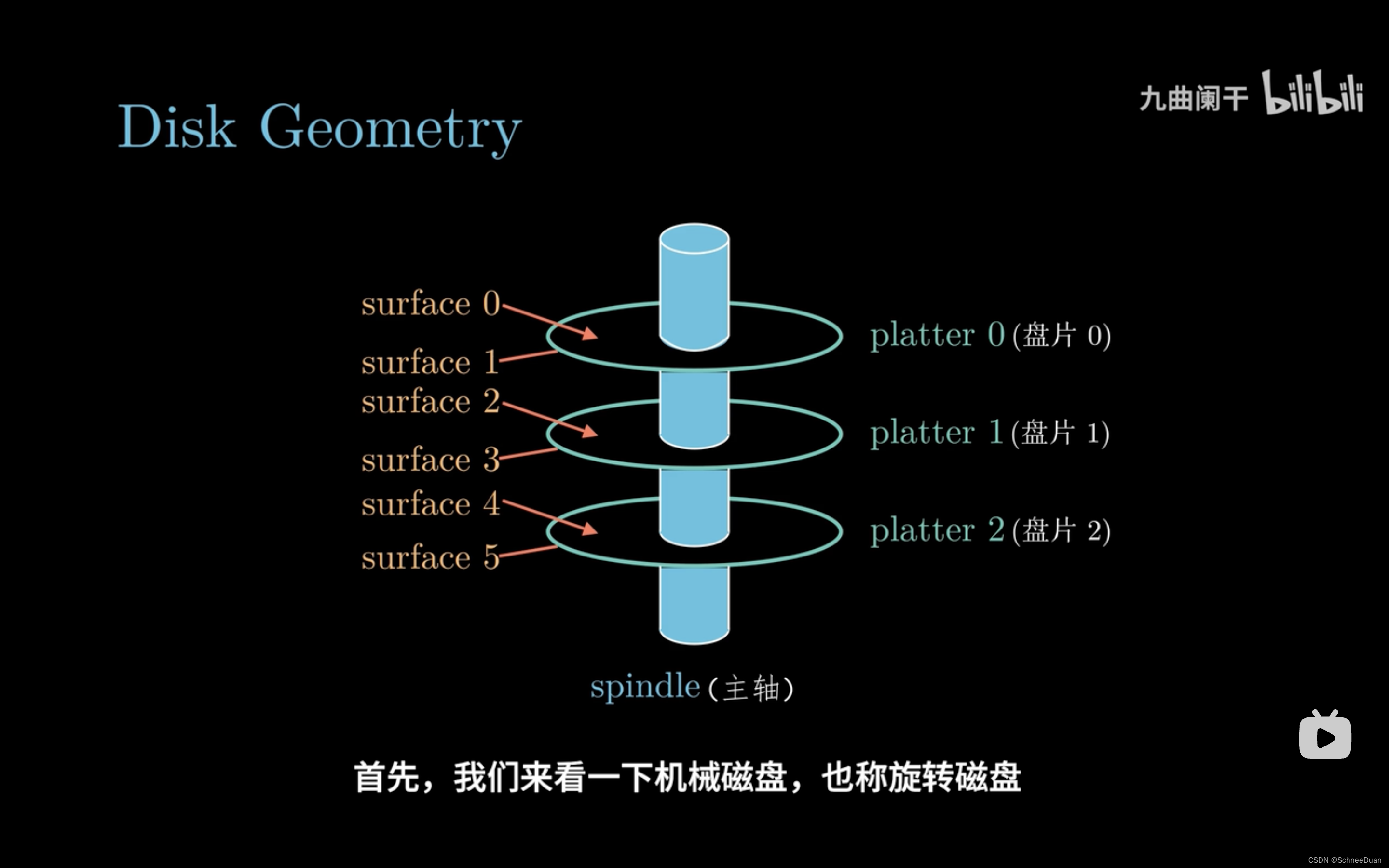

(1)机械磁盘:

如下图,磁盘由多个盘片围绕主轴旋转而成,其一个盘片有两个表面(上表面和下表面)。

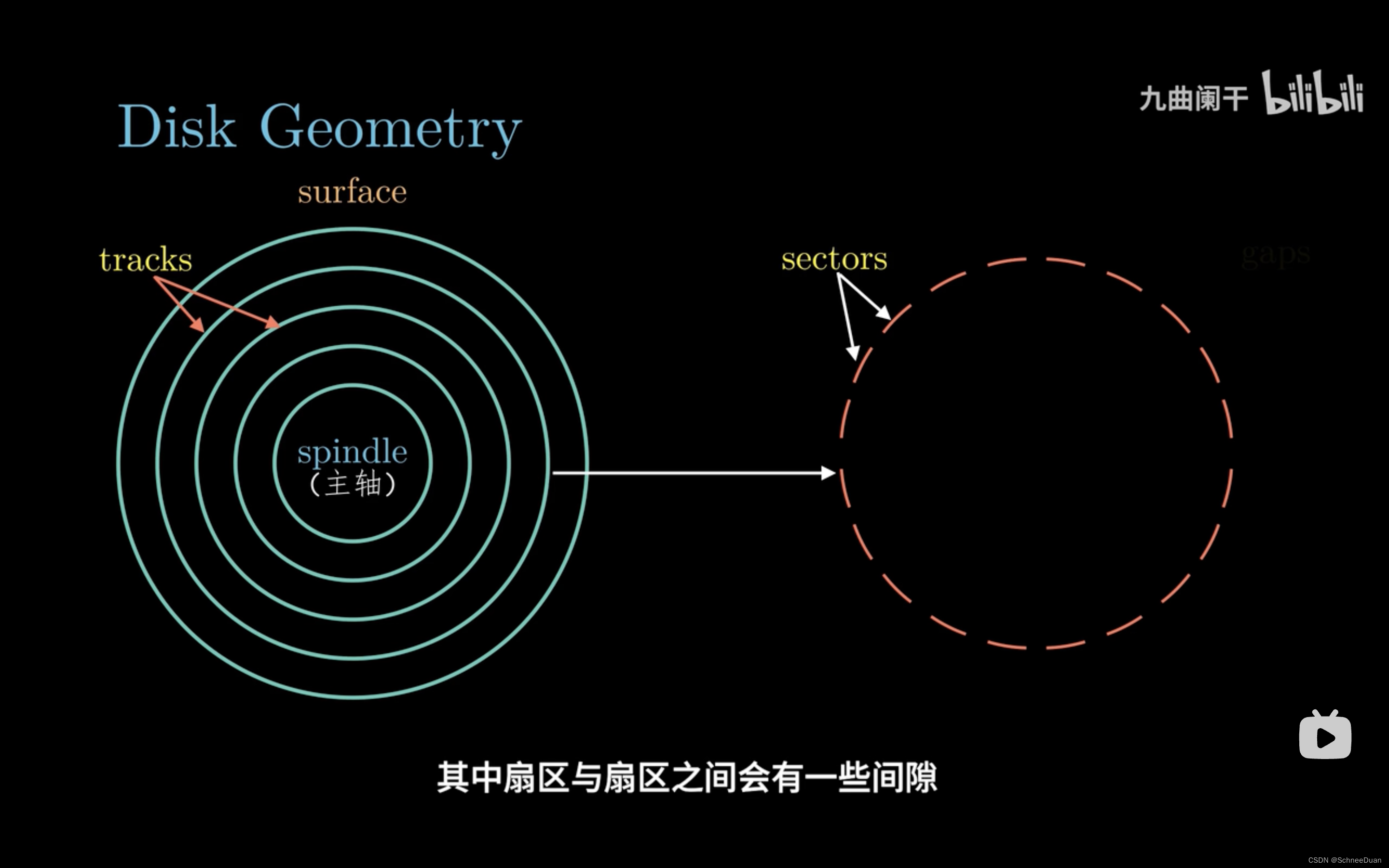

每个表面就像下面的多圈同心圆一样,其中每圈同心圆有多个扇区,扇区与扇区之间会有一些间隙,间隙用来存放扇区的标识信息,不能用来存放数据。扇区才能存放数据。

磁盘用读写头来读取数据(就像唱片),每个表面都有独立的读写头。

磁盘操作:

磁盘操作主要有寻道、旋转和传送三个过程构成,操作磁盘的时间主要寻道时间和旋转时间的延迟,传送时间相比于两者基本可忽略。

- 寻道:传动臂寻找正确的圈。

- 旋转:传动臂不动,磁盘表面旋转。

- 传送:驱动器开始读或者写该扇区的内容。

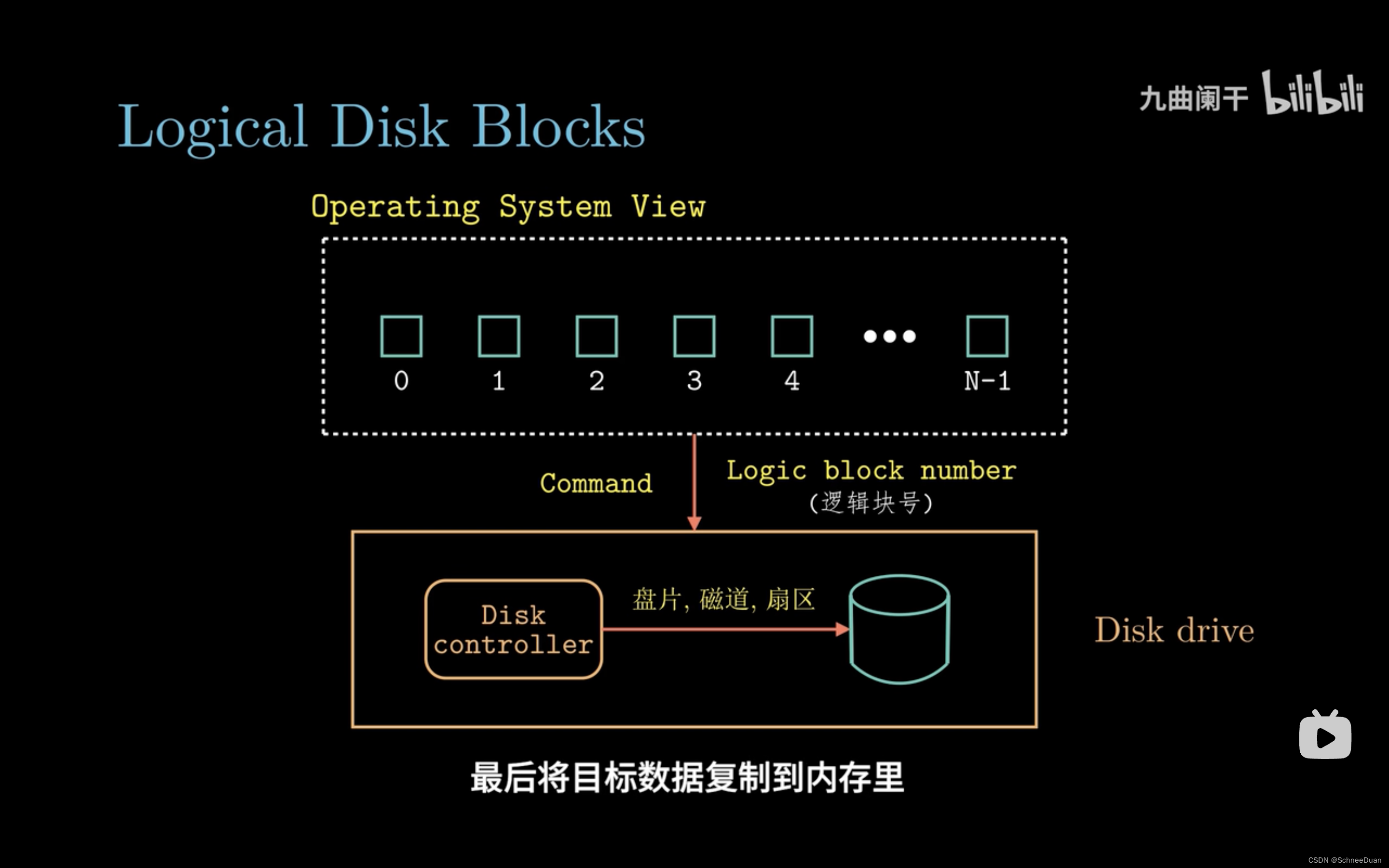

操作系统与磁盘:

从操作系统的视角来看,磁盘被抽象成了一个个等大的逻辑块,有一个磁盘控制器通过“盘片、磁道、扇区”来映射实际的磁盘。(可以理解成,有钱人为了方便买房,直接找了个中介)

(2)固态硬盘:

固态硬盘又叫SSD,结构如下图。

相比于传统的机械硬盘的读与写操作,固态硬盘还多一个擦出的操作(只能让1变成0),所以page最开始就全是1。擦除是block为单位擦除。

固态硬盘采用平均磨损算法来平摊擦除操作的磨损,以此来延长固态硬盘的寿命。

SSD相对于旋转磁盘来说,好处是访问时间块,能耗低。反复写之后,闪存块也会磨损,一般要很多年才能磨损。

三、局部性

CPU的读取速度越来越快,实际上弥补CPU和内存之间差距的关键,是程序的局部性。

局部性是程序的一个基本属性。具有良好局部性的程序倾向于重复地访问相同的数据 (时间局部性),缓存思想,或倾向于访问邻近的数据 (空间局部性),快查思想,因此运行更快。

1.存储的缓存思想

不同存储技术的访问时间差异很大,速度快的成本高,慢的成本低。如果数据在寄存器中,指令执行期间,访问需要1个时钟周期;在高速缓存SRAM中,需要4~75个周期;在主存DRAM中,需要上百个周期;在磁盘中,大约要几千万个周期

为了方便数据快速读写,数据需要经过层层缓存,以此来优化存储器结构。

存储器结构的中心思想是:快的缓存慢的。(上层缓存下层)

如下图:第k层是第k+1层的上层,第k层缓存着第k+1层的部分数据。

2.缓存命中

在程序找寻数据时,会优先访问快的存储器,即高层的存储器,比如说程序想要的数据本来在第三层,那么它会先在第二层(缓存着部分第三层的数据)找寻,如果在第二层找到,那么就是缓存命中

3.缓存不命中

与缓存命中相反,如果在第二层没找到的话,那么就会在第三层找,并且将其缓存到第二层中,如果第二层满了的话就覆盖。

4.缓存管理

缓存有很多层,每一层都需要某种逻辑来管理缓存,比如将缓存划分成块,在不同的层之间传送块,判定是命中还是不命中,并处理它们。管理缓存的逻辑可以是硬件、软件,或者两者结合。

四、基于SRAM的高速缓存存储器cache

L1、L2、L3

cache的层次结构如下图

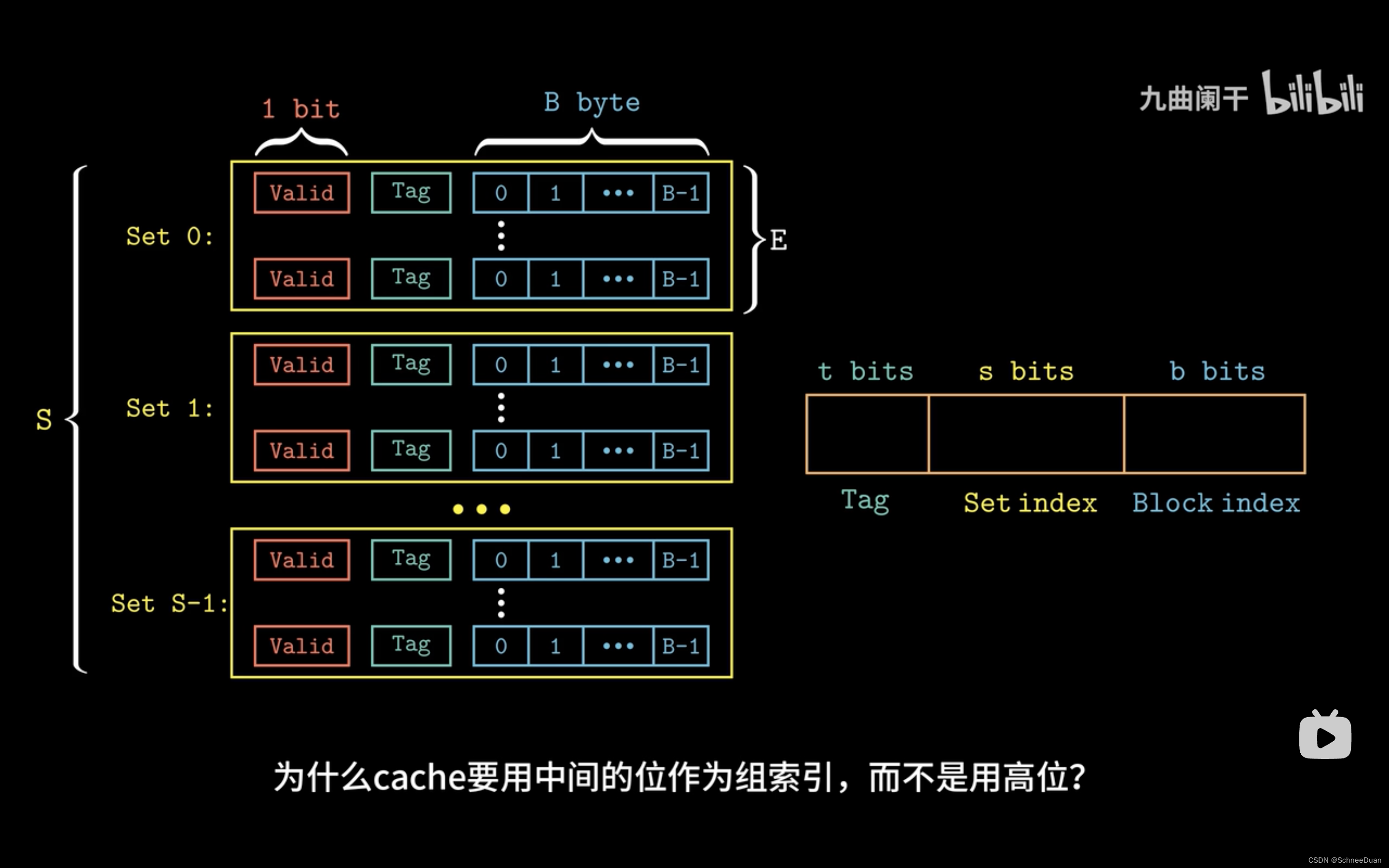

每个cache有多个set,每个set有多个高速缓存行(cache line),每个cache line有三个三部分组成:有效位valid、标记tag、数据块cache block。

具体过程:

CPU要地址A的数据,就会从高层往低层寻找。地址A结构如上图右边。

地址A是一堆0或1组成的,高位为tag、中间位为Set index、低位为Block index。

中间位Set index ,顾名思义,就是选择哪一个set,接着高位tag 是确定set中具体的哪一行,找到具体cache line后,通过具体长度为b的Block index块偏移量来确定目标数据。使用中间位做组索引,相邻的内存块可以被映射到不同的Set中,大大提高了Set的利用率。

853

853

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?