产品特色:

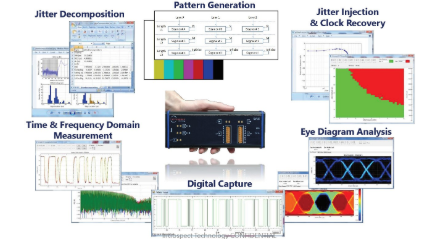

强大的硬件能力,提供宽广且连续的操作频率,单台硬件设备可同时支持16 Tx/16 Rx测试,每个信道可达12.5Gsps。单机分别提供可独立控制的信号产生器与码型侦测器。

灵活的物理层控制能力,各通道可以独立控制并提供抖动注入(Jitter Injection)、相位调整(Skew)、电压摆幅控制以及时序调整的能力,大幅提高测试完整度。

提供多种协议模型,可应用在DRAM、DB、RCD与Module等产品开发。

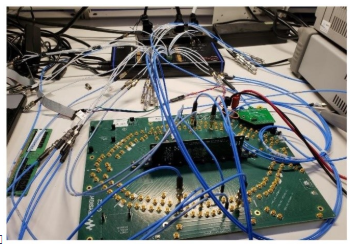

轻巧且可携带的体积,在实验桌上即可以完成系统级测试。

弹性且灵活的Python软件开发环境,可搭配控制循环进行多个测试变量的自动化测试并自动产生测试报告。

内存是半导体行业中增长最快的部分,存储技术在密度、效率和传输速率方面持续的迅速提高。在建置最新一代双倍数据速率(DDR)存储接口时,开发人员在设计验证将面临着前所未有的挑战。一方面,DDR接口是采用单端的设计,并且对于每个存储装置都需要大量的信号走线。另一方面,最新的标准(如DDR4/5)要求非常精确的量测设置,更新增了接收器的压力测试。

Introspect Technology的高速多通道码型/封包产生器和信号分析仪解决方案非常适合DDR4与DDR5的接口测试。所提供的产品规格已经高于JEDEC所定义的传输速率,同时我们也与世界上一些最先进的CPU和内存芯片制造商同步开发更多应用在DDR4/5的测试功能,这些功能将涵盖更广泛的物理层以及协议层的测试,并且不断的更新与支持最新的协议规范。这些强大的功能与极具竞争力的价格,让Introspect SV5C系列产品正快速成为高速实验室中做为DDR4/5开发与特性化测试的标准测试平台。

462

462

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?