文章目录

1、FPGA硬件调试

1.1 硬件调试简介

FPGA硬件调试是指将FPGA生成的位流文件(bit文件)通过下载器烧录或者固化到FPGA或Flash中,通过在线逻辑分析仪抓取实时信号来验证逻辑功能是否满足预期,或者通过系统测试来验证逻辑设计的正确性。

1.2 FPGA调试IP核

硬件的诊断和校验可能会占用开发周期的30%~40%。

对于Xilinx FPGA厂商提供的开发软件,Vivado和ISE都有相应的调试IP核,这些调试IP核属于FPGA调试的一部分。例如,使用ILA IP核可以在线观察FPGA内部信号,使用VIO IP核可以通过虚拟按键输出相关信号。

ILA是Vivado下的一个Debug IP核,类似于片上逻辑分析仪,通过在RTL设计中嵌入ILA IP核,可以抓取信号的实时波形,帮助设计人员定位问题。

1.3 闪烁灯实例展示

1、系统设计

基于Xilinx FPGA闪烁灯逻辑设计主要分为三个模块:时钟模块、闪烁灯模块和调试模块。

2、程序设计

(1)闪烁灯程序设计,包括顶层文件和模块程序。

(2)闪烁灯约束文件

3、硬件调试

(1)闪烁灯IP核定制,需要用MMCM IP核和ILA IP核。

逻辑综合与布局布线

2、vivado编程总结

2.1 输出打印函数

$display

$strobe

$write

2.2 实例化接口注意事项

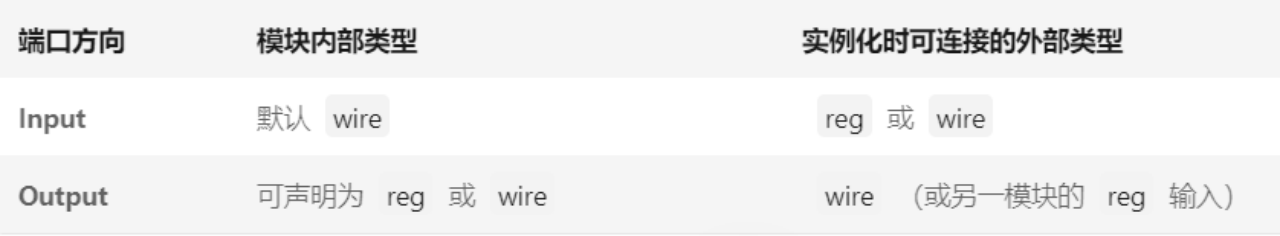

输入端口:模块内部类型默认为wire,实例化时可连接的外部类型为reg或wire

输出端口:模块内部类型可声明为reg或wire,实例化时可连接的外部类型必须为wire或另一模块的reg输入

2.3 性能指标

FF(Flip-Flop):触发器,时序逻辑的基本单元

每个FF通常与一个LUT组合在同一个CLB中。

资源报告中显示的FF数量反映了设计中需要存储的“状态”数量。

LUT(Look-Up Table):查找表,FPGA中实现组合逻辑的核心组件。

LUT的使用数量直接反映了设计的逻辑复杂度。

2.4 BRAM IP的使用方法

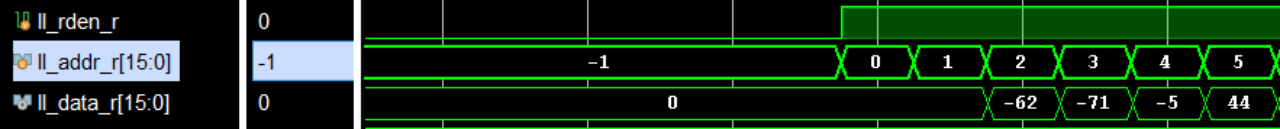

BRAM读数据:读使能信号拉高后会延迟两个周期输出数据。

BRAM写数据:写使能信号拉高后需要将数据在同一周期内写入。

2.5 语法相关

wire非阻塞赋值给reg类型,不延迟一个周期;但reg非阻塞赋值给reg类型,会延迟一个周期

BUFG:全局时钟资源

2.6 逻辑保留语法

(* DONT_TOUCH = “TRUE” ) 作用阶段:在综合和实现阶段均生效。

功能:强制工具在整个流程(综合+实现)中保留标记的逻辑,禁止任何优化或修改,这包括防止逻辑被吸收、合并、删除或重构。

适用范围:需要绝对保留逻辑的场景。例如手动优化的关键逻辑。

举例:( DONT_TOUCH = “TRUE” *) module critical_module (…);

(* keep = “true” ) 作用阶段:在综合阶段生效。

功能:阻止综合工具对标记的信号或模块进行优化,但不能保证在实现阶段中逻辑不被修改。适用范围:通常用于保留信号或层次结构。优先级低于DONT_TOUCH。

举例:( keep = “true” *) wire debug_signal;

2.7 PS和PL

PS:Processing System,处理系统,PS是FPGA中集成的硬核处理器子系统,通常基于ARM架构;

功能:

运行操作系统(如Linux)或裸机程序,处理控制密集型任务。

提供外设接口(如UART、Ethernet、USB、GPIO等),支持通用计算和系统管理。

与PL通过高速总线(如AXI)进行通信。

特点:硬件固定,不可编程,专注于软件任务的执行。

PL:Programmable Logic,可编程逻辑,PL是FPGA的传统可编程逻辑部分。

功能:

用户通过硬件描述语言(如Verilog/VHDL)定制逻辑功能,实现高速并行计算或硬件加速。

支持灵活重构,适用于实时信号处理、图像处理等高性能场景。

特点:高度可编程,资源可根据需求重新配置,与PS协同提升系统效率。

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?