csapp分类:

Exception(异常),分为同步异常和异步异常,本质都是将控制交给kernel解决的。

异步异常,也称为中断(Interrupt)指由处理器外部的事引起的,计时器中断和I/O中断时最常见的两种;

同步异常,由执行某条指令导致的,分为Trap(陷阱,比如syscall),Fault(故障,比如页故障page fault)和Abort(终止)三种情况。Trap和中断都会返回下一条指令,故障是重新执行之前触发事件的指令。

xv6 textbook中分类方式是syscall,exception和interrupt,其实可以理解为syscall,同步中断和异步中断??。在大多数处理器中这三种事件都是用一种硬件机制处理的。

Intel Chapter 9 这里分类是这样的,和xv6 book相同,按照处理器内部和外部检测分类中断和异常,理解一下其实和csapp说法类似,只不过似乎csapp里把中断称作异步异常:

中断: 外部,异步

可屏蔽中断:通过INTR线向CPU请求中断,主要是外部设备如硬盘,打印机,网卡等。

bit 9 of FLAG register is IF(Interrupt-Enable Flag) and IF = 0,屏蔽,IF = 1,不屏蔽。CLI和STI可以显式的清楚和设置IF位(只有CPL <= IOPL才可以执行)。RESET可以清除IF。此外还有隐式的更改。

不可屏蔽中断:通过NMI线向CPU请求中断,如电源掉电,硬件线路故障等,当一个NMI handler在执行的时候,其余的来自NMI的中断信号会被忽略直到下一个IRET指令执行。

异常: 内部,同步,处理器自己在执行指令过程中检测到的

处理器检测到的:trap(总是返回到下一条指令),fault(可恢复的错误比如除法错误,0号异常,可能返回到当前指令),abort(不可恢复的错误)

Programmed:虽然是software interrupts,例如INTO,INT 3,INT n,BOUND,但是处理器把它们当作异常处理

trap和interrupt的区别: traps are caused by the current process running on a processor (e.g., the process makes a system call and as a result generates a trap), and interrupts are caused by devices and may not be related to the currently running process

优先级处理问题:

如果在一个指令边界有不止一个中断或异常挂起,处理器只能一次处理他们中的一个。中断和异常之间的优先级被表9-2显示。处理器最先处理优先级最高的中断或异常类型,把控制转移到最高优先级的中断处理程序里的第一条指令。低优先级的异常将被丢弃。低优先级的中断将被挂起。丢弃的异常将在返回到引起中断的指令处再次被发现。

Table 9-2. Priority Among Simultaneous Interrupts and Exceptions

Priority Class of Interrupt or Exception

HIGHEST Faults except debug faults

Trap instructions INTO, INT n, INT 3

Debug traps for this instruction

Debug faults for next instruction

NMI interrupt

LOWEST INTR interrupt

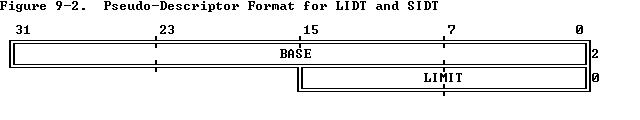

LIDT和SIDT指令:

LIDT从图9-1所示内存中加载linear address BASE and LIMIT到IDTR中

SIDT则相反

LIDT必须是CPL = 0才能执行,SIDT在任何优先级下都能执行

IDT Descriptors

三种:Task gates,Interrupt gates,Trap gates

Interrupt procedures

the IRET instruction:

pops the return instruction pointer, return code segment selector, and EFLAGS image from the stack to the EIP, CS, and EFLAGS registers, respectively, and then resumes execution of the interrupted program or procedure.

If the return is to another privilege level, the IRET instruction also pops the stack pointer and SS from the stack, before resuming program execution

如下链接是EFLAGS:

http://www.c-jump.com/CIS77/ASM/Instructions/I77_0070_eflags_bits.htm

Interrupt procedure 期间 TF 会被设置为0(注意不包含通过的Task gate哦),以避免single-step activity影响

如果是通过Interrupt gate还会重置 IF 从而避免其余Interrupts的影响

但是以上标志都会在IRET的时候恢复。

Return from an Interrupt procedure:

IRET is similar to RET except that IRET increments ESP by an extra four bytes (because of the flags on the stack) and moves the saved flags into the EFLAGS register. The IOPL field of EFLAGS is changed only if the CPL is zero. The IF flag is changed only if CPL <= IOPL.

Protection in Interrupt Procedures

中断过程(interrupt procedure)和过程调用一样:

the CPU does not permit an interrupt to transfer control to a procedure in a segment of lesser privilege (numerically greater privilege level) than the current privilege level. An attempt to violate this rule results in a general protection exception.(不允许特权级变低)

the privilege rule mentioned above effectively imposes restrictions on the privilege levels at which interrupt and exception handling procedures can execute.Either of the following strategies can be employed to ensure that the privilege rule is never violated:

1、 Place the handler in a conforming segment. This strategy suits the handlers for certain exceptions (divide error, for example). Such a handler must use only the data available to it from the stack. If it needed data from a data segment, the data segment would have to have privilege level three, thereby making it unprotected

什么是conforming segment:

An executable segment whose descriptor has the conforming bit set is called a conforming segment. The conforming-segment mechanism permits sharing of procedures that may be called from various privilege levels but should execute at the privilege level of the calling procedure.

2、 Place the handler procedure in a privilege level zero segment.

Interrupt Tasks

https://pdos.csail.mit.edu/6.828/2018/readings/i386/s09_06.htm

看上面链接最后一段,没太理解细节,还要看链接对应的书里的chapter 7

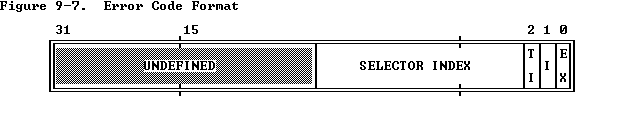

Error Code

EX :whether an event external to the program caused the exception.

I:if the index portion of the error code refers to a gate descriptor in the IDT.

TI:when I = 0,TI = 0=>GDT,TI = 1=>LDT

In some cases the error code on the stack is null, i.e., all bits in the low-order word are zero.

715

715

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?