点击此处获取源代码(一码通关)cpu24.circ

本代码为原创首发,创作不易,谢谢支持!

下载链接 https://afdian.com/a/fries

https://afdian.com/a/fries

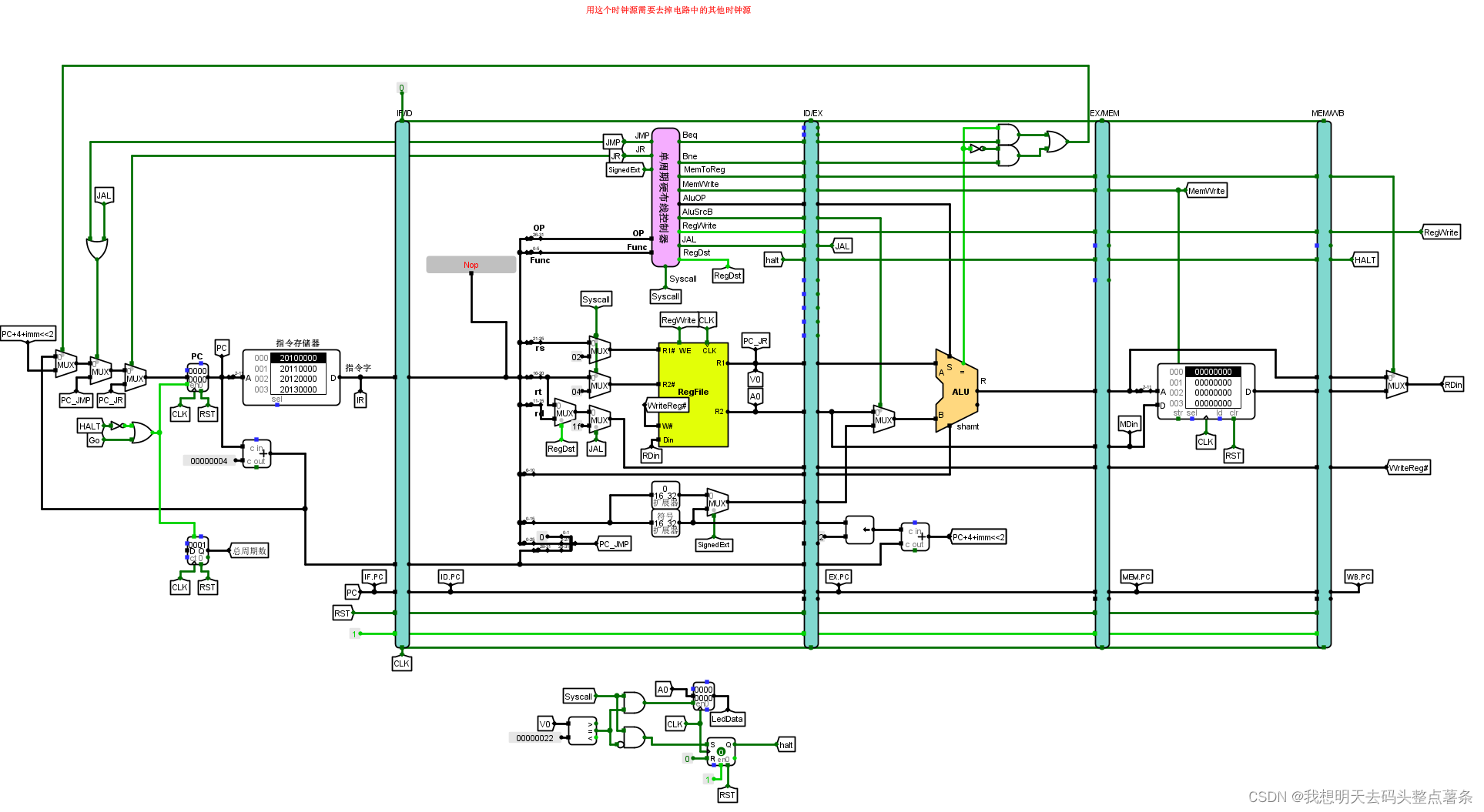

实验成品电路图

MIPS流水CPU设计所有实验见该博客:

目录

实验目的

学生掌握流水接口设计的基本原理,能够将单周期的CPU改造成可以运行无任何冲突冒险程序的理想流水线。

实验内容

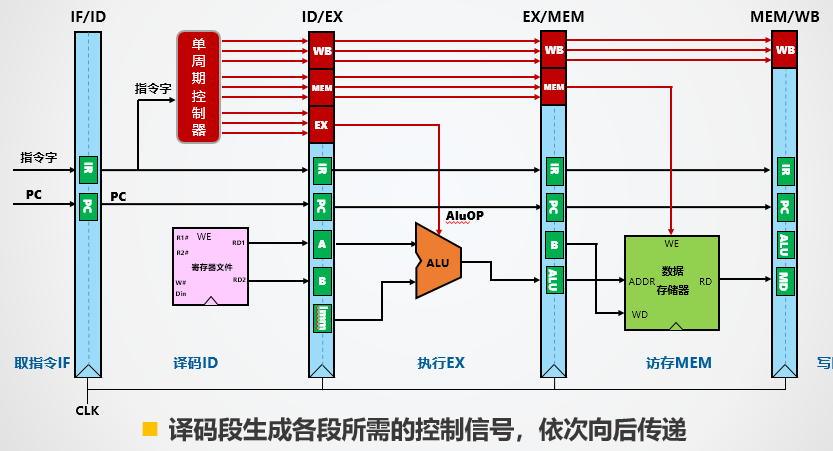

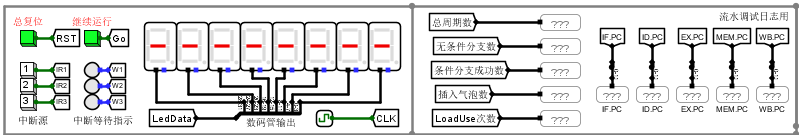

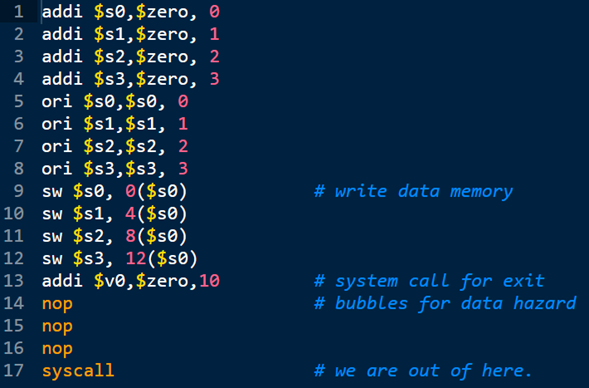

将单周期CPU修改为理想流水线。设计流水接口子电路IF/ID、ID/EX、EX/MEM、MEM/WB,并测试联调理想流水线测试.asm程序,Ctrl+k自动仿真,运行17条指令后停机,时钟周期应该是21,由于最后一拍没有计数,周期数显示应该是20。实验基本原理图如下所示:

电路框架

cpu24.circ 理想流水线子电路

注意:可以整体平移引脚框到电路任何位置,但由于电路封装与引脚位置和顺序有关系,所以框内引脚一律不许增删改,哪怕是移动位置调整顺序,改变引脚朝向,也不要在电路中增加额外的引脚,否则测试系统无法测试。

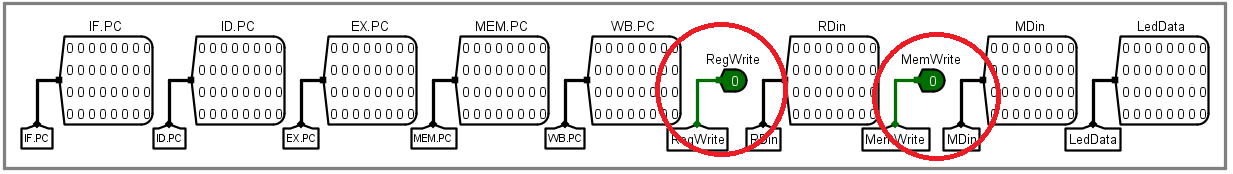

电路引脚

| 信号 | 位宽 | 功能描述 |

|---|---|---|

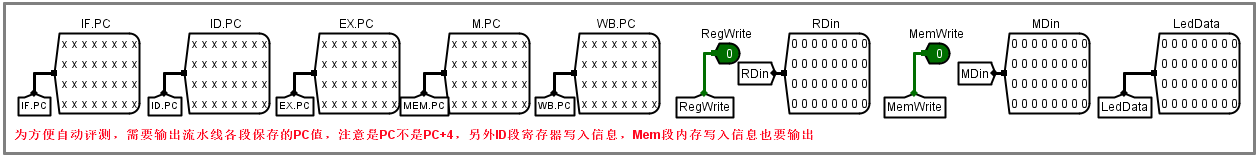

| IF.PC | 32 | IF阶段PC值 |

| ID.PC | 32 | ID阶段PC值 |

| EX.PC | 32 | EX阶段PC值 |

| MEM.PC | 32 | MEM阶段PC值 |

| WB.PC | 32 | WB阶段PC值 |

| RegWrite | 1 | 寄存器堆写使能控制信号,直接连寄存器堆WE端口 |

| RDin | 32 | 寄存器堆写入端口的数据,直接连寄存器堆Din端口 |

| MemWrite | 1 | 存储器写使能控制信号,接MEM段的RAM上的Str端口 |

| MDin | 32 | 存储器写入端口的数据,接MEM段的RAM上的Din端口 |

| LedData | 32 | LED显示输出值,连数码管输入数据LedData标签 |

待测电路默认封装如下,提交测试前请检查是否一致,如不一致,检查引脚是否修改过,另外可以通过恢复默认封装功能尝试修复。

电路测试

完成设计后,加载 理想流水线测试.hex 程序,测试功能。确认实验完成正确后,可利用文本编辑工具打开 cpu24.circ,将所有文字信息复制粘贴到 educoder 平台的 cpu24.circ 文件中,再点击评测按钮即可进行本关测试。平台会对你设计的电路进行自动测试,为方便测试,请勿修改子电路封装。

测试输出结果说明

| # | 信号 | 功能描述 |

|---|---|---|

| 1 | CLKs | 时钟计数,表明当前节拍,注意计数为十六进制 |

| 2 | IFPC | 当前节拍IF段PC的期望值 |

| 3 | IDPC | 当前节拍ID段PC的期望值 |

| 4 | EXPC | 当前节拍EX段PC的期望值 |

| 5 | MEMPC | 当前节拍Mem段PC的期望值 |

| 6 | WBPC | 当前节拍WB段PC的期望值 |

| 7 | PCerr | 5位指错字:从左到右分别表示IF、ID、EX、MEM、WB段PC出错的情况,1表示错误,0表示正确 |

| 8 | Werr | 4位指错字:从左到右分别表示RegW、RDin、MemW、MDin出错的情况,1表示错误,0表示正确 |

| 9 | LED | LED显示输出期望值 |

| 10 | RegW | 寄存器写使能控制信号的期望值 |

| 11 | RDin | 寄存器文件写入端口的数据的期望值 |

| 12 | MemW | 存储器写使能控制信号的期望值 |

| 13 | MDin | 存储器写入端口的数据的期望值 |

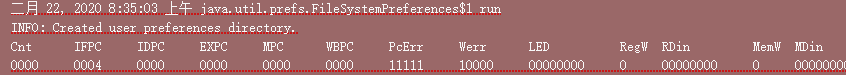

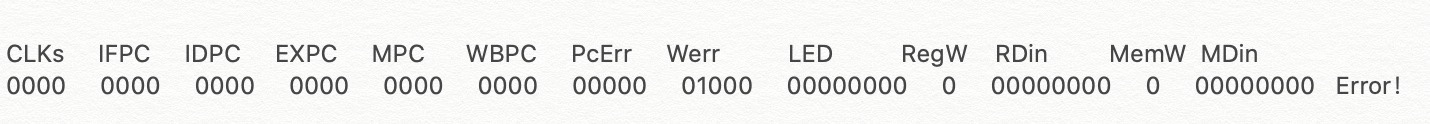

由于24条指令的测试程序benchmark节拍周期数过多,所以会输出大量信息,educoder平台不支持,所以本测试中使用了精简模式,左侧测试用例部分这里仅仅输出表头,如下图所示

![]()

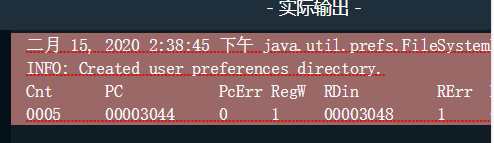

右侧实际输出部分仅仅输出表头和错误节拍对应的各监测引脚的标准值,如下图所示

如果未能通过测试,系统会输出待测CPU出错的节拍编号,以及当前节拍下各监测引脚的期望值以及出错情况,请根据出错字找出错误,将cpu运行到对应节拍下(注意CLK值为十六进制)进行比对,并根据指令的功能进行调试。

调试技巧与常见故障

私自调整引脚,看下图,很隐蔽的调整

第0拍就出错了,我机器上运行好好的啊,最有可能就是你封装不对,查看下电路封装,恢复为默认封装即可!

Werr=01000,RegW=0,表示RegWrite信号不对,预期为0,但是你的信号为1,造成这个的原因是RegWrite信号连接的位置不对,应该连接写回段的RegWrite信号,也就是直接连接寄存器堆的WE使能端,不要连ID段控制器的RegWrite输出。

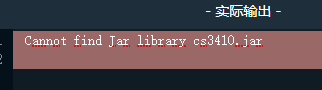

出现以上故障,是因为本地 cs3410.jar 和测试平台中的 cs3410.jar 路径不一样导致的。一般建议本地的 jar 文件和 cpu.circ 文件在同一目录下,如果出现这个问题,可以将本地 cs3410.jar 先移动到 cpu.circ 同目录下后,打开 cpu.circ,logisim 会提示找不到 cs3410.jar,重新指向同目录 cs3410.jar,存盘退出,再重新上传电路文本内容,即可解决这个问题。

也可以直接修改平台代码,搜索 cs3410,如下所示:

<lib desc="jar#6.CPU设计实验/cs3410.jar#edu.cornell.cs3410.Components" name="7">

将上面的绝对路径删除,改成如下形式即可:

<lib desc="jar#cs3410.jar#edu.cornell.cs3410.Components" name="7">

开始你的闯关任务吧,升级打怪中....

2662

2662

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?