设计目的

全志(AllWinner)V3S配备了3个串口和1个USB Root HUB,对于多端口接入场合是不够的。自带的3个串口中,UART0作为芯片的调试口用掉了,UART1作为RS485通信接口也用掉了,UART2接另一个接口芯片也被占用。单一的一个USB口,如果直接拉出去的话,只能外接USB HUB做扩展,集成度无法提高。应用中,USB口除了作为USB端口使用以外,还需要连接USB-UART用以扩展更多的串口,也需要连接USB-SPI/I2C转换芯片等场合。因此,V3S核心板配备一个USB HUB,连接一个WIFI模块,预留三个USB口用以其它扩展是必要的。

本次设计即是实现了V3S USB->USB HUB->WIFI的连接。

有图有真相先!;)

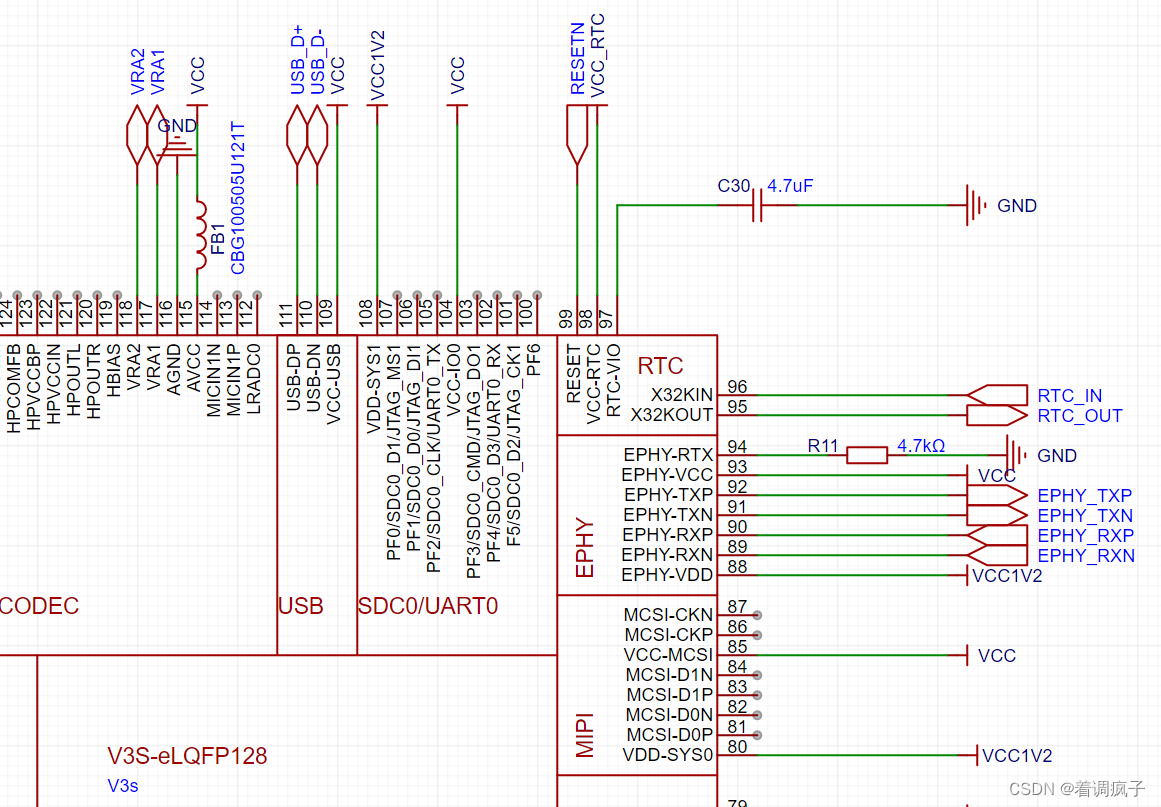

原理图

V3S的USB管脚非常简单,列举如下:

- 第109脚,USB POWER,接3.3V

- 第110脚,USB_D-

- 第111脚,USB_D+

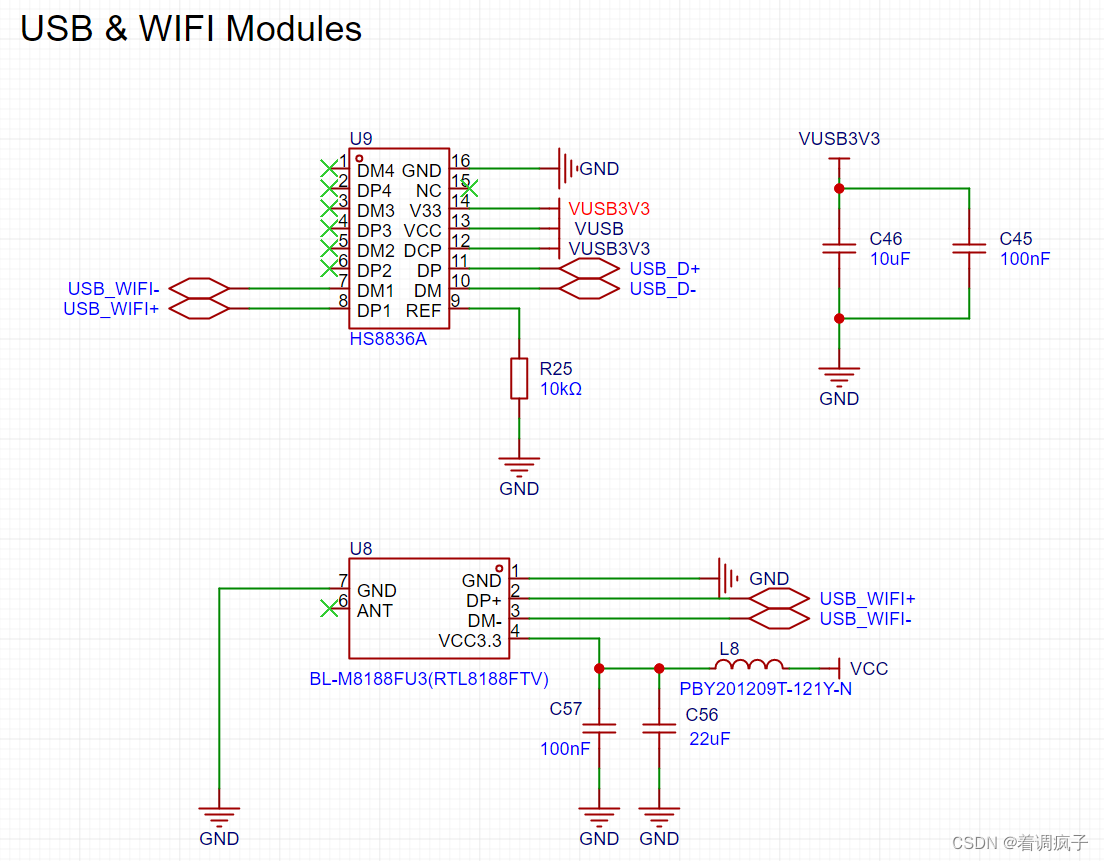

USB HUB使用了口碑较好的HS8836A,是一颗1拖4的USB HUB。本次设计中只使用了1进1出。

第10脚,USB_D+,直连主芯片

第11脚,USB_D-,直连主芯片

第8脚,USB_WIFI+,直连WIFI模块的DP+

第7脚,USB_WIFI-,直连WIFI模块的DP-

第13脚,接VUSB,5V

第12脚和14脚,连接在一起,是HS8836A的内部电源输出,电压是3.3V~4V,根据参考设计,使用一颗10uF和一颗100nF的电容去耦/稳压,这两颗电容靠近第13脚放置。

第9脚,使用一颗10KΩ的电阻可靠接地。参考设计中也说用100KΩ的电阻,实测中发现10~100KΩ没有影响。第9脚是否可靠接地将影响到HS8836A是否能正常工作,因此在将来量产版本中计划使用两颗100KΩ电阻并联接地。

第16脚直接接地。

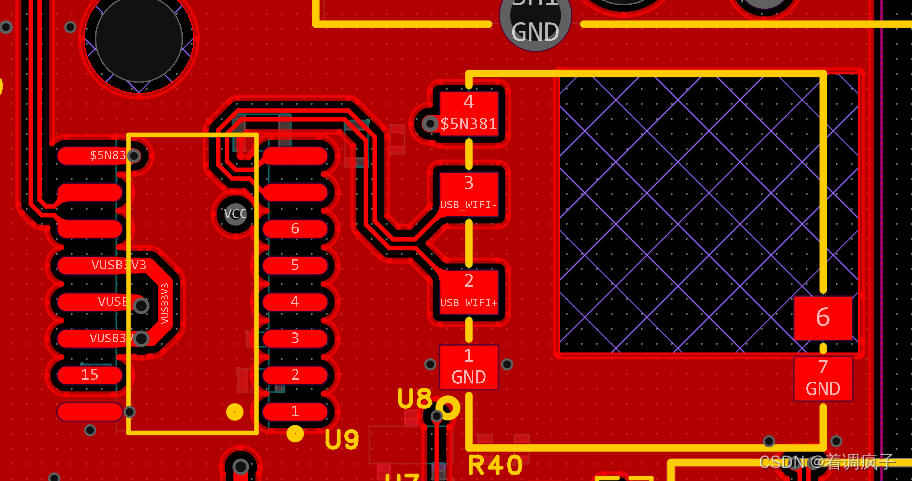

USB差分线的Layout

USB数据线全程采用差分布线,本设计中使用的是线径6mil,线距6mil的阻抗控制。从V3S的USB_D+/-到HS8836A的DP/DM,采用等长差分线,长度差不超过1%;从HS8836A的DP1/DM1到WIFI模块的DP/DM,长度差不超过2mil。

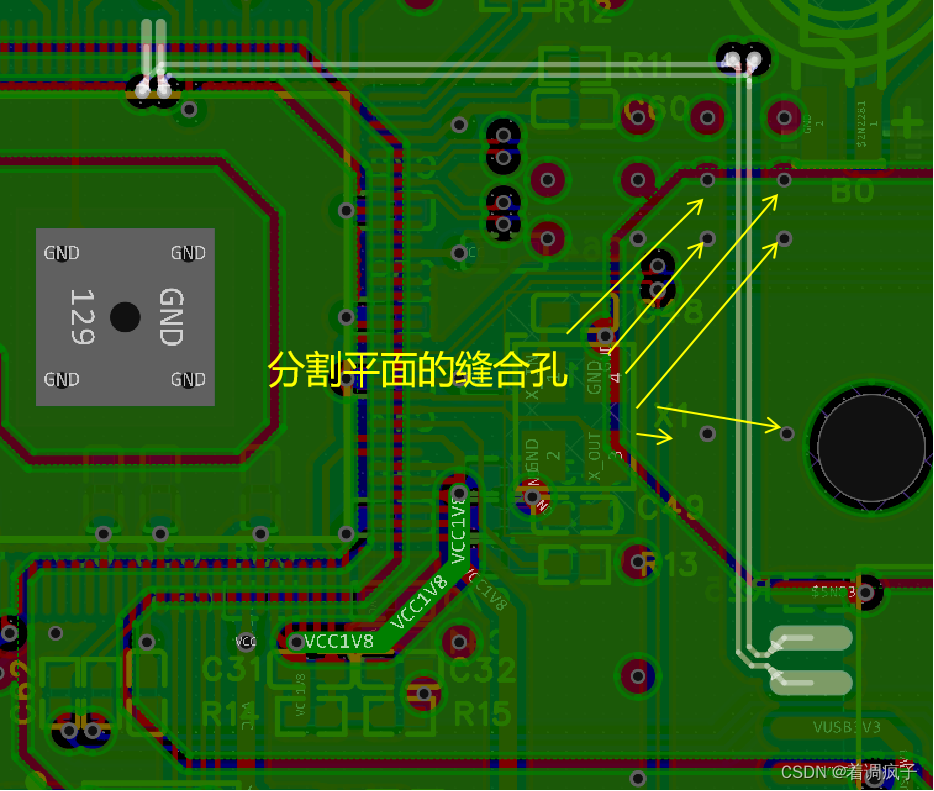

本设计中V3S到HS8836A的USB数据线经过了一次换面,在地层(第2层)中没有平面分割,电源层(第3层)上存在平面分割,在分割平面处,增加了缝合过孔,确保回流路径最短。实测中没有发现对USB传输速率的影响。

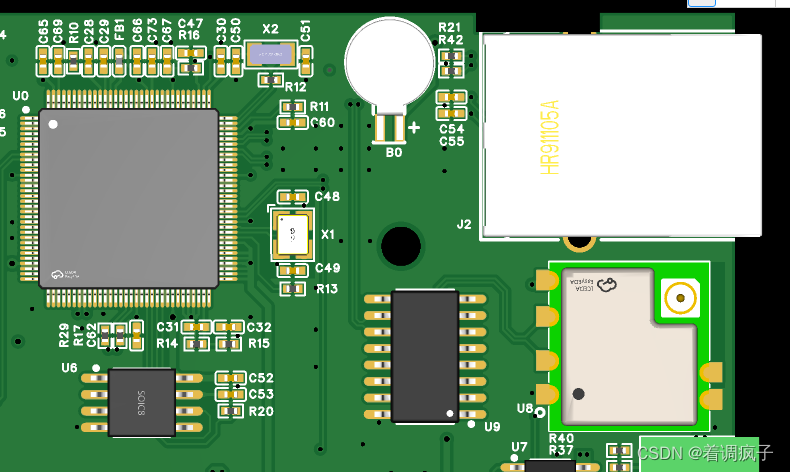

效果图

测试验证

按照上述设计,打板,上电运行,HS8836A即插即用,顺利驱动起来;WIFI模块的ko也被正确insmod,使用iwconfig可以正确地得到wlan0端口。使用wpa_applicant配置无线网卡后,无线模块可以顺利上网。

适配了天线,室内现场测试,iperf可以打到50Mbps左右,在正常范围。

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?