一、概述

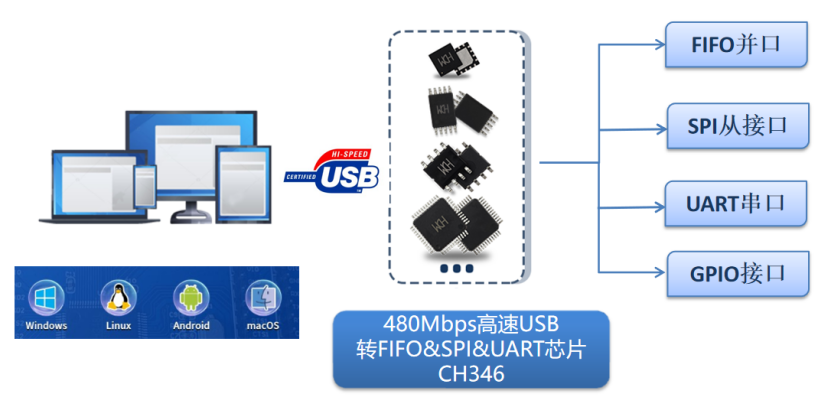

CH346是一款480Mbps高速USB2.0的接口转换芯片,实现USB转高速FIFO并口、2路全功能高速异步串口、高速SPI同步串行接口,FIFO并口传输速度可达每秒30M字节以上, SPI接口时钟频率支持40MHz,串口最高波特率支持15Mbps。芯片提供3种工作模式,可支持其中一种或两种接口,需根据实际的应用需要灵活选用。

芯片内部高度集成,外围精简,提供VIO电源引脚,FIFO并口、串口和SPI接口I/O均支持独立供电,支持3.3V、2.5V和1.8V的电源电压。芯片端采用480Mbps的高速USB接口,用以满足高速FIFO并口、高速15Mbps串口和40MHz的SPI接口的大数据高效传输,全速USB接口总线速率仅12Mbps,在连续数据传输以及数据收发实时性上会大打折扣。

芯片的USB转串口接口,支持使用系统集成的CDC串口驱动或VCP厂商驱动。VCP厂商驱动的功能更齐全,支持全功能串口、硬件流控、GPIO、USB参数配置等功能、支持SPI和串口的高速率下持续稳定传输。推荐使用VCP驱动程序,支持Windows、Linux、Android、macOS等操作系统。

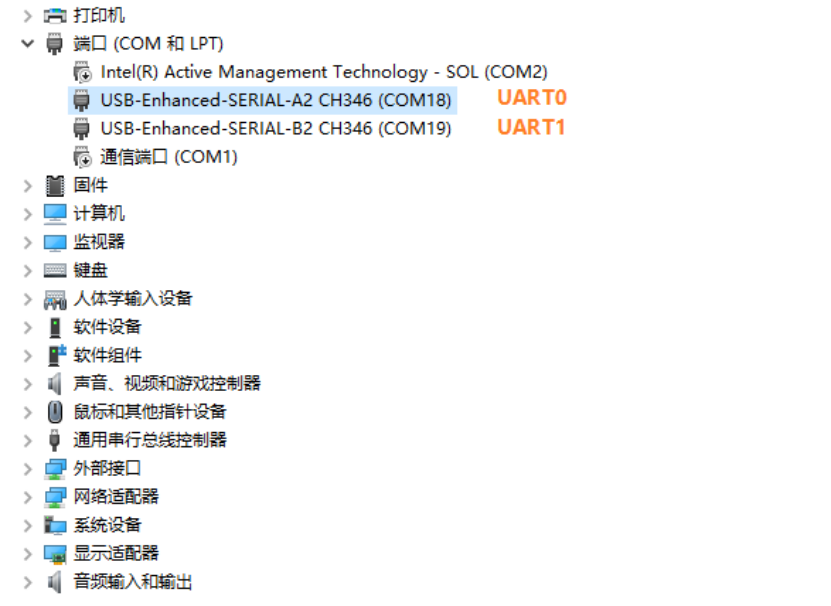

用户在系统端以虚拟串口的形式来访问芯片的串口接口,如:Windows上以COM口形式出现,Linux上以/dev/tty*形式出现。用户端仅需要了解串口编程或使用通用的系统端串口调试软件即可轻松实现对串口的读写操作。如下图所示,CH346工作在双串口模式下Windows操作系统会生成2个COM口供通讯使用,并且“Ch A”对应芯片串口通道0,“Ch B”对应芯片串口通道1。

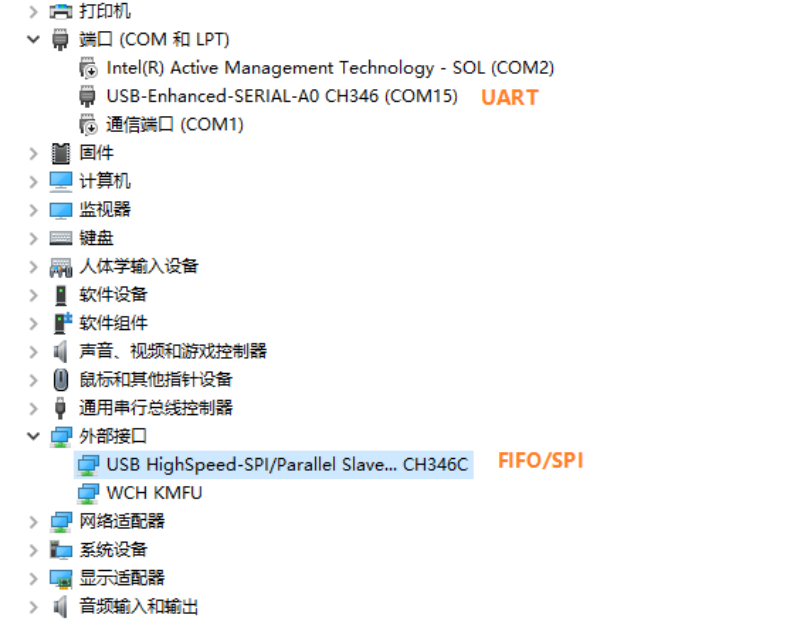

芯片的USB转FIFO和SPI接口需要配合厂商高速接口驱动与软件接口库使用,用户可使用此接口库开发应用软件,驱动与接口库同样支持Windows、Linux、Android、macOS等操作系统。如下图所示,接入Windows操作系统时串口和FIFO/SPI接口会分别对应一个虚拟COM口和专用外部接口供通讯使用。

二、工作原理

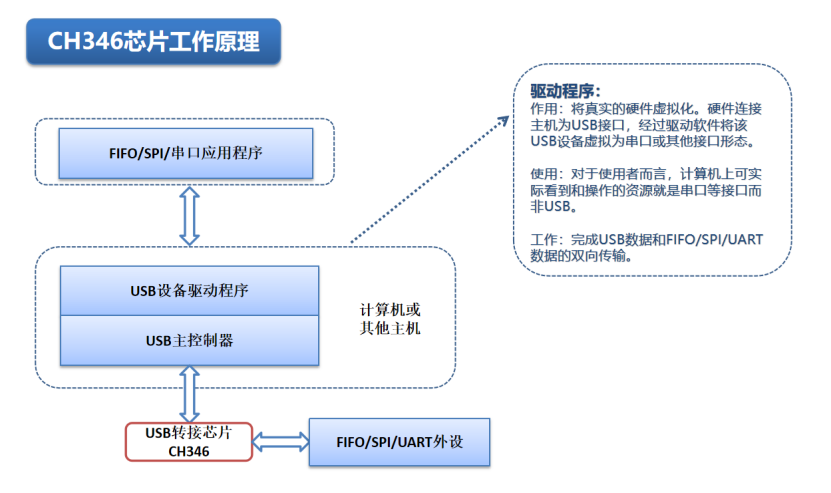

USB主机检测到CH3346设备插入后,首先会对设备复位,然后开始USB枚举过程。USB枚举时过程会获取设备描述符、配置描述符、接口描述符等。描述符中会包含USB设备的厂商ID,设备ID和Class类别等信息。操作系统会根据该信息为设备匹配相应的USB设备驱动。

USB虚拟串口以及FIFO/SPI专用接口的实现在系统上依赖于USB设备接口驱动,驱动主要分为2个功能,其一注册USB设备驱动,完成对USB设备的控制与数据通讯,其二注册串口或接口驱动,为应用层提供相应的实现方法。

发送数据流向

应用程序发送数据->USB设备驱动获取数据->驱动将数据经过USB通道发送给USB接口芯片CH346->CH346接收到数据通过FIFO/SPI/串口发送到外设

接收数据流向

CH346接收外设发送的FIFO/SPI/串口数据->将数据经过USB打包后上传给USB主机->USB设备驱动获取到通过USB上传的接口数据->驱动将数据保存在接口缓冲区提供给应用程序读取

三、通信接口描述

1、FIFO接口

| 功能 | 描述 |

| 通讯角色 | Slave从机 |

| 通讯带宽 | 30MByte/S↑ |

| 收发FIFO | 接收8K字节,发送8K字节 |

| FIFO信号线 | 数据线:D0-D7 数据控制线:CS、RD、WR、A0 数据流控线:RDNE、WRNF |

2、SPI接口

| 功能 | 描述 |

| SPI角色 | Slave从机 |

| 最高时钟频率 | 40MHz |

| SPI模式支持 | 模式0/3 |

| 收发FIFO | 接收12K字节,发送12K字节 |

| SPI信号线 | 信号线:SCS、SCK、MOSI/SDI、MISO/SDO 数据控制线:SPI_RWS 数据流控线:SPI_RDNE、SPI_WRNF |

3、UART串口

| 功能 | 描述 |

| 最高串口波特率 | 15Mbps |

| 串口数据位 | 5/6/7/8 |

| 串口校验位 | 奇/偶/标志/空白/无校验 |

| 硬件流控 | 支持RTS/CTS |

| 收发FIFO | 接收8K字节,发送4K字节 |

| MODEM信号 | 全功能,支持RTS/CTS/DTR/DSR/RI/DCD |

| RS485收发控制 | 提供串口发送状态指示引脚TNOW,可用于直接控制RS485电平转换芯片的收发方向切换,也可以外接LED用于指示TXD通道的发送状态 |

四、电源设计

芯片有4个电源端分别是VDD5、VDD33、VIO和VDDK,芯片内置3.3V和1.2V的LDO电源调节器。

- VDD5是内部LDO的输入端。

- VDD33是内部3.3V的LDO的输出端,USB收发器电源从该引脚输入。

- VIO是单独的串口和SPI等IO引脚的电源输入。

- VDDK是内部1.2V的LDO输出端,为内核提供电源。

常见问题1—VDD5和VDD33如何连接

- 当VDD5引脚输入5V工作电压(实际上大于3.6V)时,内部LDO工作,VDD33引脚会输出3.3V电源供内核和USB收发器使用。

- 当VDD5引脚输入3.3V工作电压(实际上小于3.6V)时,VDD33引脚需要和VDD5连接,同时输入外部的3.3V工作电压。

VDD5、VDD33、VIO和VDDK引脚均需要外接电源退耦电容,且PCB布局时靠近芯片引脚放置。

VDD33引脚的电容用于USB电源退耦,来改善USB传输过程中的EMI。

常见问题2—VIO如何连接

芯片的VIO引脚用于为串口、SPI信号引脚和其他如RESET引脚提供I/O电源,支持电压范围1.8V~3.3V。

默认情况下VIO引脚应该与芯片所连接的外设采用同一电压,此时双方电压匹配。VIO引脚支持的电压输入范围是线性的,在如上范围内可随意调节。例如,可直接使用芯片实现USB转1.8V串口/SPI接口,USB转2.5V串口/SPI接口,USB转3.3V串口/SPI接口等。

芯片VDD33引脚在芯片5V供电时可以输出3.3V电压,因此使用3.3V串口/SPI接口时,VIO也可以直连VDD33引脚节省一个外部LDO。

常见问题3—电源连接方案

| 供电方案 | 推荐连接 |

| 5V供电模式 | VDD5:外部输入5V,可直接从USB口的VBUS取电 VDD33:外接4.7~10uF并联0.1uF VIO:短接VDD33或外部输入其他电源,同时外接0.1~1uF退耦电容 VDDK:连接1uF退耦电容 |

| 3.3V供电模式 | VDD5:外部输入3.3V,同时外接4.7~10uF并联0.1uF VDD33:短接VDD5,同时外接4.7~10uF并联0.1uF VIO:短接VDD5/VDD33或外部输入其他电源,同时连接0.1~1uF退耦电容 VDDK:连接1uF退耦电容 |

五、串口接口设计

芯片的串口引脚包含数据传输引脚和MODEM信号引脚。数据传输引脚包括:串口数据发送引脚TXD、串口数据接收引脚RXD。MODEM信号引脚包括:RTS、CTS、DTR、DSR、RI、DCD。

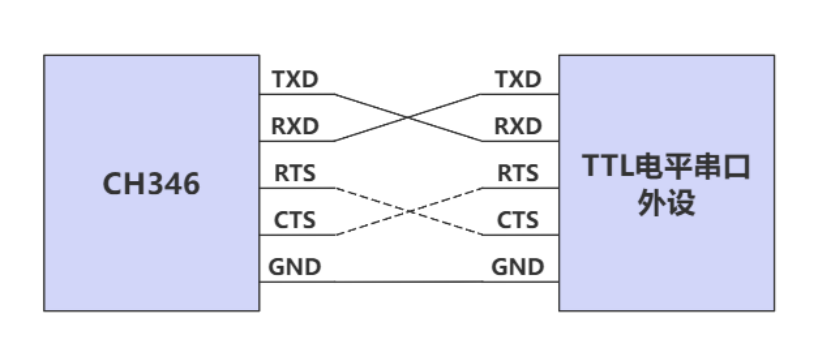

常见问题1-CMOS/TTL串口设计

常规情况下使用CMOS/TTL串口通讯,仅需要使用TXD和RX信号即可,部分场合需要硬件流控功能时还需要使用RTS和CTS信号。其余MODEM信号引脚若使用不到可直接悬空处理。

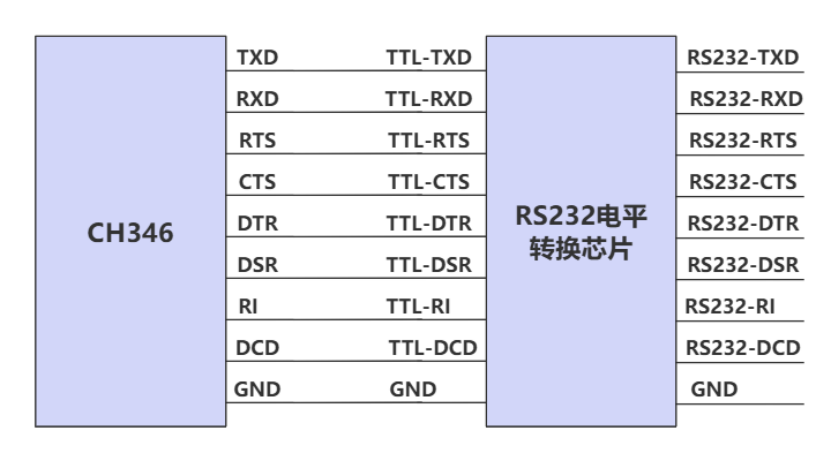

常见问题2-RS232串口设计

USB转串口芯片配合RS232电平转换芯片组合使用可以实现全MODEM信号的RS232串口,也可以仅使用部分串口信号实现简版RS232串口,和CMOS/TTL类似,不使用的信号悬空处理。

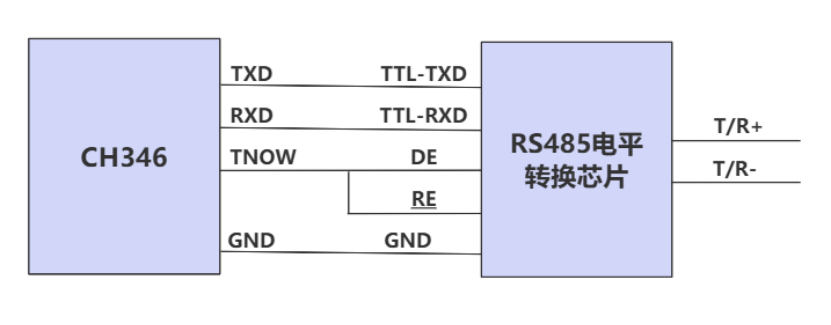

常见问题3-RS485串口设计

使用提供TNOW信号的芯片型号配合RS485电平转换芯片可以实现RS485串口通信,RS485收发转换芯片需要单独进行收发方向控制,TNOW用于该方向的控制,线路上TNOW直连RS485收发器的发送使能DE和接收使能RE即可。

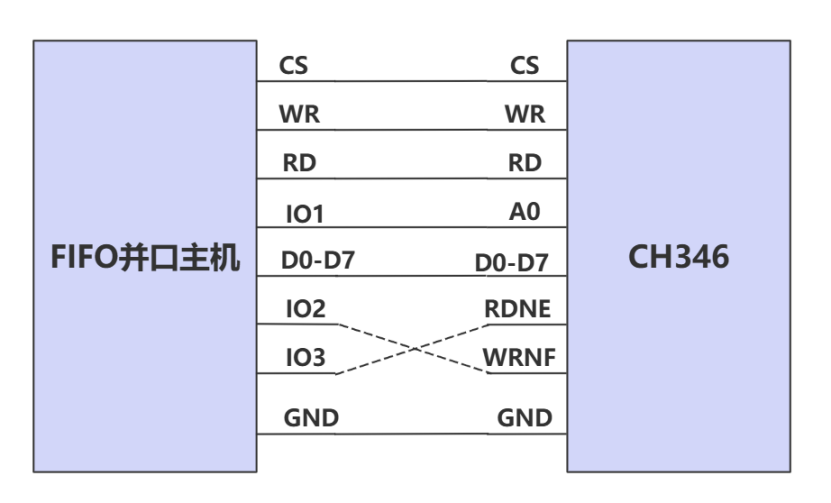

六、FIFO并口设计

芯片的FIFO并口接口引脚包含数据传输引脚、数据控制引脚和数据流控引脚。

数据传输引脚包括:D0-D7,8位总线传输。

数据控制引脚包括:并口片选引脚,并口读和写控制引脚,并口命令/数据选择引脚。

数据流控引脚包括:并口读FIFO状态输出RDNE、并口写FIFO状态输出WRNF。

连接示意图:

| FIFO信号线 | 描述 |

| CS | 片选信号线,由FIFO主机控制,芯片被动响应 |

| WR | FIFO并口写控制信号线,由FIFO主机控制,芯片被动响应 |

| RD | FIFO并口读控制信号线,由FIFO主机控制,芯片被动响应 |

| A0 | 由FIFO主机控制,芯片被动响应 芯片命令/数据选择切换引脚,由FIFO主机控制。 低电平:表示D0-D7需要传输数据 高电平:表示D0-D7需要传输命令码AA或BB |

| D0-D7 | FIFO数据发送与接收信号线 写模式:由FIFO主机发送给芯片,即:芯片端先通过D0-D7信号线接收FIFO主机发送的数据包,然后通过USB通道上传给计算机端 读模式:由芯片返回/发送给FIFO主机,即:计算机端通过USB通道发送数据包,芯片端接收后,通过D0-D7信号线发送 |

| RDNE | FIFO并口读数据FIFO非空状态输出,配合芯片读模式使用。低电平:发送FIFO有数据可以读取。高电平:发送FIFO无数据可以读取 |

| WRNF | FIFO并口写数据FIFO非满状态输出,配合芯片写模式使用。低电平:接收FIFO有空间可以接收数据。高电平:接收FIFO无空间可以接收数据 |

常见问题1-FIFO并口信号线的使用

常规情况下建议使用上所有的并口相关引脚,即:8根数据传输信号线,4根数据控制信号线和2根数据流控信号线,流控信号线 RDNE和WRNF是可选引脚,功能可类比串口信号的RTS/CTS硬件流控脚,用于保证USB主机和FIFO主机两侧数据收发的完整性。如FIFO主机侧资源有限,则只能省略RDNE和WRNF信号脚,其余信号脚连接不可省。

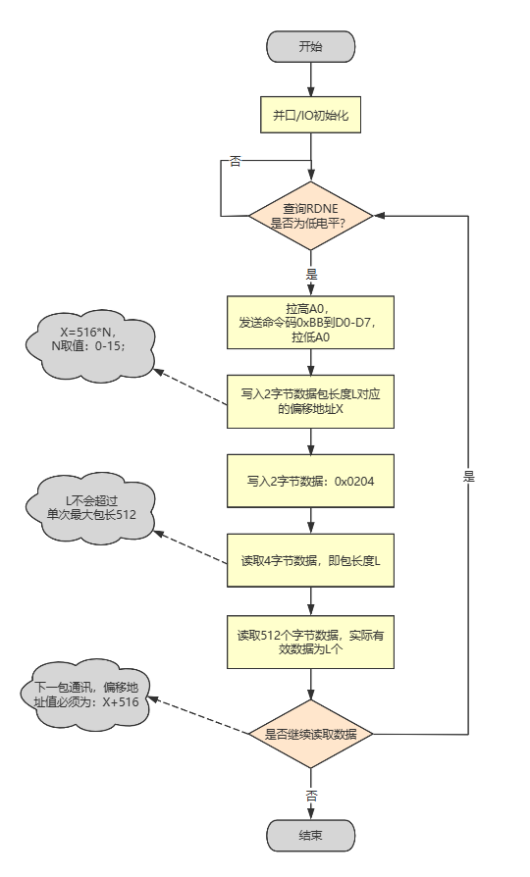

常见问题2-FIFO数据读写流程

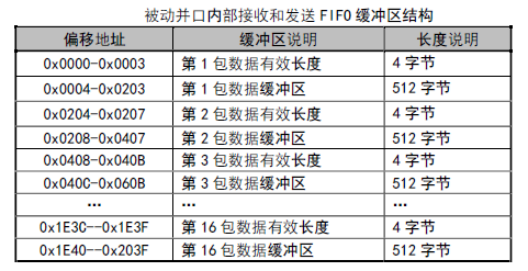

FIFO写模式和读模式是相对于FIFO主机而言,如下从FIFO主机侧展示数据读写流程。芯片内部收发FIFO缓冲区结构如下:

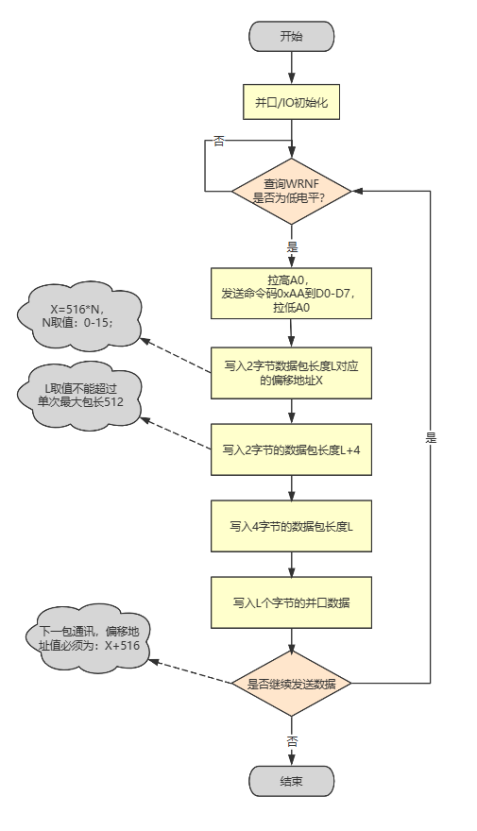

FIFO写模式流程

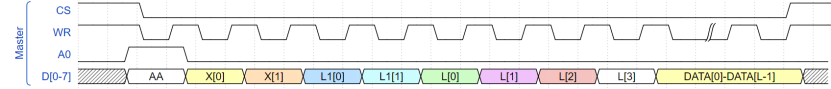

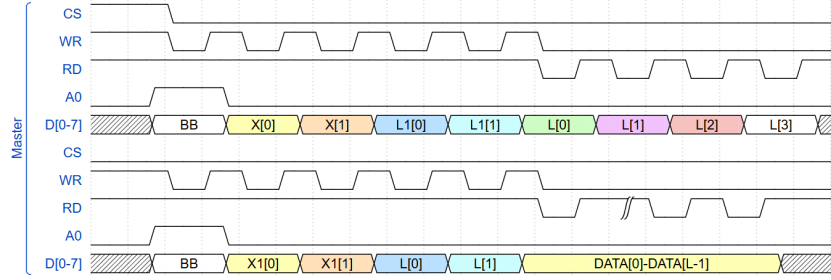

写模式时序示意图如下:

X=516*N,N为包序号,有效范围:0-15;

L为本次要写入的数据包长度,L[0]为L的低字节;

L1为本次数据包长度L,再加上4字节长度字段,即:L1=L+4。L1[0]为L1的低字节;

DATA[0]~DATA[L-1]为L个字节的目标数据;

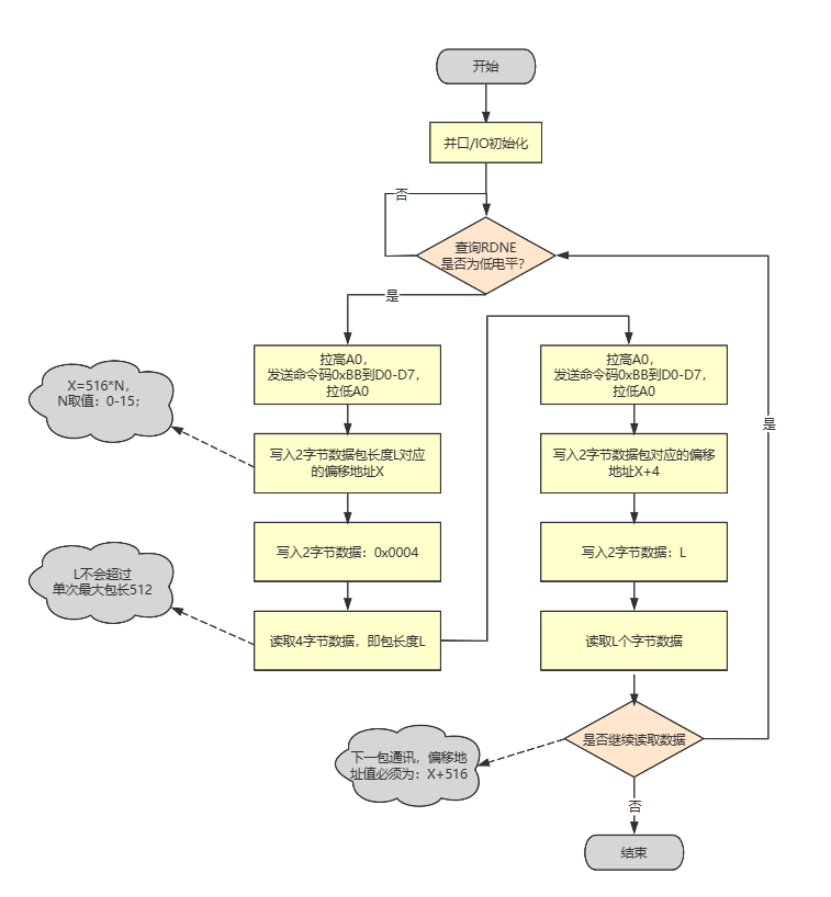

FIFO读模式流程

针对读模式,芯片支持2种方式的FIFO数据读取。

方式1

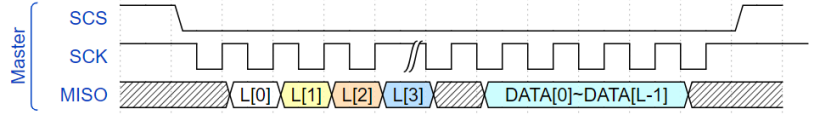

时序示意图如下:

X=516*N,N为包序号,有效范围:0-15;

L1为固定长度:0x0004;

L为从芯片读取的4字节数据包长度,即:L[0]~L[3],L[0]为L的低字节;

X1为此过程中第二次写入的偏移地址,即:X1=X+4。X1[0]为X1的低字节;

DATA[0]~DATA[L-1]为L个字节的目标数据;

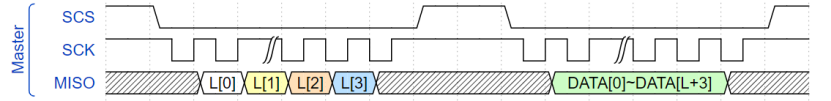

方式2

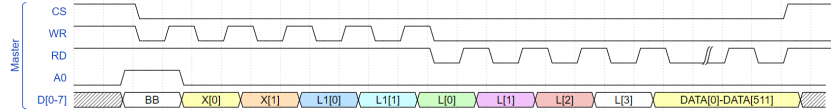

时序示意图如下:

此方式下为一次性读取,时序上更简单,大包连续传输效率更高。

X=516*N,N为包序号,有效范围:0-15;

L1为固定长度:0x0204;

L为从芯片读取的4字节数据包长度,即:L[0]~L[3],L[0]为L的低字节;

X1为此过程中第二次写入的偏移地址,即:X1=X+4。X1[0]为X1的低字节;

DATA[0]~DATA[L-1]为L个字节的目标数据;

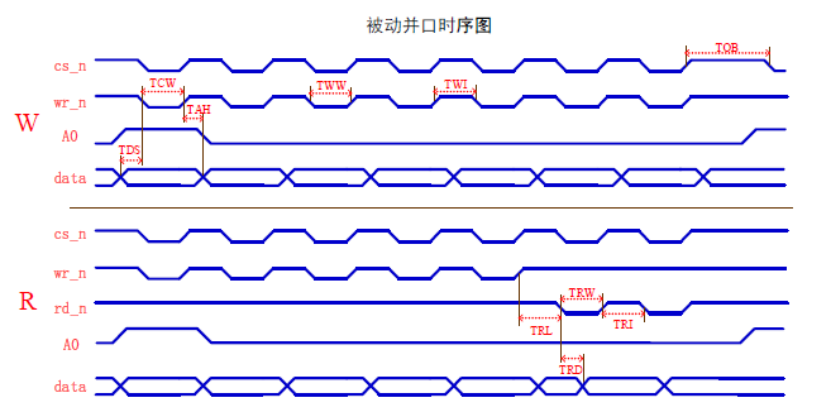

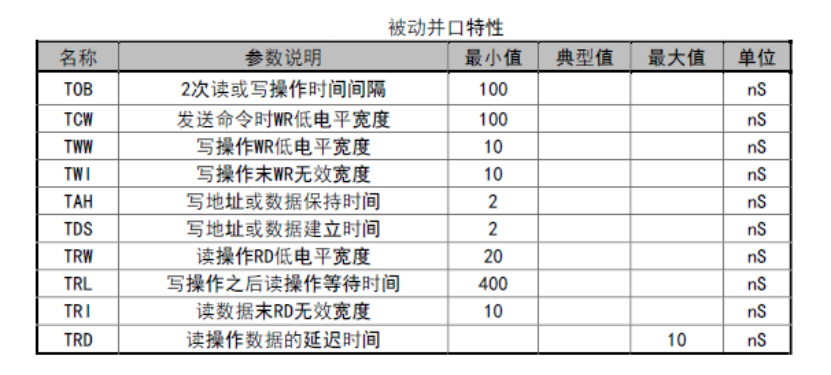

常见问题3-FIFO接口时序图

七、SPI接口设计

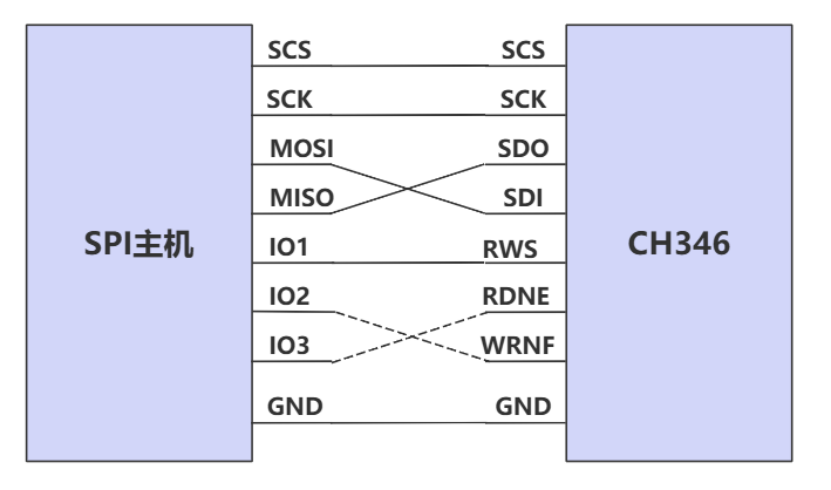

芯片的SPI接口引脚包含数据传输引脚和读写控制引脚。

数据传输引脚包括:SPI从机数据发送引脚MISO/SDO、SPI从机数据接收引脚MOSI/SDI、SPI从机片选信号线SCS、SPI从机时钟信号线SCK。

读写控制引脚包括:SPI从机读写方向控制引脚RWS、SPI从机读FIFO状态输出RDNE、SPI从机写FIFO状态输出WRNF。

连接示意图:

| SPI信号线 | 描述 |

| SCS | SPI片选信号线,由SPI主机控制,芯片被动响应 |

| SCK | SPI时钟信号线,由SPI主机控制,芯片被动响应 |

| MISO/SDO | SPI从机数据发送,由芯片发送给SPI主机,即:计算机端通过USB通道发送数据包,芯片端接收后,通过SDO信号线发送 |

| MOSI/SDI | SPI从机数据接收,由SPI主机发送给芯片,即:芯片端先通过SDI信号线接收SPI主机发送的数据包,然后通过USB通道上传给计算机端 |

| RWS | 芯片读写模式切换引脚,由SPI主机控制。 高电平:CH346切换为写模式,即芯片通过SDI接收数据包然后通过USB通道上传给计算机端。 低电平:CH346C切换为读模式,即芯片将计算机端通过USB通道下传的数据,通过SDO发送给SPI主机 |

| RDNE | SPI接口读数据FIFO非空状态输出,配合芯片读模式使用。低电平:发送FIFO有数据可以读取。高电平:发送FIFO无数据可以读取 |

| WRNF | SPI接口写数据FIFO非满状态输出,配合芯片写模式使用。低电平:接收FIFO有空间可以接收数据。高电平:接收FIFO无空间可以接收数据 |

本文所提及的SPI接口特性与SPI主机端操作方法同样适用于特性相近的USB转FIFO/SPI/串口芯片CH9111。

常见问题1-SPI信号线的使用

常规情况下建议使用上所有的SPI相关引脚,即:4根数据传输脚和3根读写控制引脚,控制信号引脚的RDNE和WRNF是可选引脚,功能可类比串口信号的RTS/CTS硬件流控脚,用于保证USB主机和SPI主机两侧数据收发的完整性。如SPI主机侧资源有限,则可以省略RDNE和WRNF信号脚,其余5根信号脚连接不可省。

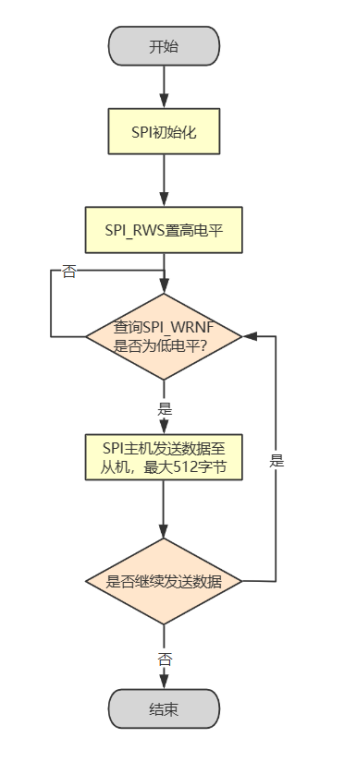

常见问题2-SPI数据读写流程

SPI写模式和读模式是相对于SPI主机而言,如下从SPI主机侧展示数据读写流程。

SPI写模式流程

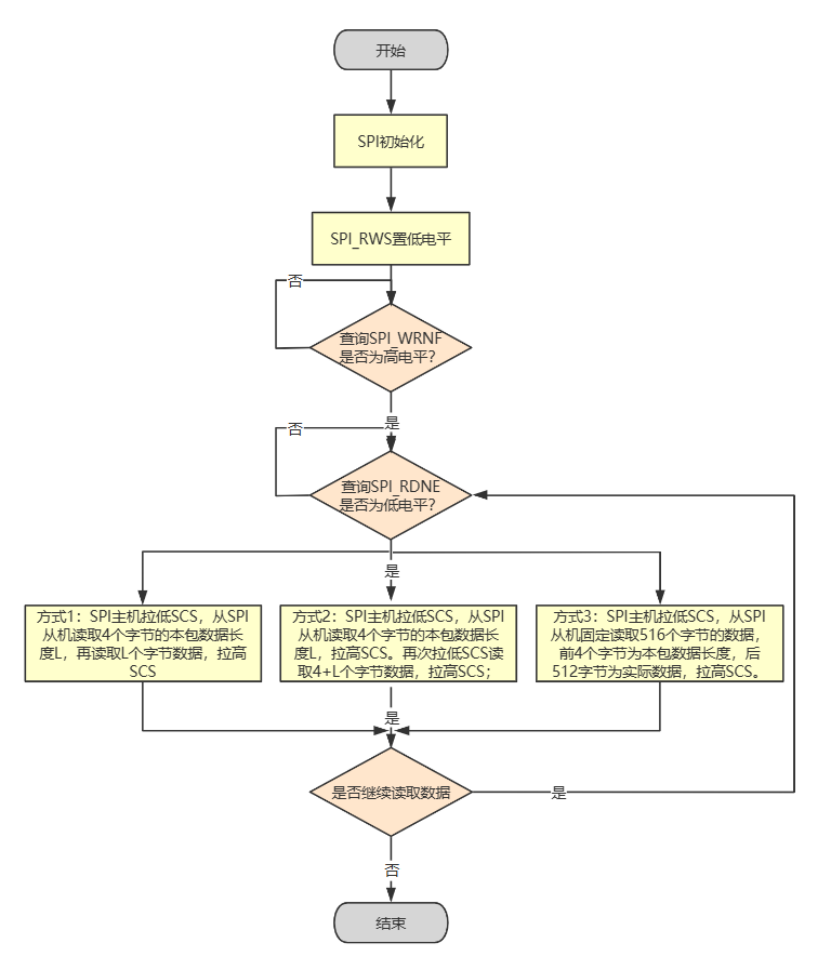

SPI读模式流程

针对读模式,芯片支持3种方式的SPI数据读取。时序示意图如下:

方式1

L为4字节的数据包长度,L[0]为L的低字节。

方式2

L为4字节的数据包长度,L[0]为L的低字节。

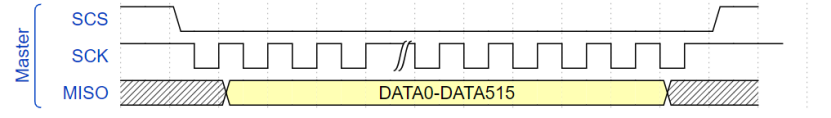

方式3

一次性读取516字节,DATA0~DATA3为实际有效长度L。

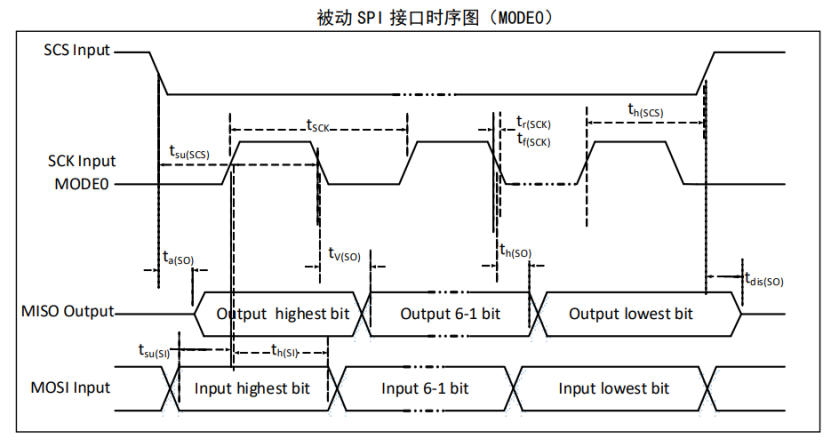

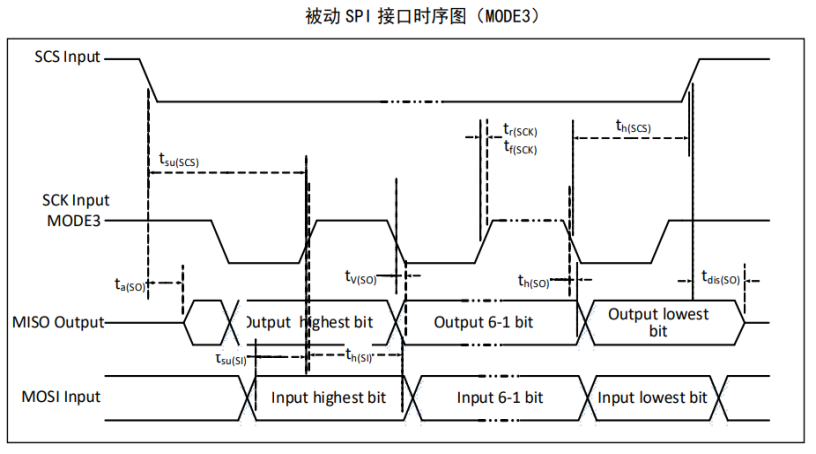

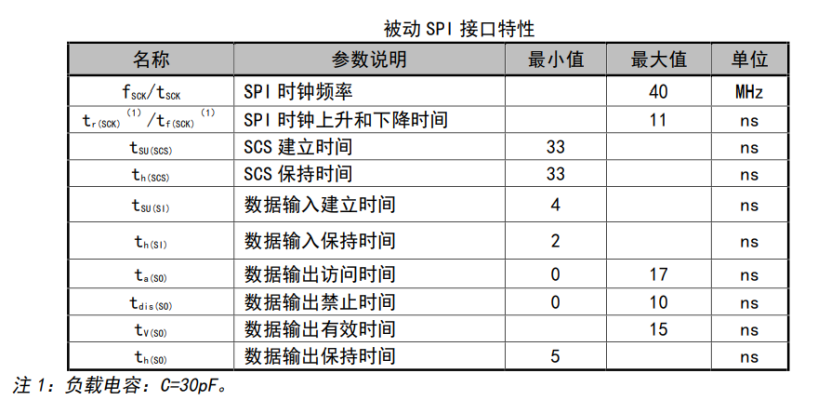

常见问题3-SPI接口时序图

八、其他辅助引脚说明

ACT和SUSP引脚说明

芯片的ACT引脚为USB设备配置完成状态输出(当芯片接收到主机的设置配置请求并操作完成时会输出低电平,默认该引脚上电为高电平),该引脚可用作芯片的USB工作状态指示,也可以用于通知MCU等串口设备USB转串口芯片的工作状态。也可以用于控制后级电路的电源通断,如USB转RS232串口应用,当计算机睡眠ACT输出无效电平可用于控制RS232电平转换芯片关断电源以节约功耗。

芯片的SUSP引脚为USB设备挂起状态输出,当芯片处于USB正常通信的情况下,该引脚输出高电平,当处于给芯片正常供电但USB不通信的情况下:如操作系统进入睡眠状态或者芯片使用外供电方式但USB未连接主机,此时输出低电平。使用一般与ACT引脚相反。

GPIO引脚说明

芯片提供了14路GPIO引脚,任意一路GPIO均支持独立的IO输出和输入控制。该功能的使用需要与计算机端厂商驱动程序和应用软件配合使用。因GPIO与芯片的其他功能存在复用关系,芯片上电后相关复用引脚均默认工作在其他功能/模式下,仅当计算机软件端主动使能开启GPIO功能后相关引脚才工作在GPIO功能/模式下。

九、资料下载链接

| No. | 资料 | 文件名 | |

| 1 | 芯片手册 | CH346DS1.PDF | |

| 2 | 参考设计 | CH346EVT.ZIP | |

| 3 | 串口驱动 | Windows厂商VCP驱动一键安装包 | CH343SER.EXE |

| 4 | Windows厂商VCP驱动 | CH343SER.ZIP | |

| 5 | Android免驱应用库和程序 | CH341SER_ANDROID.ZIP | |

| 6 | macOS厂商VCP驱动 | CH341SER_MAC.ZIP | |

| 7 | Linux驱动 | 请发邮件至tech@wch.cn 获取 | |

| 8 | FIFO/SPI驱动 | Windows厂商驱动一键安装包 | CH346DRV.EXE |

| 9 | Windows厂商驱动 | CH346DRV.ZIP | |

| 10 | Windows应用库和程序 | CH346EVT.ZIP | |

| 11 | Android免驱应用库和程序 | CH341PAR_ANDROID | |

| 12 | macOS免驱应用库和程序 | CH341PAR_MAC | |

| 13 | Linux驱动、应用库和程序 | CH341PAR_LINUX | |

| 14 | 工具和软件 | 芯片配置工具 | CH34xSerCfg.ZIP |

| 15 | 串口调试工具 | COMTransmit.ZIP | |

| 16 | 串口号批量管理工具 | ComPortManager.ZIP | |

更多USB转接芯片选型请参考:USB转串口芯片选型 - 南京沁恒微电子股份有限公司

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?