转自:http://blog.csdn.net/yihui8/article/details/54316888

SPI四种模式区别

CPHA --> Clock phase (时钟相位)

CPOL --> CLock polarity (时钟极性)

spi四种模式SPI的相位(CPHA)和极性(CPOL)分别可以为0或1,对应的4种组合构成了SPI的4种模式(mode)

Mode 0 CPOL=0, CPHA=0

Mode 1 CPOL=0, CPHA=1

Mode 2 CPOL=1, CPHA=0

Mode 3 CPOL=1, CPHA=1

时钟极性CPOL: 即SPI空闲时,时钟信号SCLK的电平(1:空闲时高电平; 0:空闲时低电平)

时钟相位CPHA: 即SPI在SCLK第几个边沿开始采样(0:第一个边沿开始; 1:第二个边沿开始)

sd卡的spi常用的是mode 0 和mode 3,这两种模式的相同的地方是都在时钟上升沿采样传输数据,区别这两种方式的简单方法就是看空闲时,时钟的电平状态,低电平为mode 0 ,高电平为mode 3。

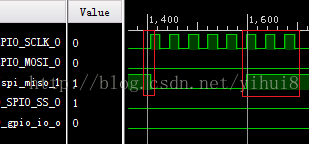

例如这个波形图

(注意红色框)

如果CPOL=0, CPHA=0 ,则miso数据是0x83(10000011)

如果CPOL=0, CPHA=1 ,则miso数据是0x07(00000111)

在用内核自带的linux-kernel/xlnx-4.0/Documentation/spi/spidev_test.c例子,读写内核的spidev.c设备的时候,

/spidev_test -r 69 -w 7

写入地址69寄存器,数值7

./spidev_test -r 69

读出地址69寄存器数值:0x83,以为程序代码有bug

./spidev_test -H -r 69

读出地址69寄存器数值:0x07,应该在SCLK第2个边沿开始采样(带H参数表示CPOL=0, CPHA=1),这才读对了。

在调试ad9631时,用默认spi mode读写总返回0x83,以为程序有问题,查查spi mode原理后,再对比波形图,才知道ad9631的mode=1

附我自己修改的程序:应用spidev_test.c,内核驱动spidev.c,设备树devicetree,下载

spidev的移植,参考文章:http://blog.csdn.net/yihui8/article/details/54142351

附加:SPI四种工作模式时序图

3526

3526

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?