-

目录

一:安装

- 软件安装包下载 :可以直接从百度网盘保存 通过百度网盘分享的文件:PADS9.5链接:https://pan.baidu.com/s/1B3R9J_tlOS6VXtco2uFZDA 提取码:1312 也可以从网址中搜索下载 Mentor Pads VX 2.2 Standard Plus 下载 – 吴川斌的博客 (mr-wu.cn);

- 安装教程参考Mentor PADS 9.5下载安装及破解指南 – 吴川斌的博客 (mr-wu.cn);Mentor PADS9.5全程入门安装视频教程_哔哩哔哩_bilibili;pads9.5安装_哔哩哔哩_bilibili参照这三个视频基本就没什么问题了。

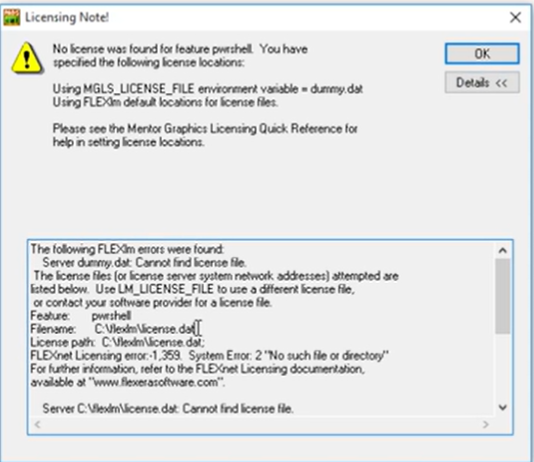

- 安装问题主要汇总:开始的时候我参照的是凡亿的安装视频,破解工具大同小异,但是在找环境变量时我的C盘中没有,直接运行PADS Logic,会有一个提示如下 图1:

无法在C盘下找到这个文件,此时直接将刚刚生成的licese文件更改文件格式重新命名到提示的文件夹中,这样就能运行了。

图1

二:使用(器件库创建)

PADS 9.5安装成功后会有三个快捷界面,分别为

。这里主要说一下和AD使用的区别。在AD中一个工程由原理图和PCB图两部分组成;一个器件也由原理sch和封装footprint两部分组成。在PADS中一个工程由原理图和PCB图两部分组成;一个器件由logic 、decal 和part组成一个器件。

。这里主要说一下和AD使用的区别。在AD中一个工程由原理图和PCB图两部分组成;一个器件也由原理sch和封装footprint两部分组成。在PADS中一个工程由原理图和PCB图两部分组成;一个器件由logic 、decal 和part组成一个器件。

1.Logic 基础使用

Shift+鼠标滚轮左右移动; 直接滚动鼠标上下移动; CTRL+鼠标滚轮放大缩小;

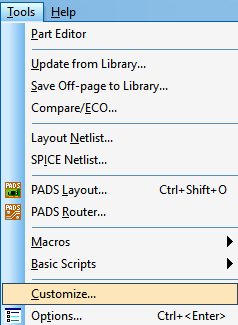

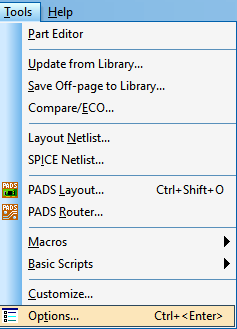

切换语言:tools工具栏下 customize客户定制中进行修改语言;

customize客户定制中进行修改语言;

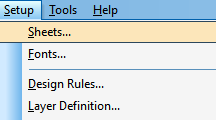

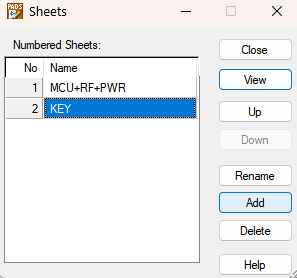

原理图创建分页:

在设置中选择sheets(图页)添加 ;

;

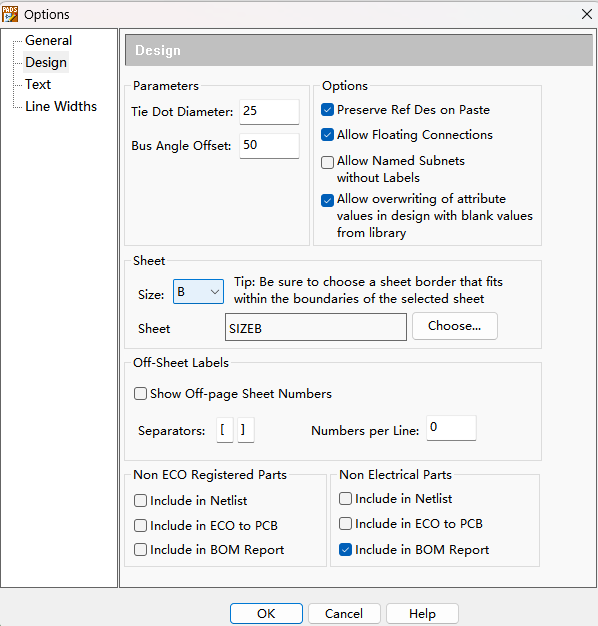

图页型号修改:直接在size中选择,

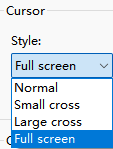

CTRL+@+enter进入设置,修改光标形状

修改原理图模板,需要先拆分线条才能删除,删除之后再组合(拆分:Explode,合并:Combine)

2.logic 显示问题

LOGIC下选项窗口显示不全问题可以参考如下

PADS问题汇总——PADS Logic选项窗口显示不全_pads logic选项菜单显示不全-CSDN博客

修改默认原理图模板

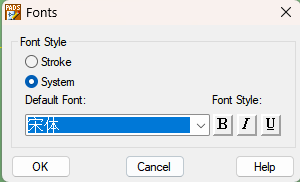

修改默认字体 ,建议修改为汉语字体,这样在添加标注汉语文字时,导出PDF文件时能够正常显示,不会出现乱码。

,建议修改为汉语字体,这样在添加标注汉语文字时,导出PDF文件时能够正常显示,不会出现乱码。

修改原理图背景颜色和器件颜色

3.原理图封装库的创建

一个元件:

CAE Logic下的名称

PCB 布线和布局下的名称

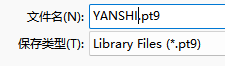

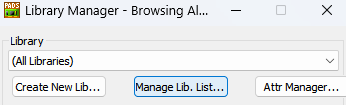

元件创建前要确定元件放置位置——即库

创建库后开始创建logic。

创建库后开始创建logic。

LOGIC 封装创建

(1)准备

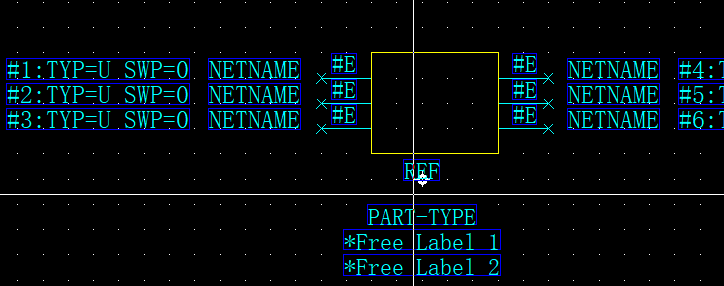

选择NEW创建一个新的Logic之后会弹出新的页面,如下

,

,

使用无膜命令修改显示格点和跳转格点为100mil,UM ;G 100;GD100.(在创建每一个新的Logic时都要修改格点显示和格点跳转的距离,保持一致,这样在绘制原理图放置器件时就能够较为整齐);

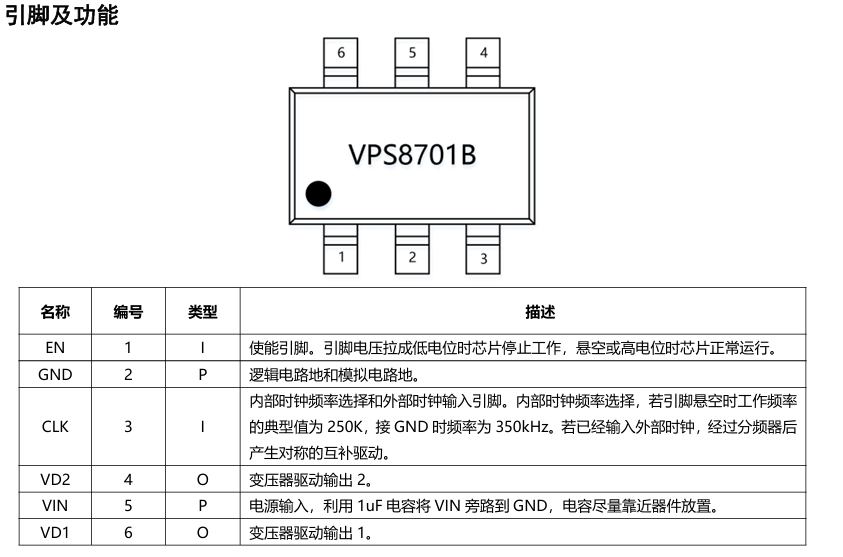

(2)绘制一个器件,我以VPS8701B器件作为示例:

绘制边框:

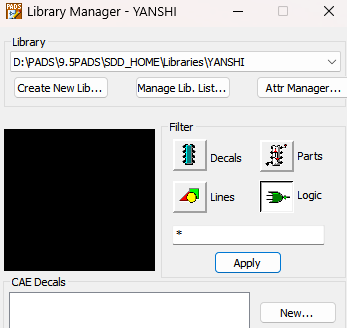

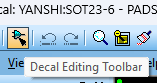

先绘制一个边框,选中菜单栏中的 单击Decal Editing Toolbar后会显示绘制工具菜单

单击Decal Editing Toolbar后会显示绘制工具菜单![]()

再移动光标到铅笔图标会显示Create 2D Line,

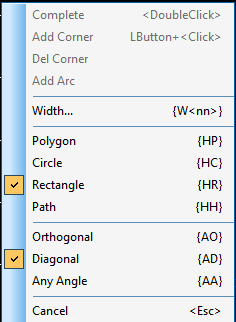

使用该工具绘制2D线,单击选中后,移动到绘制图中会有一个小V的标志,右键点击空白处,根据需要选择,这里我选择的是矩形,正交角度 ;

;

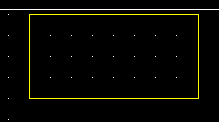

绘制一个矩形框,矩形框的宽度和长度根据器件的引脚数和引脚名称长度来确定,通常小器件我会在上下留一格空白 ,绘制完成矩形框之后就要添加引脚了;

,绘制完成矩形框之后就要添加引脚了;

添加引脚:

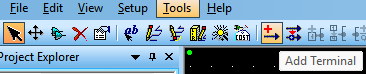

添加引脚,移动光标到![]() 图标会显示Add Terminal

图标会显示Add Terminal

,

,

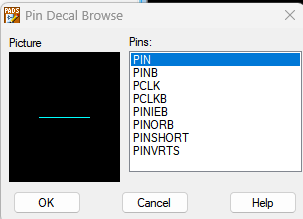

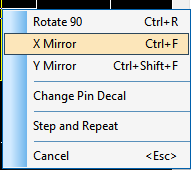

单击左键会弹出一个引脚类型框Pin Decal Browse,根据需要选择,这里默认选择PIN,点击OK后开始添加引脚,在完成左侧引脚添加后,右键单击鼠标选择X mirro在X轴方向反转引脚,绘制余下的右侧引脚。

保存Logic Decal:

保存Logic Decal:

绘制完成后保存Logic Decal ,点击File下的Save,根据提示完成保存。

此处Logic下的CAE Decal 命名可以根据个人习惯进行命名,可以按照器件的名称命名也可以按照器件的PCB封装进行命名,为了方便使用可以将CAE Decal和PCB Decal 统一命名,PARTS命名为器件名称VPS8701B。

Decal 封装绘制

(1)准备

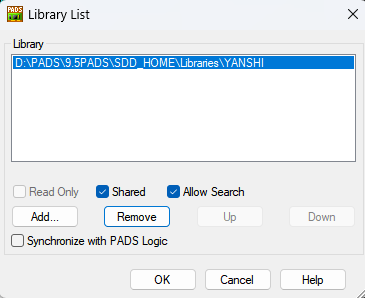

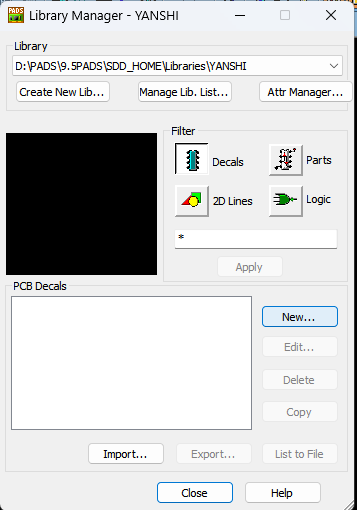

在File 下找到Library 点击左键弹出库管理页面,选择![]() ,将库添加进去后点击OK。

,将库添加进去后点击OK。

选择NEW创建一个新的Decal之后会弹出新的页面,如下

使用无膜命令修改显示格点和跳转格点为0.1MM,UMM ;G 0.1;GD0.1.(在创建每一个新的Decal时都要修改格点显示和格点跳转的距离,保持一致,这样在绘制PCB图放置器件时就能够较为整齐);

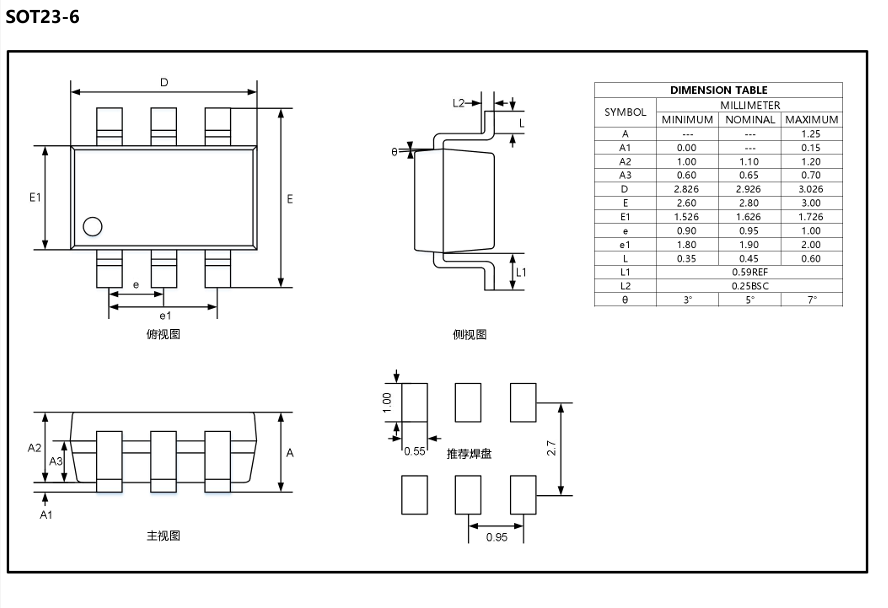

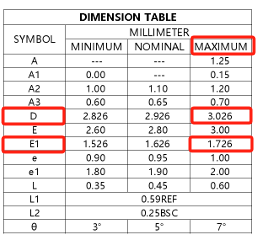

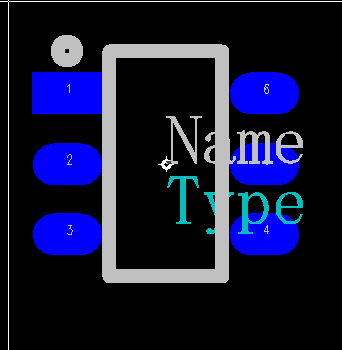

(2)绘制一个器件,我以VPS8701B器件作为示例:

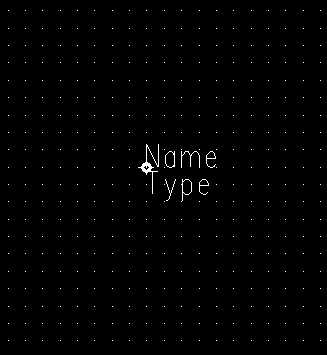

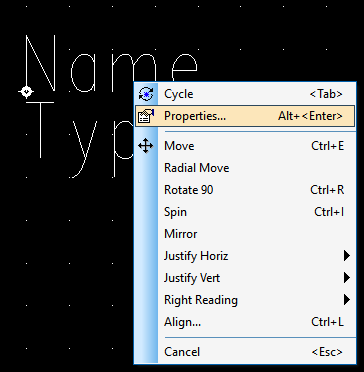

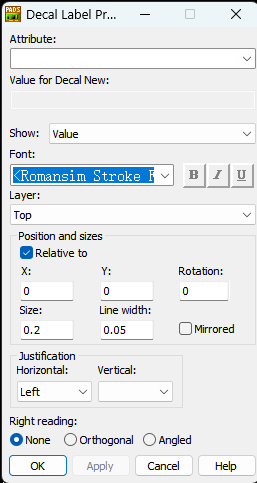

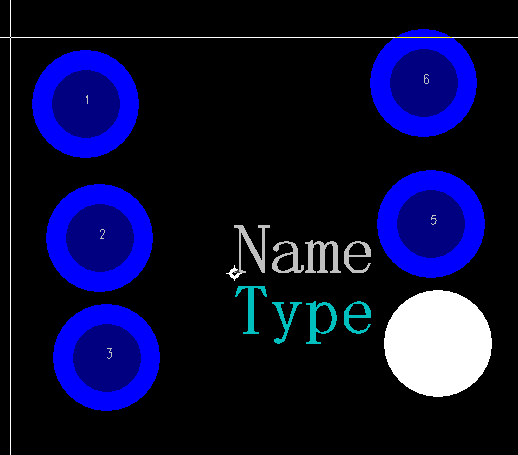

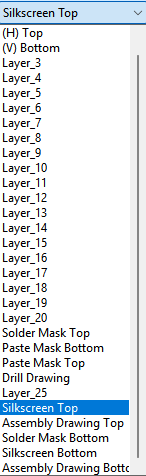

修改字符:

先修改字符所在层和字体大小,选中Name和Type后右键单击鼠标,选中属性Properties.,这里需要修改字体Font根据自己喜欢选择,我这里选择宋体;Size这里根据需要选择,但是生产工艺限制通常选择≥1mm以上的字体,在印刷时候才能显示清晰而不会成为一坨。其他先不管点击OK。然后再单击选择Name,修改所在层Layer为 Silkscreen Top顶层丝印。(这里也可以分别修改Name 和Type,我在绘制PCB中Type我会隐藏掉,所以没有修改Type所在层。)修改完字符之后开始放置焊盘。

添加焊盘:

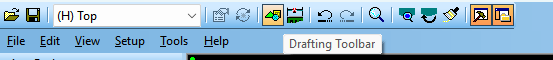

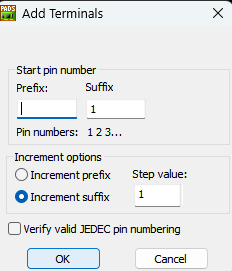

在工具栏中选择绘图工具栏![]() Drafting Toolbar,单击后会出现工具栏,点击焊盘

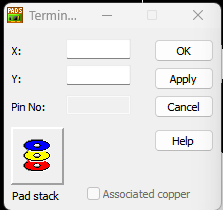

Drafting Toolbar,单击后会出现工具栏,点击焊盘![]() 后会弹出添加焊盘窗口,如果是第一次添加默认不用动,Suffix是指放置的焊盘的数字名称。放置六个焊盘,这里焊盘顺序要参照器件说明书来进行。放置完焊盘后根据器件说明书来修改焊盘大小。

后会弹出添加焊盘窗口,如果是第一次添加默认不用动,Suffix是指放置的焊盘的数字名称。放置六个焊盘,这里焊盘顺序要参照器件说明书来进行。放置完焊盘后根据器件说明书来修改焊盘大小。

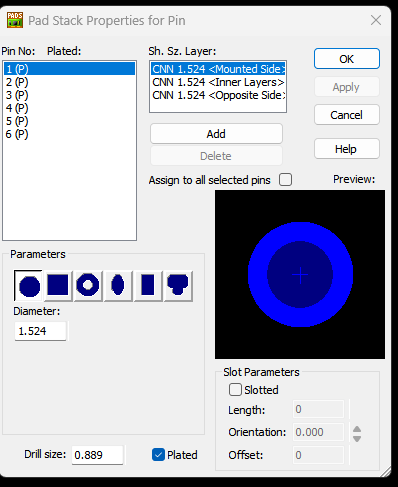

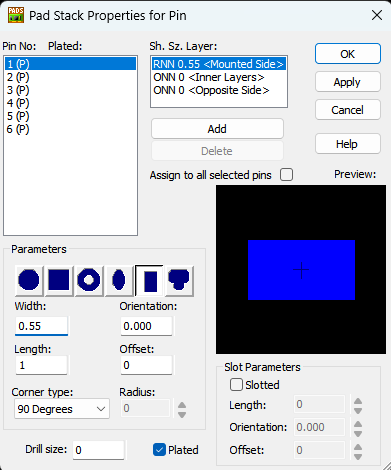

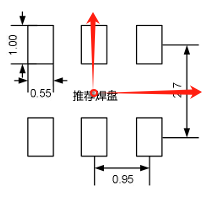

修改焊盘大小:

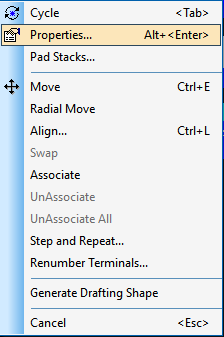

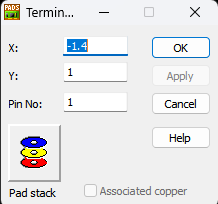

按住Ctrl键,单击各个焊盘选中后,右键点击空白处弹出Termin...会话框后单击Pad stack,弹出Pad Stack Properties for Pin会话框,因为该器件是贴片器件,所以我们使用的层只选择Mounted Side,把剩余的层中的焊盘参数全部给修改为0 0,钻孔(Drill Size)也修改为0。为了区分通常会将第一个焊盘设置为方形,其他焊盘设置为椭圆。参照手册中的推荐焊盘,修改焊盘大小,可以直接按照推荐焊盘进行设计,我会根据习惯修改焊盘为间距为1mm,焊盘大小为1.mm×0.6mm。(这里要根据实际情况确定是否能修改)。完成焊盘大小修改后进行各个焊盘的位置修改,同样参照器件手册说明书中推荐的封装来进行修改,通常以器件的中心为参考点(0.0),单击选中焊盘后,点击鼠标右键,在弹出的会话框中选择属性,会弹出当前焊盘的坐标,修改即可;逐个修改焊盘参数位置即可。完成后给器件添加封装外围丝印。

添加丝印:

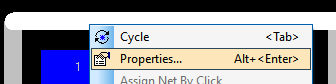

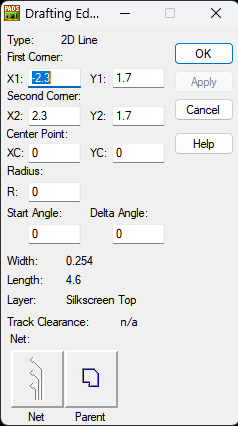

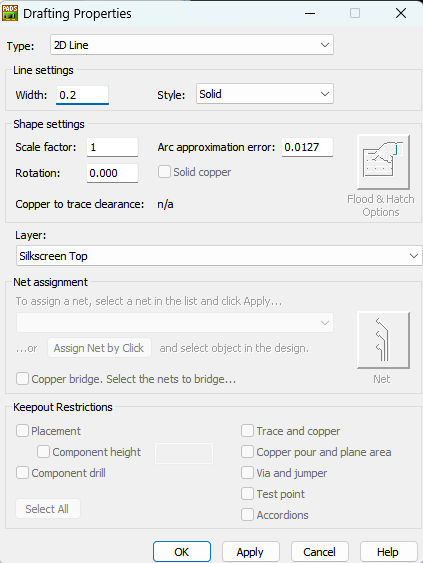

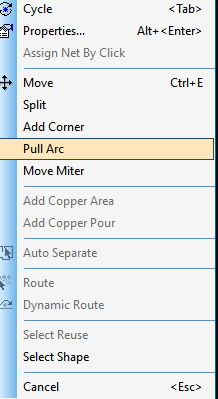

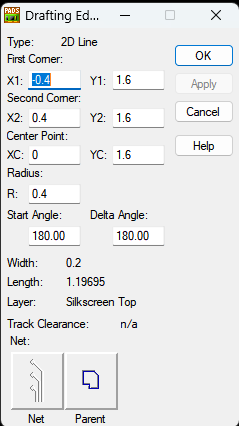

首先将层修改为Silkscreen Top,默认的层为TOP层,修改为Silkscreen Top顶层丝印层之后,选择2D Line![]() 单击鼠标,移动到绘制图中右键点击鼠标选择2D Line线的属性,这里绘制选择为矩形Rectangle,绘制一个矩形框将焊盘都涵盖。完成后调整线宽和丝印的位置。左键点击丝印选中后,右键单击 在弹出的会话框中选择属性Properties...,会弹出Drafting Ed...会话框,我们可以看到这里Width默认的是0.254mm,我们点击Parent 。弹出会话框Drafting Properties,我们根据个人习惯修改线宽,这里也可以修改线段的样式,可线段的所在层。我这里按照我的习惯将线宽修改为0.2mm,实线Solid,顶层丝印Silkscreen Top。修改完后点击应用Apply,点击OK关闭会话框。修改丝印的位置也在Drafting Ed...会话框中,我们根据手册提示找到器件尺寸显示宽度最大为1.726mm,长度最大值为3.028mm,所以我们修改丝印宽度X轴起始为-0.8,终点0.8;Y轴起始为-1.6,终点1.6,完成后丝印位置在器件中间;再添加2D Line选择圆形,放置在1角上方作为标记,标识器件的方向。到此就算完成一个器件的PCB Decal封装了,通常我还会再给它添加一个倒圆弧标识该器件的上下方向,可以根据自己喜好选择是否添加,添加的方式是在上方丝印的位置再绘制一段短线(可以选择丝印的一半来绘制),这里绘制的短线为-0.4到0.4,绘制完成后选中短线右键选择Pull Arc拉弧,完成后点击弧线右键选择属性在弹出的Drafting Ed...会话框中修改弧线的半径为0.4mm(这里也可以根据你的习惯来选择半径长度)。完成绘制之后接下来保存器件。

单击鼠标,移动到绘制图中右键点击鼠标选择2D Line线的属性,这里绘制选择为矩形Rectangle,绘制一个矩形框将焊盘都涵盖。完成后调整线宽和丝印的位置。左键点击丝印选中后,右键单击 在弹出的会话框中选择属性Properties...,会弹出Drafting Ed...会话框,我们可以看到这里Width默认的是0.254mm,我们点击Parent 。弹出会话框Drafting Properties,我们根据个人习惯修改线宽,这里也可以修改线段的样式,可线段的所在层。我这里按照我的习惯将线宽修改为0.2mm,实线Solid,顶层丝印Silkscreen Top。修改完后点击应用Apply,点击OK关闭会话框。修改丝印的位置也在Drafting Ed...会话框中,我们根据手册提示找到器件尺寸显示宽度最大为1.726mm,长度最大值为3.028mm,所以我们修改丝印宽度X轴起始为-0.8,终点0.8;Y轴起始为-1.6,终点1.6,完成后丝印位置在器件中间;再添加2D Line选择圆形,放置在1角上方作为标记,标识器件的方向。到此就算完成一个器件的PCB Decal封装了,通常我还会再给它添加一个倒圆弧标识该器件的上下方向,可以根据自己喜好选择是否添加,添加的方式是在上方丝印的位置再绘制一段短线(可以选择丝印的一半来绘制),这里绘制的短线为-0.4到0.4,绘制完成后选中短线右键选择Pull Arc拉弧,完成后点击弧线右键选择属性在弹出的Drafting Ed...会话框中修改弧线的半径为0.4mm(这里也可以根据你的习惯来选择半径长度)。完成绘制之后接下来保存器件。

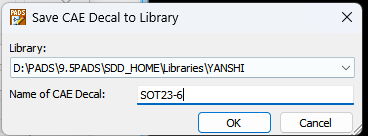

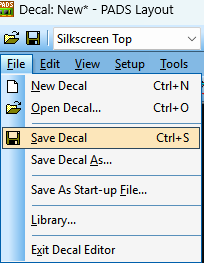

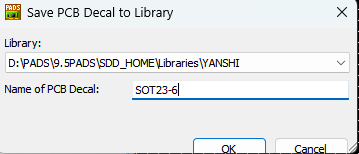

保存封装:

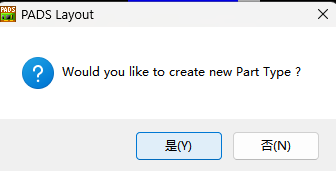

保存PCB Decal和保存Logic Decal的方法一样,在File下点击Save,根据提示完成保存。完成后点击OK即可。接下来创建Part Type,如果不需要创建新的Part Type,直接点击否关闭提示框即可。

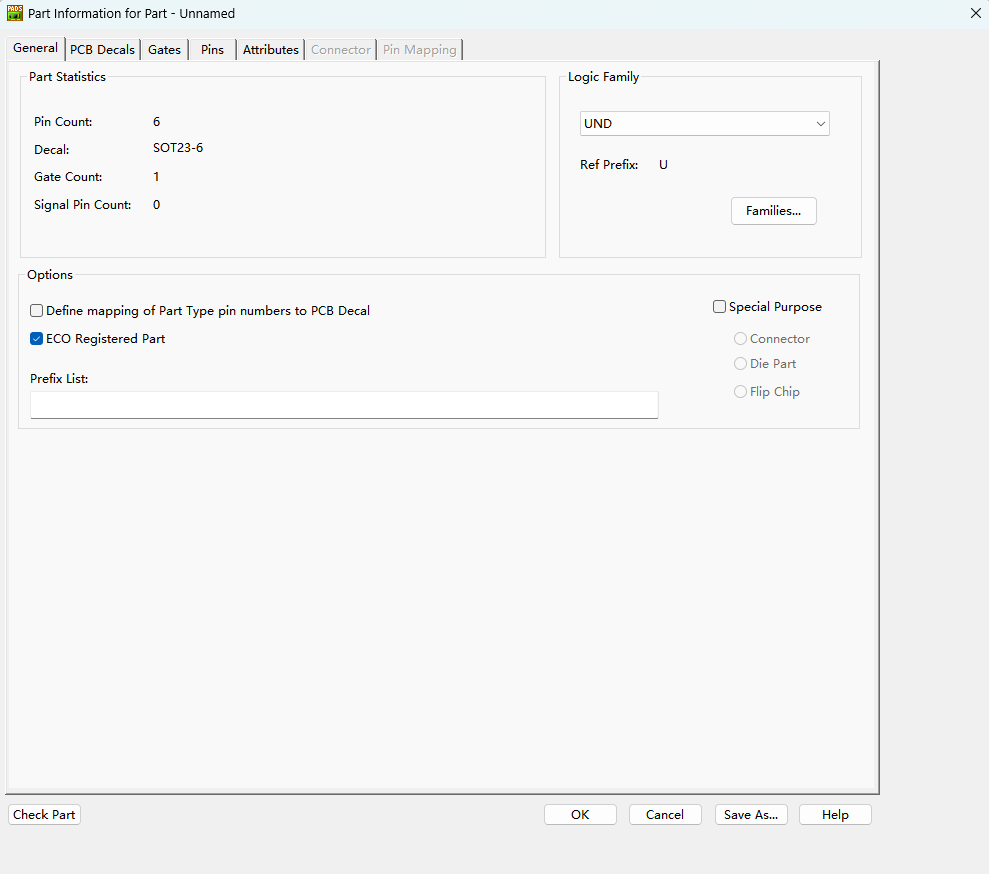

创建Part Type

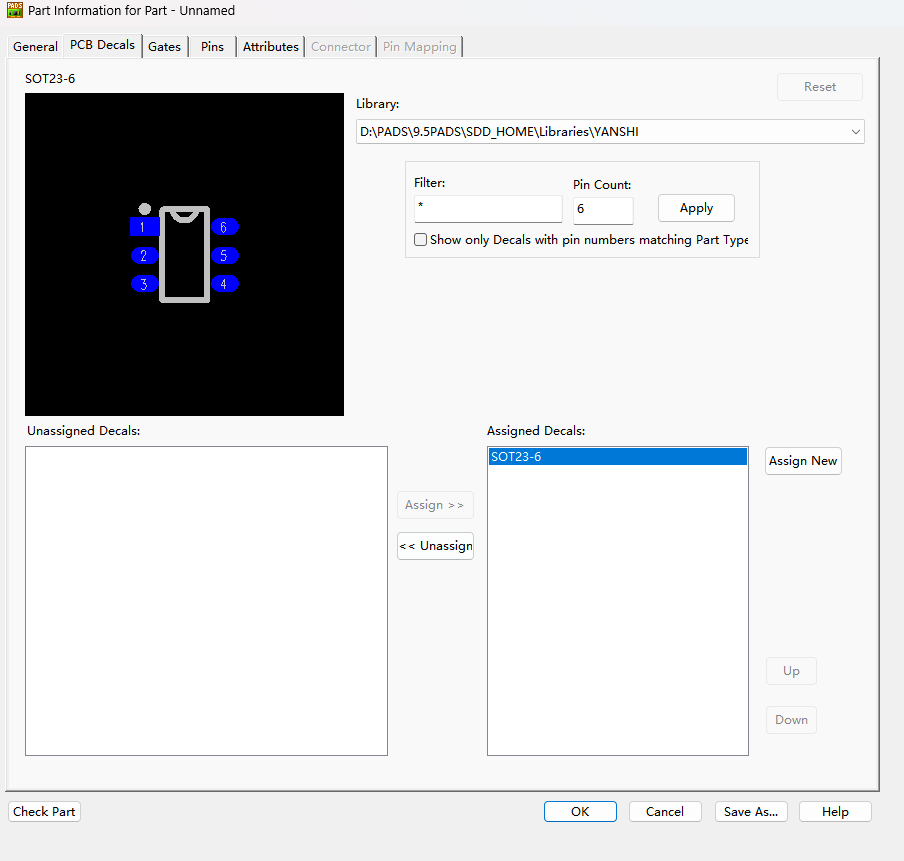

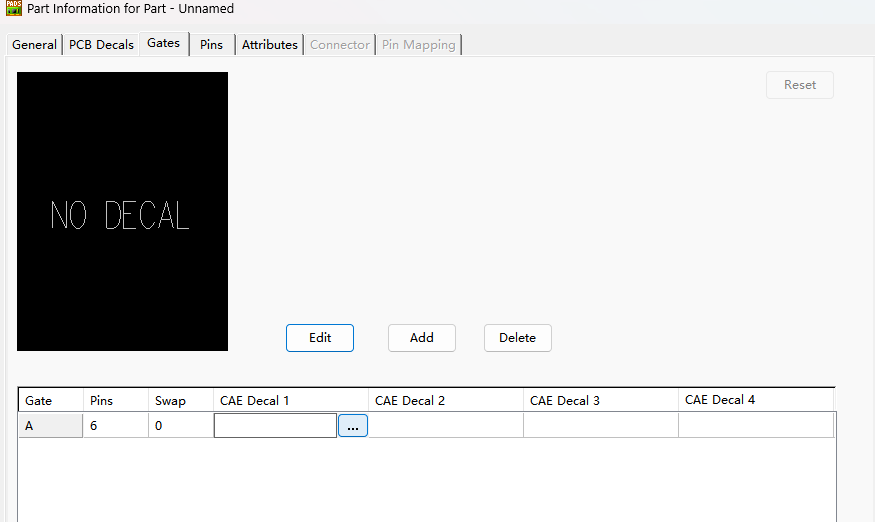

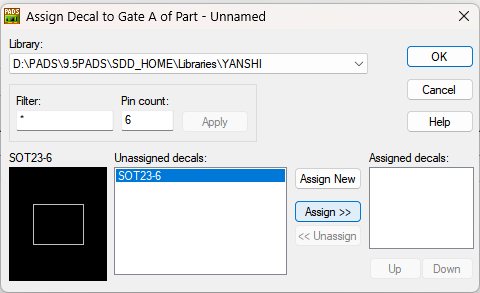

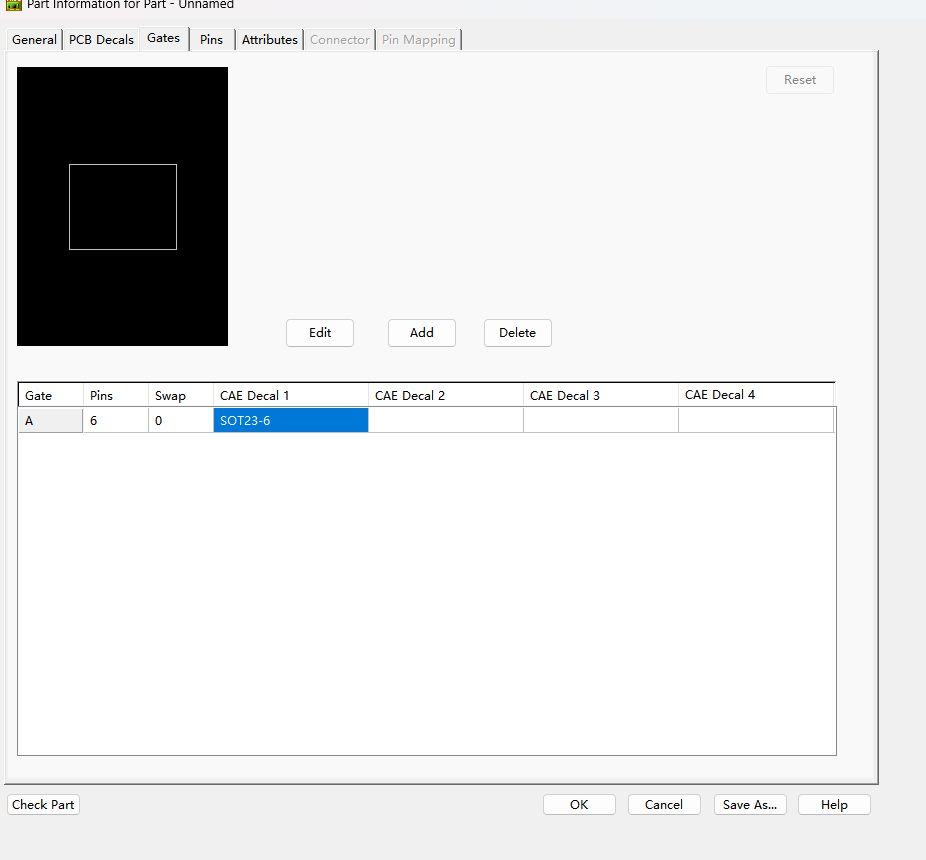

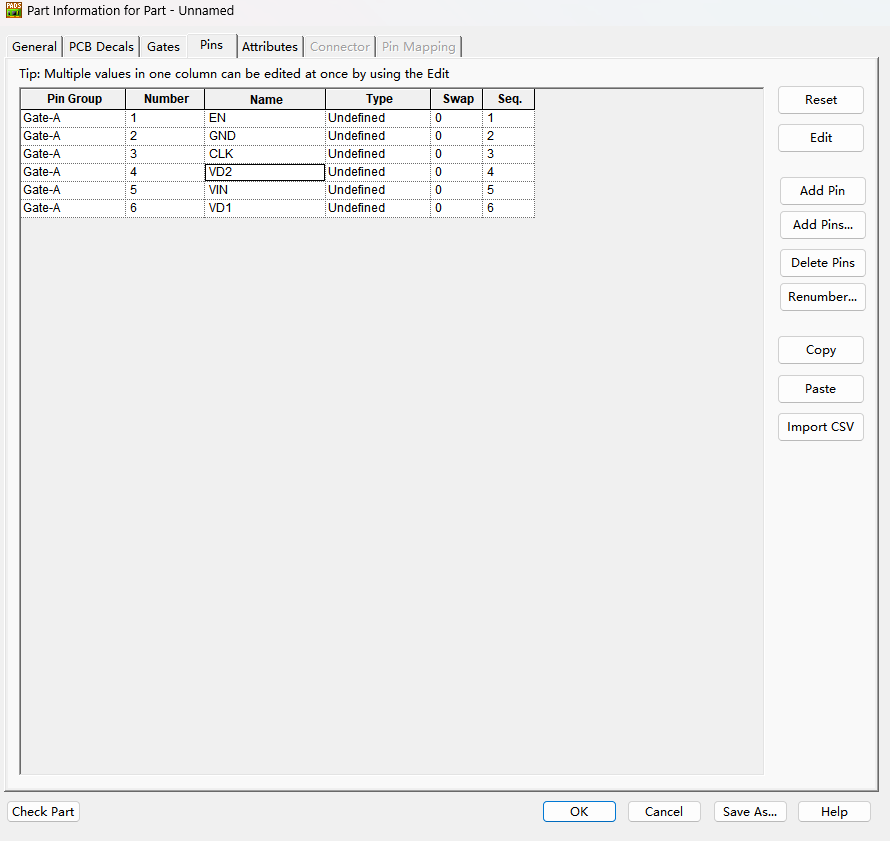

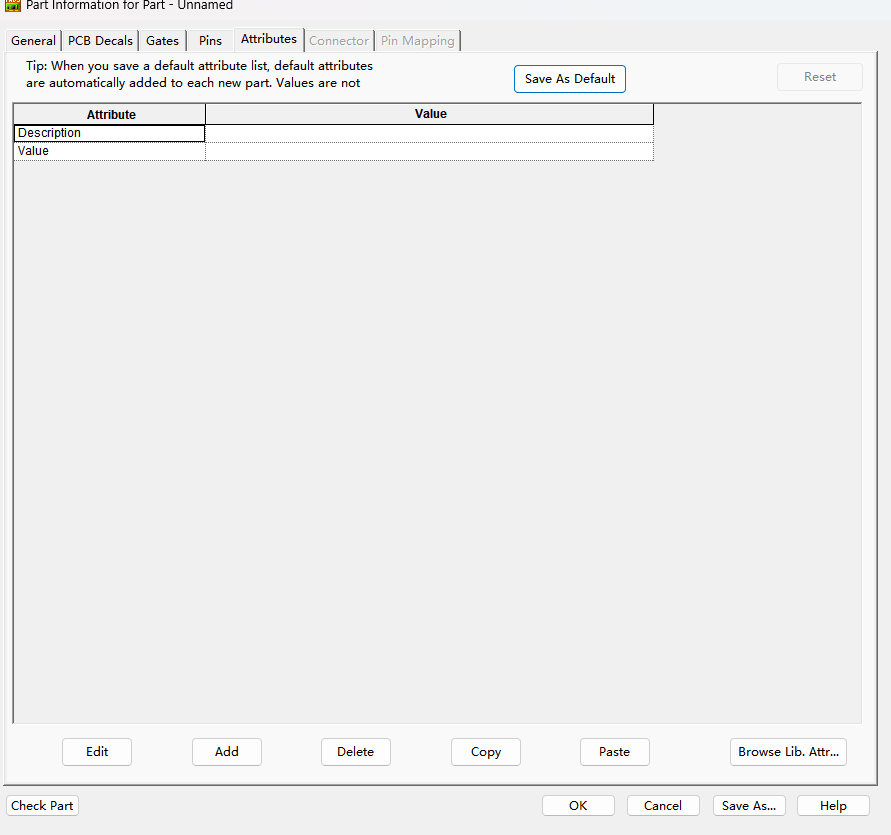

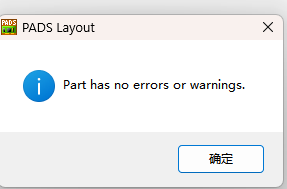

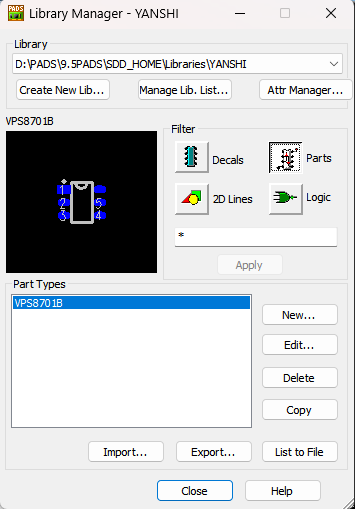

完成一个新的PCB Decal保存之后系统会提示是否创建Part Type,我们选择是。会弹出Part Information for Part-Unnamed会话框。在General中选择Logic Family,这里选择UND(根据器件类型选择对应的符号),Prefix List这里和Logic Family选择统一的符号标识,写U*;PCB Decals中选择SOT23-6封装,点击Assign选中后器件会从左边的Unassigned Decals中移到Assigned Decals;Gates中点击CAE Decal1下方的格,双击后显示...![]() ,点击...选择对应的Logic Decal,点击Assign后再点击OK关闭会话框;Pins中修改PinGroup,这里可以选择为Gate A,Number按顺序填写,Name参照器件手册中的Pin Name填写,Type可以选择默认的Undefined也可根据引脚属性分别设置;Attributes中根据实际添加描述和值(也可以不写),这里描述写为“微功率隔离电源专用芯片 6-30VIN/30V/0.3A 功率管”,Value写为“VPS8701B”;完成以上设置后点击Check Part,提示无错误和警告,点击确定。最后点击OK弹出Save Part Type to Library,我们将器件的名称与厂家的名称填成一致,这里写作VPS8701B,点击OK。这样就完成一个器件封装的制作了。最后在Library中点击Parts可以看到新建的器件。

,点击...选择对应的Logic Decal,点击Assign后再点击OK关闭会话框;Pins中修改PinGroup,这里可以选择为Gate A,Number按顺序填写,Name参照器件手册中的Pin Name填写,Type可以选择默认的Undefined也可根据引脚属性分别设置;Attributes中根据实际添加描述和值(也可以不写),这里描述写为“微功率隔离电源专用芯片 6-30VIN/30V/0.3A 功率管”,Value写为“VPS8701B”;完成以上设置后点击Check Part,提示无错误和警告,点击确定。最后点击OK弹出Save Part Type to Library,我们将器件的名称与厂家的名称填成一致,这里写作VPS8701B,点击OK。这样就完成一个器件封装的制作了。最后在Library中点击Parts可以看到新建的器件。

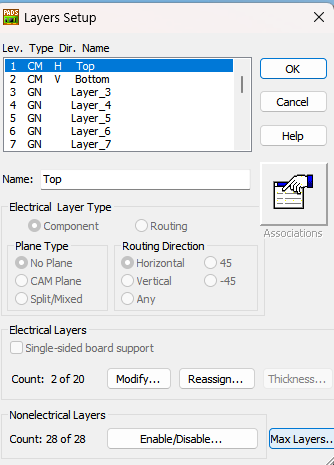

三:总结

这篇主要是PADS 9.5安装和器件封装创建的方法,封装也可以从立创上下载,但是有的器件会没有绘制,而且从立创上下载的封装会有各种类型的,绘制的时候层数可能会到最大层,在PCB绘制的时候需要注意打开层设置,将层调到最大层才能导入。

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?