磁控溅射技术属于PVD(物理气相沉积)技术的一种,是制备薄膜材料的重要方法之一。它是利用带电荷的粒子在电场中加速后具有一定动能的特点,将离子引向被溅射的物质制成的靶电极(阴极),并将靶材原子溅射出来使其沿着一定的方向运动到衬底并在衬底上沉积成膜的方法。磁控溅射设备使得镀膜厚度及均匀性可控,且制备的薄膜致密性好、粘结力强及纯净度高。该技术已经成为制备各种功能薄膜的重要手段。北方华创微电子突破了溅射源设计技术、等离子产生与控制技术、颗粒控制技术、腔室设计与仿真模拟技术、软件控制技术等多项关键技术,建立了具有自主知识产权的核心技术优势,形成了国产集成电路领域高端薄膜制备设备零的突破,设备应用跨越多个技术代,代表着国产集成电路薄膜制备工艺设备的较高水平,并成功进入国际供应链体系。北方华创微电子先后在集成电路、先进封装、LED等领域研制了具有自主知识产权的多款PVD产品并成功产业化。

Al Pad PVD作为集成电路中的一道工序,对后续的封装工艺起到了承上启下的作用。在集成电路制造过程中,几乎所有的半导体器件在其制造过程都要使用Al Pad PVD用于其后道金属互联,为芯片中各器件提供电子信号、微连线等作用。Al Pad物理气相沉积系统作为集成电路工艺中的一道重要工序,主要应用于Bond pad和Al interconnect工艺。目前典型的Al pad工艺Al厚度为1um,随着集成电路工艺的发展,Al Pad的厚度越来越厚,特别是28nm以下技术节点,3um厚铝应用逐渐成为主流,这一变化对设备的高产能、高效率、低成本、低缺陷提出了更高的要求。为了更好的适应半导体市场的飞速发展,北方华创微电子公司于2015年初适时推出eVictor A830 Al Pad物理气相沉积系统,产品具备诸多特性。

1 评估板简介

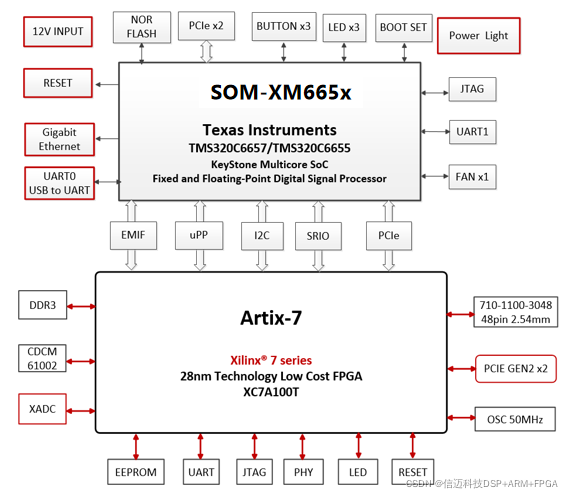

基于 TI KeyStone C66x 多核定点/浮点 DSP TMS320C665x + Xilinx Artix-7 FPGA 处理器;

TMS320C665x 主频为 1.0G/1.25GHz,单核运算能力高达 40G MACS 和 20G FLOPS,FPGA XC7A100T 逻辑单元 101K 个,DSP Slice 240 个; Ø

TMS320C665x 与 FPGA 通过 uPP、EMIF、I2C、PCIe、SRIO 等通讯接口连接,其中 PCIe、 SRIO 每路传输速度最高可达到 5 GBaud; Ø

FPGA 采集卡支持双通道 250MSPS*12Bit 高速高精度 ADC,一路 175MSPS*12Bit 高速高精度 DAC,满足多种数据采集需求;

支持千兆网口,可接工业网络摄像机,同时支持 I2C、SPI、UART、McBSP 等常见接口; Ø

支持 CameraLink 输入输出、VGA 输出等拓展模块;

支持裸机和 SYS/BIOS 操作系统。

图1 开发板实物

深圳信迈基于 TI 设计的XM-C665xF-EVM 是一款 DSP+FPGA 高速大数据采集处理架构,适用于高端图像处理、高速大数据传输和音视频等大数据采集处理领域。此设计通过 TMS320C665x 的 uPP、EMIF、I2C、PCIe、SRIO 等通信接口将板卡结合在一起,组成 DSP+FPGA 架构,实现了需求独特、灵活、功能强大的 DSP+FPGA 高速数据采集处理系统。

SOM-XM665xF 引出 CPU 全部资源信号引脚,二次开发极其容易,客户只需要专注上层运用,降低了开发难度和时间成本,让产品快速上市,及时抢占市场先机。不仅提供丰

富的 Demo 程序,还提供 DSP 核间通信开发教程,全面的技术支持,协助客户进行底板

设计和调试以及多核软件开发。

2 典型应用领域

数据采集处理显示系统 Telecom Tower:远端射频单元(RRU)高速数据采集和生成

高速数据采集处理系统

高端图像处理设备

高端音视频数据处理

通信系统

3 软硬件参数

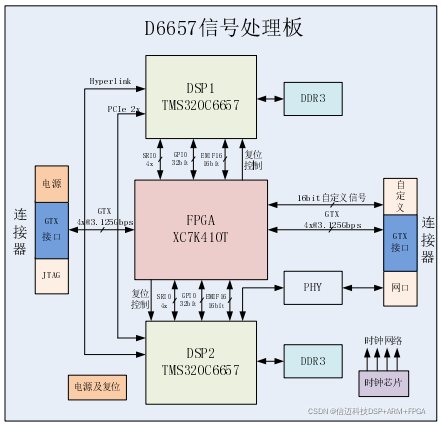

前端由 FPGA 采集两路 AD 数据,AD 数据通过 uPP、EMIF 总线或者 PCIe、SRIO 接口等通信接口传输到 DSP。 Ø

AD 数据被 DSP 处理之后,可用于数据对比和分析、网络转发、SATA 硬盘存储等应用。

DSP 根据处理结果,将得到的逻辑控制命令送 FPGA,由 FPGA 控制板载 DA 实现逻辑输出,更新速率 175MSPS。

图 2 大数据采集原理框图

高速数据采集前端部分由 FPGA 同步采集两路 AD 模拟输入信号,可实现对 AD 数据进行预滤波处理,AD 采样率最高可达 250MSPS。另外一路 DAC 可输出任意幅值和任意波形的并行 DA 数据,更新速率 175MSPS。

高速数据传输部分由 EMIF、I2C、PCIe、SRIO 等通信接口构成。大规模吞吐量的 AD和 DA 数据,可通过 SRIO 和 PCIe 接口在 DSP 和 FPGA 之间进行高速稳定传输;DSP 可通过 EMIF 总线对 FPGA 进行逻辑控制和进行中等规模吞吐量的数据交换,同时可通过 I2C对 FPGA 端进行初始化设置和参数配置。

(3)高速数据处理部分由 DSP 核和算法库构成。可实现对 AD 和 DA 数据进行时域、频

域、幅值等信号参数进行实时变换处理(如 FFT 变换、FIR 滤波等)。

(4)视频采集、输出拓展部分由 CameraLink 输入输出模块、VGA 输出模块、千兆网等

部分构成。接口资源丰富,方案选择灵活方便,是高端图像处理系统的理想选择。

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?