思路和数据仅供参考,不一定对,如有不足,还望指出!

*更新2024年12月31日22:59:33新增了指令提取导数的方法,新增了旧版本绘制导数曲线的方法 偷偷修改了一个错误的公式 并听了一会b站跨年晚会

*更新2025年1月1日00:53:30

修正了本征增益应该在饱和区求gms的问题,并祝大家元旦快乐!

*更新2025年1月1日11:06:46

添加了缩减器件尺寸的思路图;修了一些小bug,并等待午饭送达。

*更新2025年1月1日13:41:07

加入了Maximilian von München提供的旧版本绘制导数曲线的方法

*更新2025年1月1日22:15:30

修正了一个笔误,600um时器件tox的厚度应为0.015um

前言

Silvaco TCAD是一种集成电路设计和分析软件,用于半导体器件模拟和工艺过程模拟,提供了一系列工具和模型,用于模拟和分析各种半导体器件的性能和特性。它可以模拟晶体管、二极管、MOS器件、功率器件等等。通过使用Silvaco TCAD,用户可以进行设备特性仿真、器件优化和工艺过程优化等。MOSFET是最常见的电子器件单元,也是一个重点仿真对象。

本文分享自己仿真一个NMOS器件的过程,以及一些软件使用的心得。

一、仿真要求

设计一个理想的n沟道多晶硅栅MOSFET(VT=0.65v,tox=30nm,L=1.25µm,Qss=1.5x1011cm-2),使得在VGS=2.5V,VDS=0.1V时,漏电流ID=50µA。

(1) 计算并确定所需衬底掺杂浓度,沟道宽度和栅极类型;

(2) 利用Silvaco TCAD工具开展器件设计与仿真:(I)基于上述参数仿真对应nMOSFET的输出特性曲线;(II)根据恒定电场尺寸缩减原则,在上述器件的基础上,设计最小沟道长度为0.6µm,0.3µm的nMOSFET器件,仿真得到阈值电压、本征增益以及输出特性曲线;(III)对比沟道长度为0.3µm nMOSFET的理想输出特性曲线与仿真输出特性曲线,分析导致产生该差异的原因。

二、计算结构参数

1.确定衬底掺杂浓度

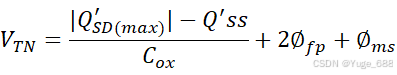

P型衬底阈值电压表达式:

其中:阈值反型点处空间电荷区电荷:

![]()

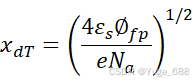

而最大空间电荷区宽度:

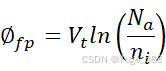

费米势:

金半功函数差近似(重掺杂):

单位面积氧化层电容:

代入以下已知数据:

VTN=0.65V,e=1.6×10-19 C,Cox=3.9×8.854×10-14÷(30×10-7)=0.115uF/cm2 , εs=11.7×8.85×10-14 F/cm, Vt=0.0259V,ni=1.5×1010 cm-3,Qss=1.5×1011 cm-2 ,Eg=1.12eV。

假设n+多晶硅的Ef能级和Ec能级重合,p+多晶硅的Ef能级和Ev能级重合。

我编写了一个简单的阈值电压计算程序,需要的同学可以拿来在MATLAB上跑一下。

% @Copyright 688

% Vth计算器

% 常数和公式已经设定好,只需要改Na和phi_ms即可;phi_ms可以去课本上找图,也可以用我下面注释掉的公式算;

clc

clear

Es = 11.7*(8.85e-14);

Eox = 3.9*(8.85e-14);

Eg = 1.12;

e = 1.6e-19;

Qss = 1.5e11;

Na = 1e10; %<-改这儿

%phi_ms = ;%<-读图出的数值写这儿

tox = 30; %单位:nm 转换为cm要*1e-7

phi_fp = 0.0259*(log(Na)-log(1.5e10));

phi_ms = -(Eg/2 + phi_fp);%用公式算n+(注意前提条件!)

% phi_ms = Eg/2 - phi_fp;%用公式算的 p+

xdT = sqrt(4*Es*phi_fp/e/Na);

Qsdmax = e*Na*xdT;

Vth = (Qsdmax - Qss*e)*tox*10*(1e-8)/Eox + phi_ms + 2*phi_fp;

fprintf('Vth: %.3f\n', Vth);可以得到:在使用n+多晶硅栅时,要使Vt=0.65V,应取Na=5.4×1016cm-3 ;在使用p+多晶硅栅时,要使得Vt=0.65V,应取Nd=2.1×1014cm-3。

2.计算沟道宽度

根据已知条件:VGS=2.5V,VDS=0.1V时,漏电流ID=50µA

选用n+ 多晶硅栅时,衬底掺杂浓度Na为5.4×1016cm-3 ,属于低掺杂。已知在 300K时硅电子迁移率为μ=800cm2 /V·s。

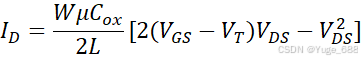

非饱和区理想电流电压关系为:

计算可得理想W = 3.78µm

三、器件仿真

这部分我将逐段解释我使用的代码,方便大家理解。我使用的是atlas直接形成器件,会比用Athena方便很多。

1、开始部分及定义网格

go atlas simflags="-P 2"

mesh space.mult=1 width=3.78

x.m l=0.0 spac=0.05

x.m l=2.25 spac=0.05

y.mesh loc=-0.30 spac=0.05

y.mesh loc=-0.20 spac=0.05

y.mesh loc=-0.03 spac=0.03

y.mesh loc=0 spac=0.05

y.mesh loc=1.5 spac=0.5第一句 simflags="-P 2" 使用两个核心进行运算,我这种渣机可以跑得快一点。

这部分非常重要。建议先在纸上画出目标器件的尺寸,再输入到代码中。

mesh space.mult=1 width=3.78 请注意这里引入了刚刚计算得到的W。必须在atlas的mesh步骤声明width大小,在别的地方引入无效(且不会报错)。声明width大小后,软件计算得到的电流会自动乘以这个W。

mesh部分容易出现的问题:

- (1)网格定义得太细。这容易跑很久甚至跑飞,应该是计算超过最大次数或不收敛。

- (2)定义网格要配合后面的定义区域来,如果区域边界和不在网格线上,例如设置区域边界为1.375而网格间隔0.03,不能整除,画出来的图就会出现锯齿和神秘彩虹色。像这样↓

此时需要修改网格位置,一般把间隔改小一些就行。

在处理一些及薄的区域时,可以在mesh的部分新加一条,如我代码里的:

y.mesh loc=-0.03 spac=0.03这一步就是为了保证30nm厚的氧化层完整。如果这个地方没有这一句,氧化层区域边界很有可能会吸附到别的网格线上,导致出现锯齿或者代码跑飞。

2、定义区域和电极

region number=1 x.min=0 x.max=2.25 y.min=0 y.max=1.5 material=silicon

#衬底

region number=2 x.min=0 x.max=2.25 y.min=-0.3 y.max=0.0 material=oxide

#氧化层0.03um

region number=3 x.min=0.5 x.max=1.75 y.min=-0.20 y.max=-0.03 material=poly

#poly栅

region number=4 x.min=0.1 x.max=0.4 y.min=-0.3 y.max=0.0 material=aluminum

#S

region number=5 x.min=1.85 x.max=2.15 y.min=-0.3 y.max=0.0 material=aluminum

#D

region number=6 x.min=0.5 x.max=1.75 y.min=-0.3 y.max=-0.2 material=aluminum

#gate

electrode reg=4 name=source

electrode reg=5 name=drain

electrode reg=6 name=gate

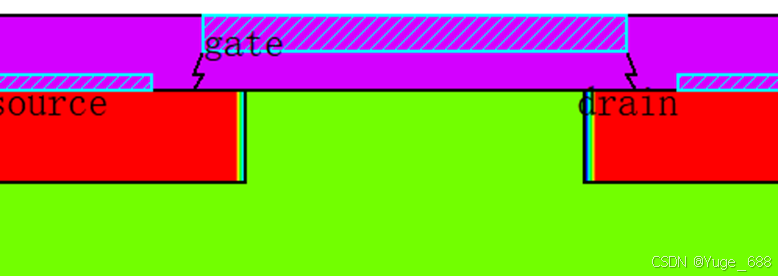

electrode bottom name=bulk使用Atlas定义区域(region)需要像你冬天盖被子一样一层层往上盖,后面定义的区域会覆盖前面的区域。正如我定义氧化层厚度为0.3um,即从硅的上界面开始,往y负方向充满整个上方空间。随后在氧化层的(图层)上方覆盖一块多晶硅区,多晶硅和硅中间留有0.03um的二氧化硅,这正是我们所需要的氧化层厚度。

定义电极时,可以直接指定reg(region)整个为电极。

常见问题:网格范围内所有的区域都需要有定义。如果漏了哪里没有定义上,软件就会报错。

如果出现了此类报错,可以在所有区域定义前面加这么一句话:

region number=1 x.min= xxx y.min=xxx material=air其中,“xxx”的位置替换为你网格的边界。注意atlas的坐标轴,y向下为正,x向右为正。

3、定义掺杂和保存结构文件

doping uniform region=1 x.min=0 x.max=2.25 y.min=0 y.max=1.5 p.type concentration=5.4e16

doping uniform region=3 x.min=0.5 x.max=1.75 y.min=-0.20 n.type concentration=2e19

doping gauss region=1 x.min=0 x.max=0.5 junc=1.0 rat=0.0001 n.type concentration=1.1e20

doping gauss region=1 x.min=1.75 x.max=2.25 junc=1.0 rat=0.0001 n.type concentration=1.1e20

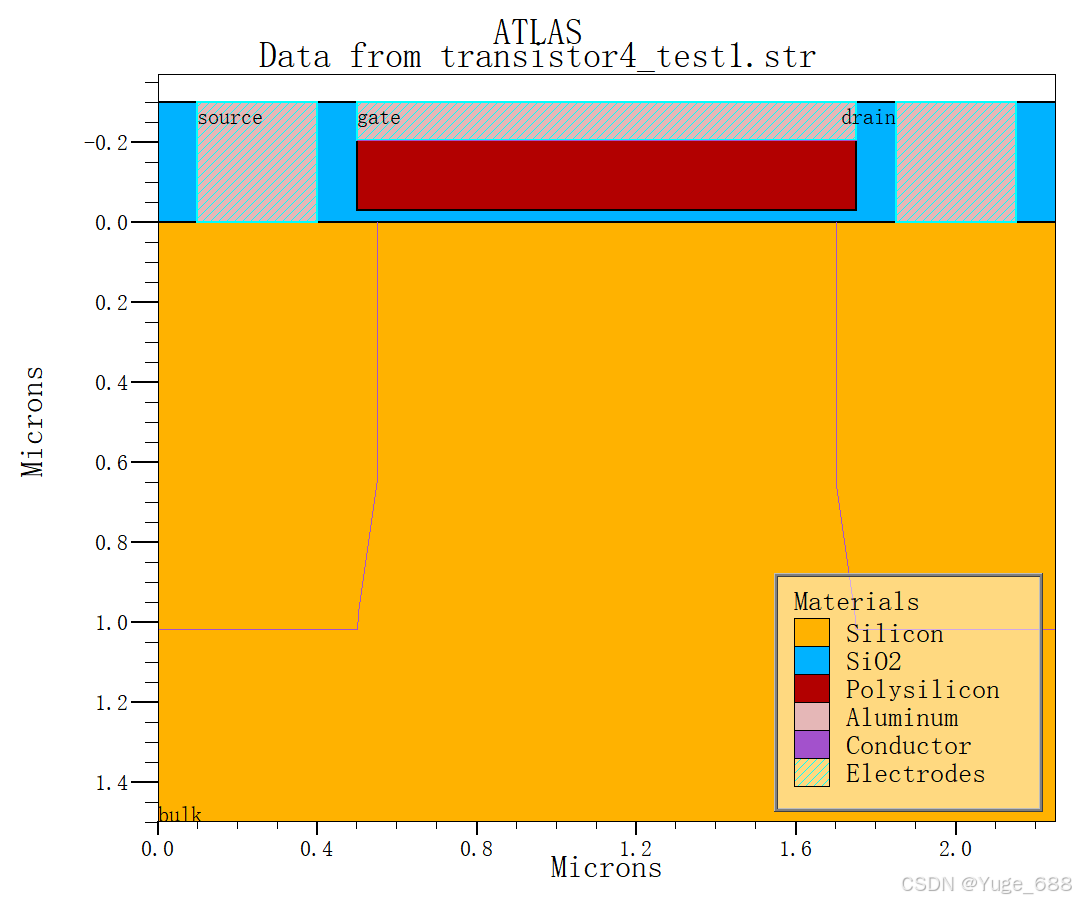

structure outf=NMOS.str

tonyplot NMOS.str这部分需要对衬底、多晶硅、源漏进行掺杂。其中源漏使用高斯分布(这几个参数我也没搞懂,复制粘贴来的),其他都是用均匀分布。

使用doping指令时,先指定区域,再指定xy范围,最后掺杂位置会是两个的交集。

衬底掺杂选择我们之前算出的Na,多晶硅掺杂需要根据后续阈值电压进行微调,源漏掺杂应该随便选个大点的数就行(

最后两句应该用过silvaco的都知道,保存为.str文件,并用tonyplot画出来,如图。

(这里我用错图了,标题应该是NMOS.str)

如何实现我图上这样的效果呢?右键,点击【Display】选项,在一排小方框里勾选【electrodes】(电极)【junctions】(结),点击OK,就有这个效果了。

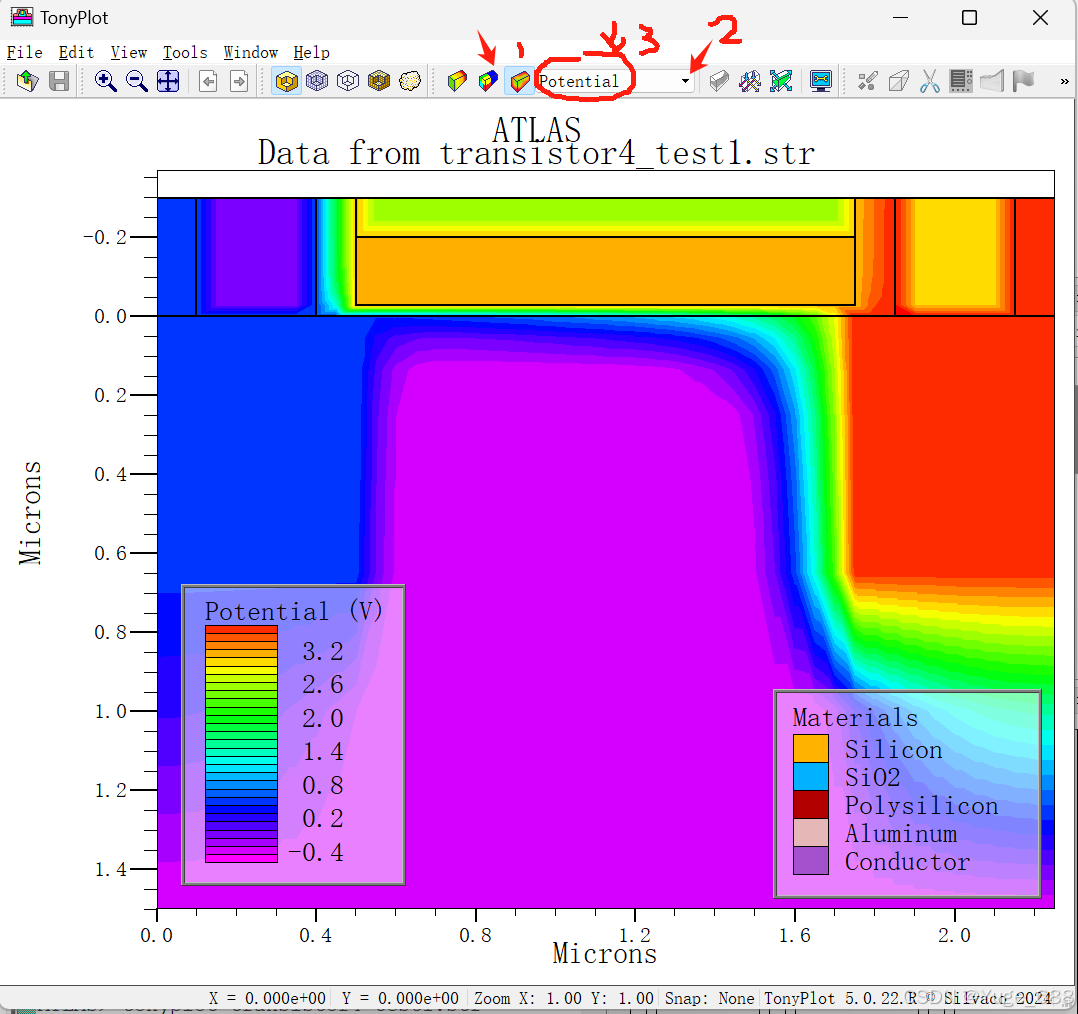

tonyplot还有很多很强力的功能,这里附加一个查看电场分布的方法:

在后期启动电学仿真后,使用log outf=xxx.log master语句保存日志文件,然后用tonyplot画出来。按照图中顺序,选择等高线图(第三个),点击右侧复选框,在复选框中找到【potential】选项,打开就能看到电场的分布图。

非常amazing呀!想必小同学你也是第一次看到夹断的沟道吧?

4、通过转移特性曲线提取阈值电压

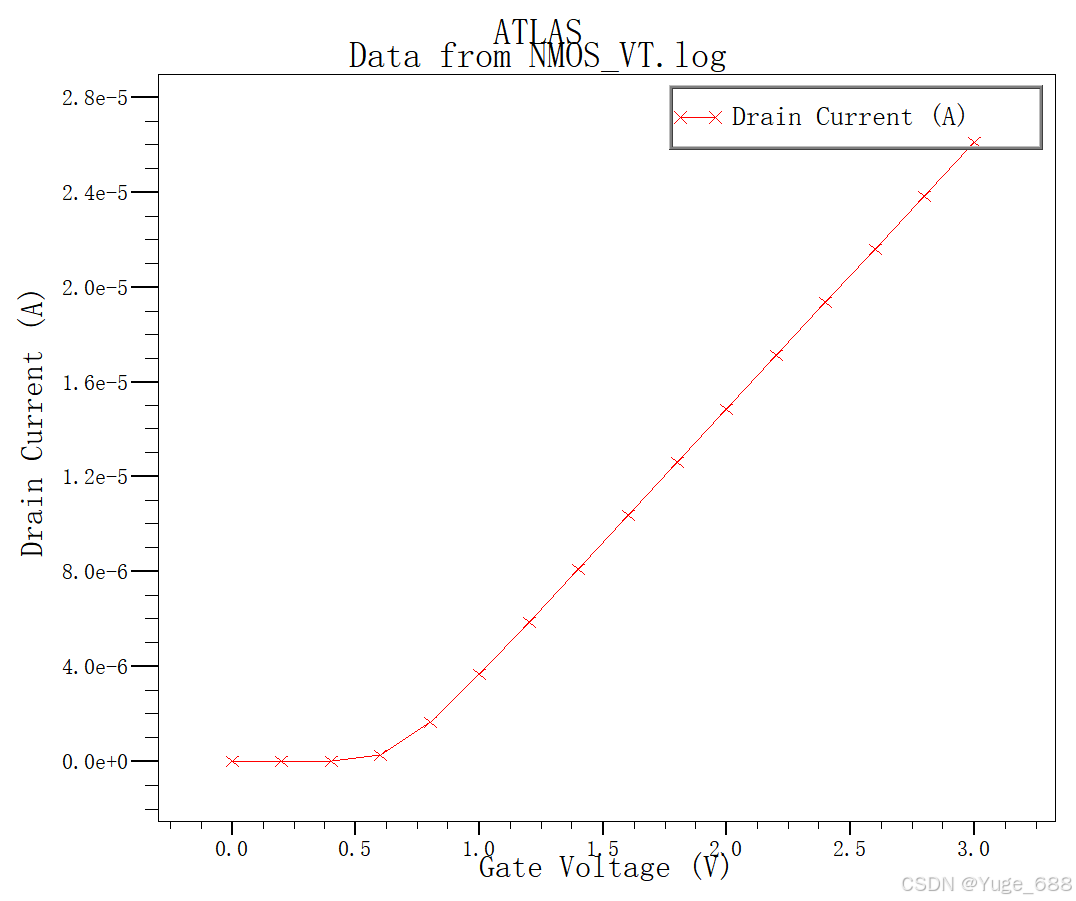

我们搭建器件模型的部分就到此结束,下面进行器件的电学仿真。按照题干要求,我们需要提取器件的转移特性曲线和输出特性曲线。以下部分为提取转移特性曲线的代码。

model cvt srh PRINT

impact selb

#contact name=gate n.poly

method newton trap

interface qf=1.5e11

solve init

solve vdrain=0.1

log outf=NMOS_VT.log master

solve vgate=0 vstep=0.2 vfinal=3 name=gate

log off

extract name="vt" (xintercept(maxslope(curve(abs(v."gate"),abs(i."drain")))) - abs(ave(v."drain"))/2.0)

extract name="gm" max(deriv(v."gate",i."drain"))

tonyplot NMOS_VT.log同学们可能看到提取就头晕哈,没事我一条条解释。

model cvt srh PRINT

这一条选择模型,可以无脑选,仿真一个NMOS完全足够。每个模型对应的含义和作用在此省略。

impact selb

如果要仿真击穿,加上这一句。

#contact name=gate n.poly

指定接触类型,根据唐龙谷《半导体工艺和器件仿真软件Silvaco TCAD实用教程》P120,铝和重掺杂硅的接触通常是欧姆接触,不要指定功函数,所以我注释掉了。

method newton trap

选择计算方式。

interface qf=1.5e11

定义界面电阻。我们题干中指定了界面电阻是1.5e11,故这么写。

solve init……等

这部分的大致含义为:开始求解,在漏极电压=0.1V的条件下,对栅极电压进行从0到3步长0.2的扫描,并把结果存到NMOS_VT.log日志文件中。之后提取日志文件,求解vt和gm。

如果没出问题的话,这段跑完就会在右边显示出提取到的vt和gm的值了,同时弹出tonyplot中IDS-VGS的转移特性曲线。此处的gm为线性区跨导,要和后面的饱和区跨导gms区分开。

几个细节:

- log outf=NMOS_VT.log master的master是什么作用?答:保存电学特性,加上master后你可以用tonyplot画出更多的神奇的图(后面说)

- log off要不要写?答:最好写。如果不写的话,有概率在tonyplot日志文件时发现乱七八糟的一堆线。

- vt提取为什么要在vdrain=0.1的条件下提?答:我也不知道。可以把这部分代码视为一个封装好的函数,既然它能跑就不要去动了。但是此时器件处于线性区,提取的gm也是线性区跨导。

- 能绘制导数曲线吗?答:下面马上介绍。

结果大概是这样的:

这里教大家怎么提取曲线的导数。 在Ids-Vgs曲线图中提取,就是跨导gm。

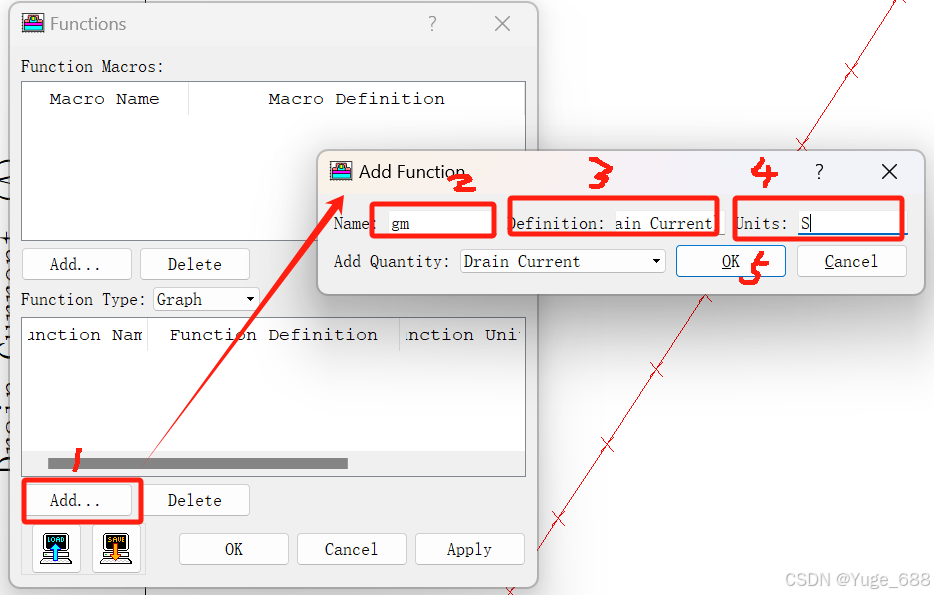

在tonyplot界面左上角【Edit】选项卡中,选择【Functions】,出现【Functions】界面,按照图中顺序点击/填写内容。definition中写的是dydx(Drain Current,Gate Voltage),嫌麻烦可以用【add quantity】中点哪个自动给你填入Definition中。

*对于Functions界面不一样的情况,在graph function1中输入dydx(Drain Current,Gate Voltage),点击OK,然后下一步选择function1而不是gm

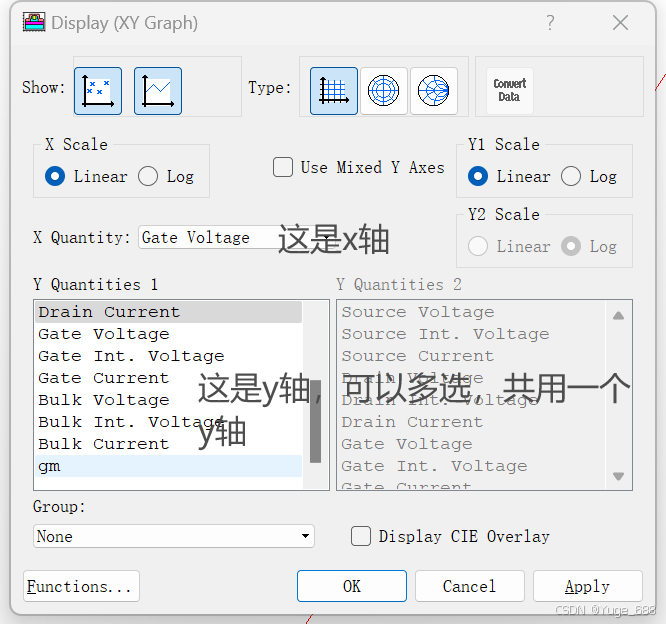

然后点击OK ,回到曲线界面,右键-【Display】,出现以下界面,在y轴中选中刚刚建立的gm(或function1),点击OK。

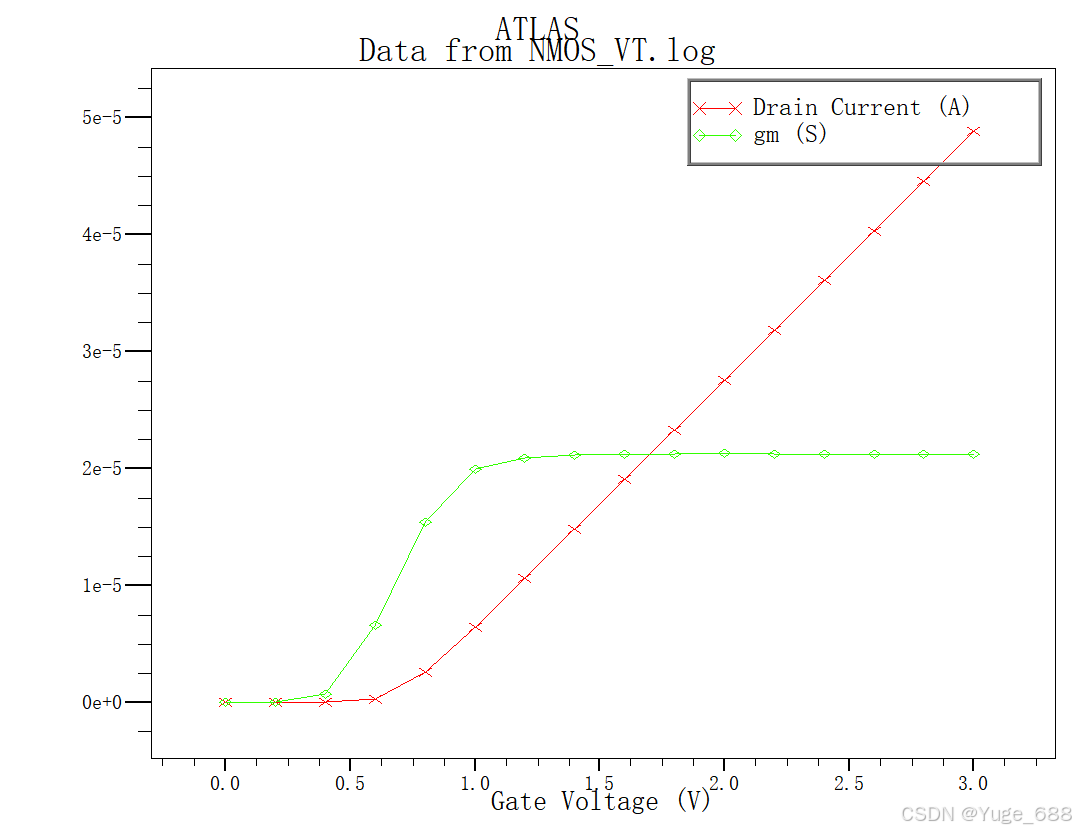

然后就可以得到以下曲线:

可以看到绿色的gm已经标注在图上了,用鼠标在曲线平稳的地方按住划一个小框可以放大图像,读出gm稳定值2.12e-5左右。

当MOS器件进入饱和区,gms与vgs呈线性关系,与vds无关。此时提取gms的方法为:配置vdrain=1.5V,确保进入饱和区,然后再对vgate进行扫描,提取vgate=2.5V时曲线的斜率。

为什么是2.5V呢?这是我自己设定的。不同的vgate下,gms不同,大家可以取不同的值试一试。

#计算饱和区跨导gms,此时跨导随Vgs线性变化,若要求Avs,需要固定Vgs的值,本代码中统一vgs=2.5

solve init

solve vdrain=1.5

#确保饱和

log outf=NMOS_gms.log

solve vgate=0 vstep=0.1 vfinal=3 name=gate

extract name="gms" grad from curve(v."gate",i."drain") where x.val=2.5

log off

#tonyplot NMOS_gms.log5、通过输出特性曲线提取输出电阻

接下来做输出特性曲线,这一段的大意为:建立4个不同栅压下的模型,分别对其进行源极电压扫描,并把结果统一输出。其中,在vgate=2.5时求解Ro和Avs。Ro为输出电阻,在这里利用饱和区切线斜率的倒数来表示。运行结束后应该就能提取出vgate=2.5V时的Ro和Avs了。

solve init

solve vgate=0.5 outf=tempVg1

solve vgate=1 outf=tempVg2

solve vgate=1.5 outf=tempVg3

solve vgate=2.5 outf=tempVg4

load inf=tempVg1

log outf=vg05.log

solve vdrain=0 vstep=0.3 vfinal=3 name=drain

log off

save outf=transistor1_test1.str

load inf=tempVg2

log outf=vg10.log

solve vdrain=0 vstep=0.3 vfinal=3 name=drain

log off

save outf=transistor2_test1.str

load inf=tempVg3

log outf=vg15.log

solve vdrain=0 vstep=0.3 vfinal=3 name=drain

log off

save outf=transistor3_test1.str

load inf=tempVg4

log outf=vg25.log

solve vdrain=0 vstep=0.3 vfinal=3 name=drain

extract name="Ro_25" 1.0/min(deriv(v."drain",i."drain"))

extract name="Avs_25" $gms*$Ro_25

log off

#save electronic feature into .str file

save outf=transistor4_test1.str master

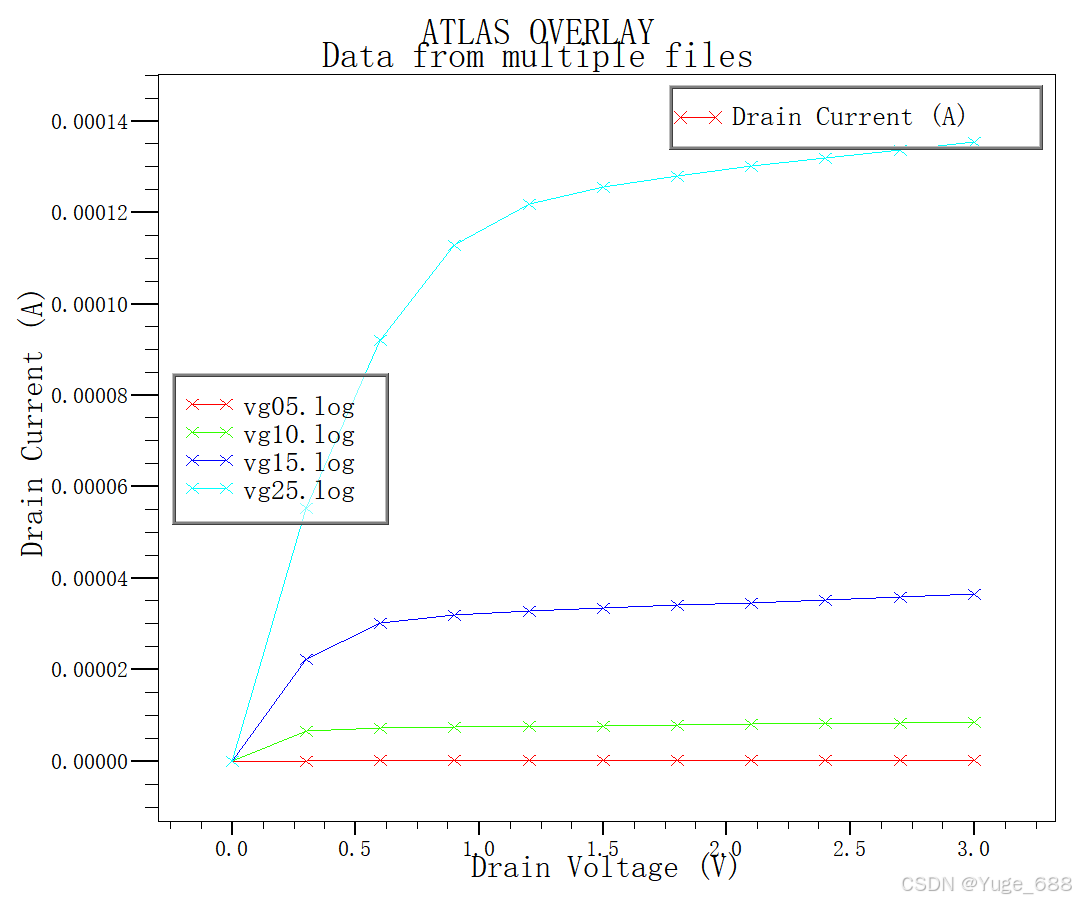

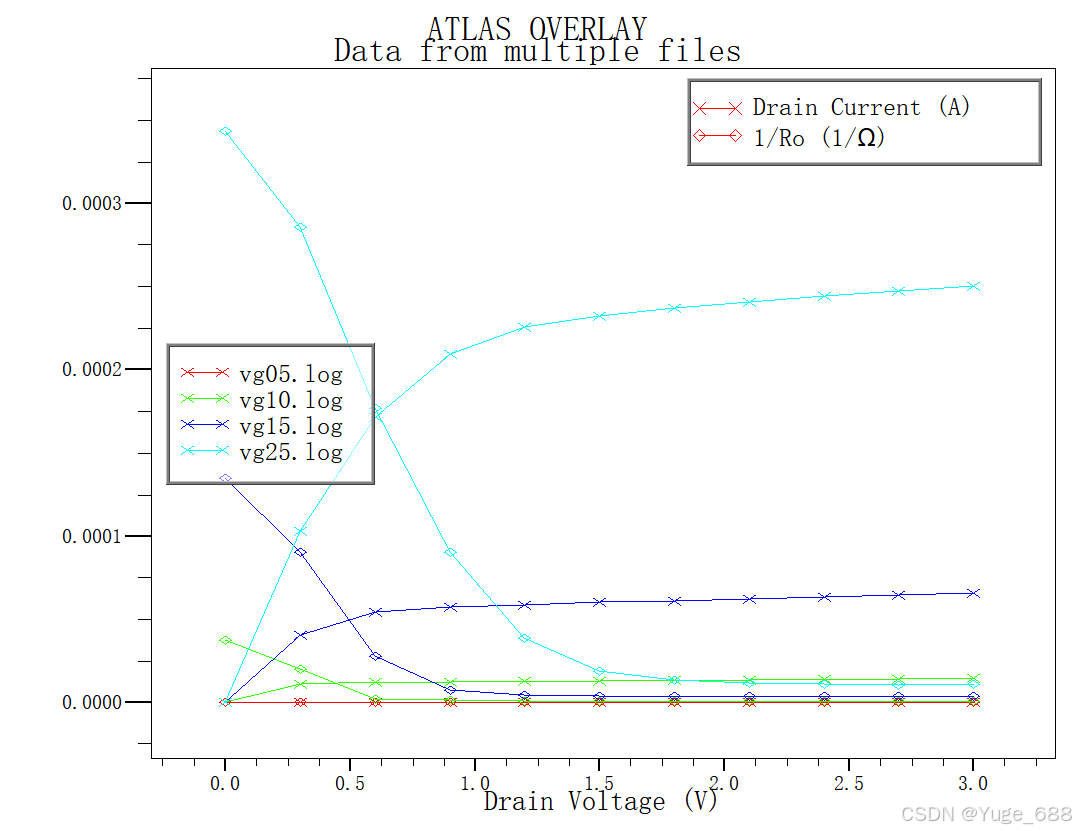

tonyplot -overlay -st vg05.log vg10.log vg15.log vg25.log

tonyplot transistor4_test1.str可能遇到的问题:

- 为什么又要solve init?答:solve init的作用是对所有电极电压为0的条件下求解。可以理解为把tonyplot上的点回归(0,0)处。不写的话,曲线里有可能又要出现一些乱七八糟的东西。

- tonyplot -overlay -st的意思是什么?答:-overlay是同时展示多条曲线,-st我忘了。

- 为什么画出来的图是几条竖着的线?答:右键【Display】,根据上面那张图修改x轴为vdrain即可。

生成的转移特性曲线图:

放大后我们可以发现,对于Vgs=2.5V,Vds=0.1V时,漏电流Id=35µA,比题目要求的50µA略小。这是怎么回事呢?我也不知道。欢迎在评论区告诉我。

同样,我们也可以画出它的导数曲线。在Ids-Vds曲线图中,切线斜率对应1/Ro,Ro为输出电阻。

同理可以读出,对于vgs=1.0V时,1/Ro约为4.0e-6,即Ro约为2.5e5Ω。

本征增益Av为负载开路时mos管的电压增益。通常与器件的频率响应有关,它描述了器件在高频工作时的增益能力。Av的计算公式为:

![]()

四、恒定电场按比例缩减

恒定电场缩小原则(Constant Electric Field Scaling Principle)是集成电路设计中用于指导器件尺寸缩小的一个基本原则。这个原则基于这样一个观察:在MOSFET中,如果所有尺寸按相同比例缩小,那么沟道中的电场分布将保持不变。

| 器件和电路参数 | 比例因子(k<1) | |

| 比例参数 | 器件尺寸(L,tox,W,xj) | k |

| 掺杂浓度 | 1/k | |

| 电压 | k | |

| 器件参数效应 | 电场 | 1 |

| *摘自《半导体物理与器件》P322 |

这里放出我缩减后的器件参数供大家参考。

器件参数修改值

| L(µm) | tox(µm) | W(µm) | Na(1016 cm-3) | |

| 原始器件 | 1.25 | 0.03 | 3.78 | 5.40 |

| 第一次缩小 | 0.61 | 0.015 | 1.85 | 11.02 |

| 第二次缩小 | 0.30 | 0.007 | 0.90 | 22.49 |

相信大家看完我上面对于代码的解析,缩小个器件简直易如反掌(doge),我就不提供缩减器件后的代码了,有需要可以找我要。

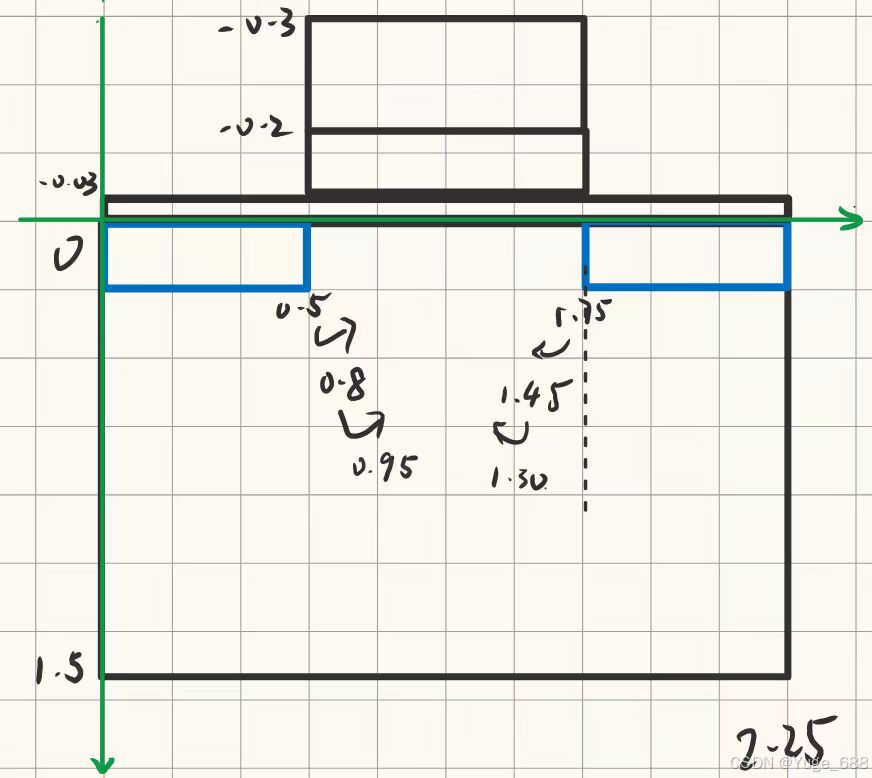

更新:这里提供一个缩减器件尺寸的思路,不一定对。

以下为我提取的器件性能参数,给大家一个数量级和变化趋势上的参考:

| 特征尺寸(µm) | Vt(V) | gms(S) | Ro(Ω) | Av |

| 1.25 | 0.654 | 0.00021 | 93898 | 19.70 |

| 0.612 | 0.497 | 0.00028 | 41288 | 11.70 |

| 0.30 | 0.304 | 0.00034 | 15549 | 5.28 |

那么我们的仿真就顺利结束了,希望对您有所帮助。

总结

本文提供了一种使用SilvacoTCAD仿真特定参数多晶硅NMOS器件的方法,以及一些计算参数的过程。其中重点解释了题干要求的器件参数是如何体现在仿真模型中的。

2025年快到了呀!希望同学们早点做大作业,不要拖到明年才完成!

记得降重,记得降重,记得降重!!

2万+

2万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?