基于FPGA的FIR数字滤波器设计(quartus和vivado程序都有)。

附:

1.配套quartus从MATLAB系数生成直到仿真成功说明文档。

2.配套仿真出波形的视频。

ID:8730676775115818

倪有孟迪吗

基于FPGA的FIR数字滤波器设计是一项重要而富有挑战性的任务。本文将从基本概念和理论背景出发,详细介绍了设计过程及其在实际应用中的意义。具体而言,我们将利用quartus和vivado两种常用的FPGA开发工具,实现一个高效、可靠的FIR数字滤波器。

首先,我们需要生成滤波器的系数。在这个过程中,我们可以利用MATLAB等工具来进行系数的计算和优化。通过选择合适的滤波器类型和参数,我们可以实现对不同信号的滤波需求,例如低通、高通、带通或带阻滤波器。在这一步骤中,我们还可以考虑一些特殊的设计要求,如滤波器的截止频率、滤波器阶数以及实时性能等。

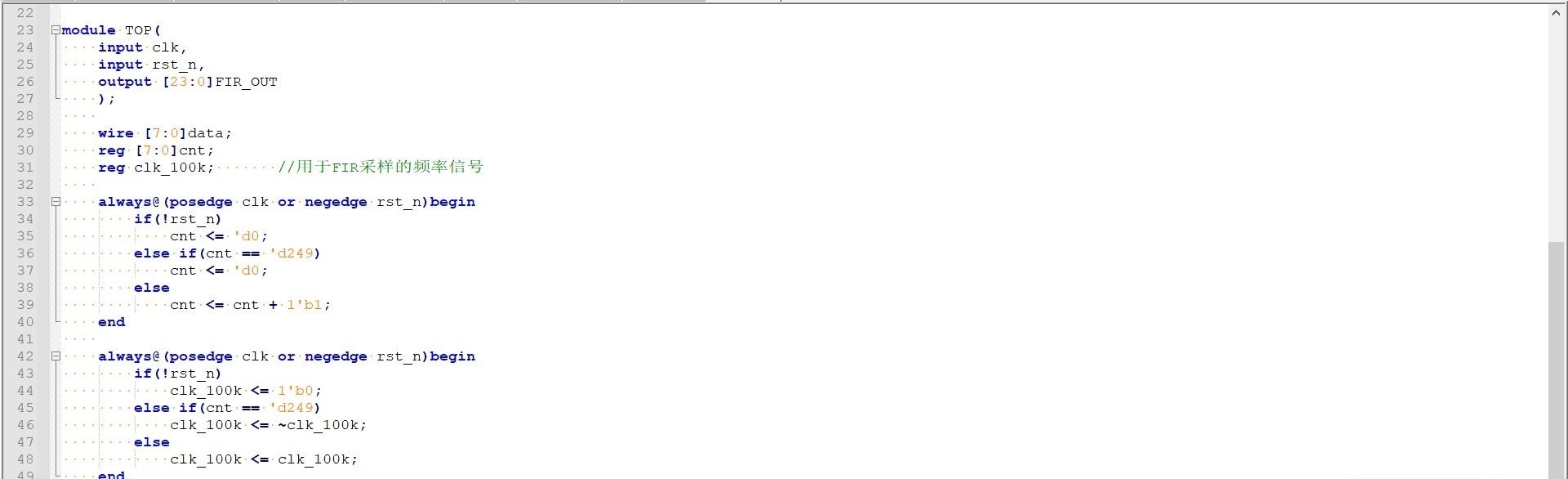

接下来,我们将使用quartus进行FPGA电路的设计。quartus提供了丰富的工具和资源,可以帮助我们实现数字滤波器的硬件描述语言(HDL)设计。我们可以使用Verilog或VHDL等语言,根据滤波器的功能和结构特点,编写相应的代码。在这一步骤中,我们需要注意的是优化电路的性能和资源利用,以确保实现的滤波器能够在FPGA上高效运行。

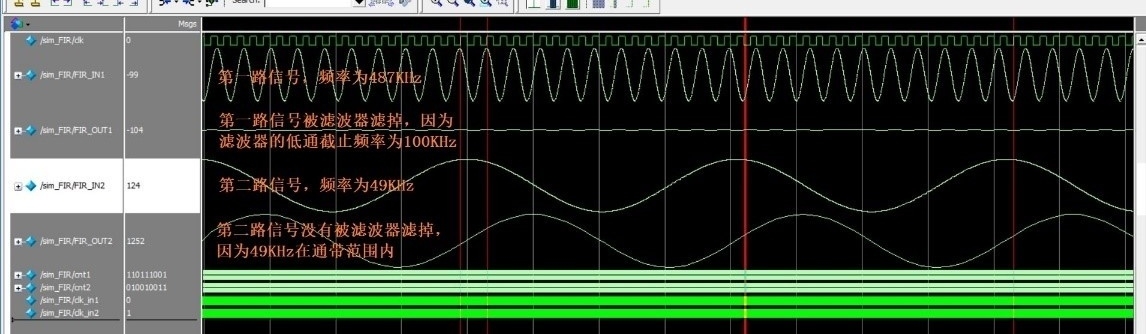

完成HDL设计后,我们需要进行仿真以验证滤波器的性能和正确性。通过配套的仿真工具,我们可以输入各种测试信号,并检查滤波器输出是否与预期一致。在这一过程中,我们可以对滤波器进行不同的测试,例如对各种频率和幅度的输入信号进行滤波,并观察输出的波形和频谱特征。仿真结果可以帮助我们发现潜在问题和改进的空间,从而提高滤波器的性能和质量。

最后,我们将利用FPGA开发板将设计好的滤波器加载到硬件上进行验证。这可以通过quartus和vivado提供的下载工具实现。在验证过程中,我们可以将真实的信号输入到滤波器中,并观察输出的波形和频谱特征。通过与仿真结果的对比,我们可以进一步验证滤波器的正确性和实时性能。

总结来说,基于FPGA的FIR数字滤波器设计是一个复杂而有意义的任务。通过quartus和vivado两种开发工具的配合,我们可以实现滤波器的系数生成、HDL设计、仿真测试和硬件验证等关键步骤。这些工具的使用和结合能够帮助我们设计出高效、可靠的FIR数字滤波器,满足不同应用领域对信号处理的需求。

(注:本文不涉及参考资料,仅为作者个人观点和经验总结。)

相关的代码,程序地址如下:http://matup.cn/676775115818.html

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?