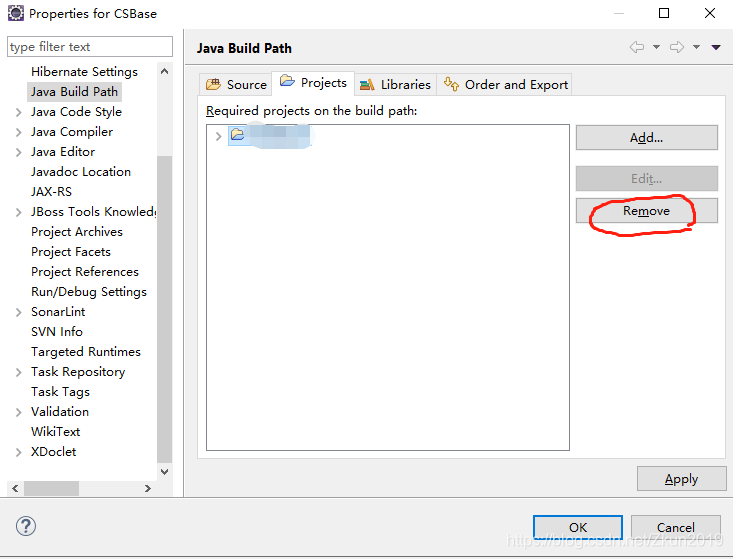

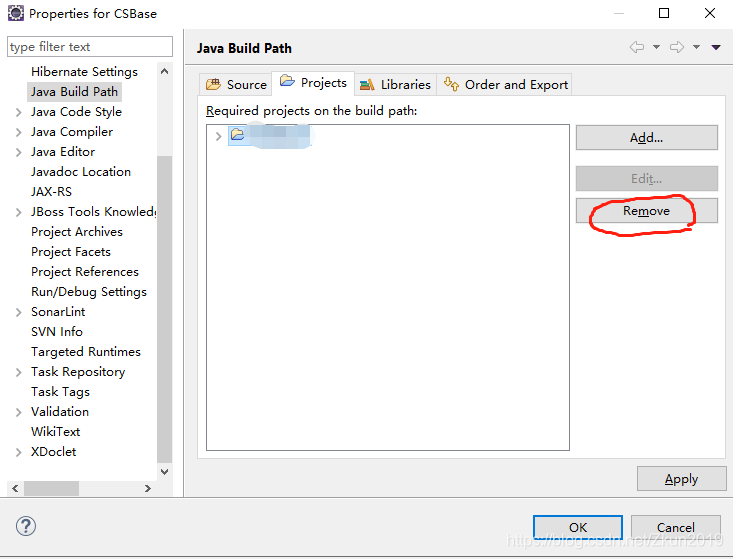

项目报这个问题的原因是A工程依赖B工程,B工程又依赖A工程,在编译的时候就会存在编译A时发现A依赖B,然后去编译B的时候又发现B依赖A,虽说并不一定会导致问题,不过存在死循环的可能,解决方法一,打开java Build Path 将互相依赖的项目remove掉

解决方法二

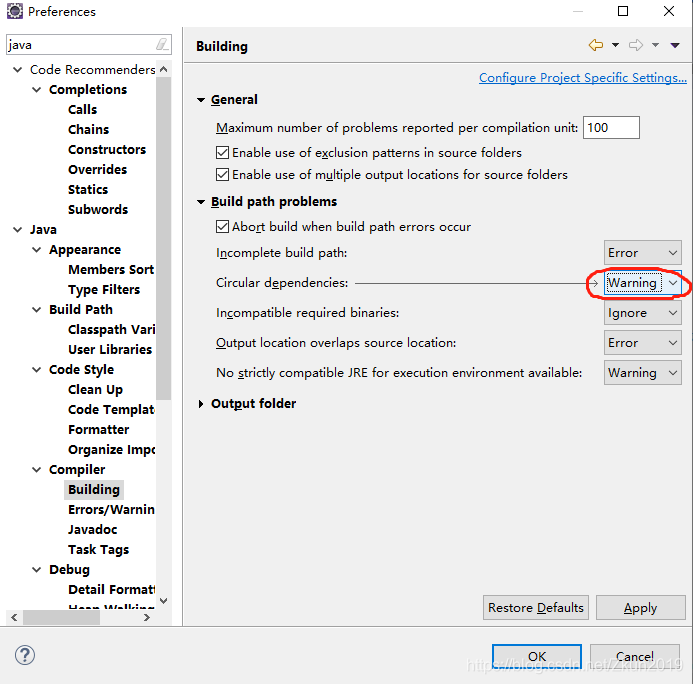

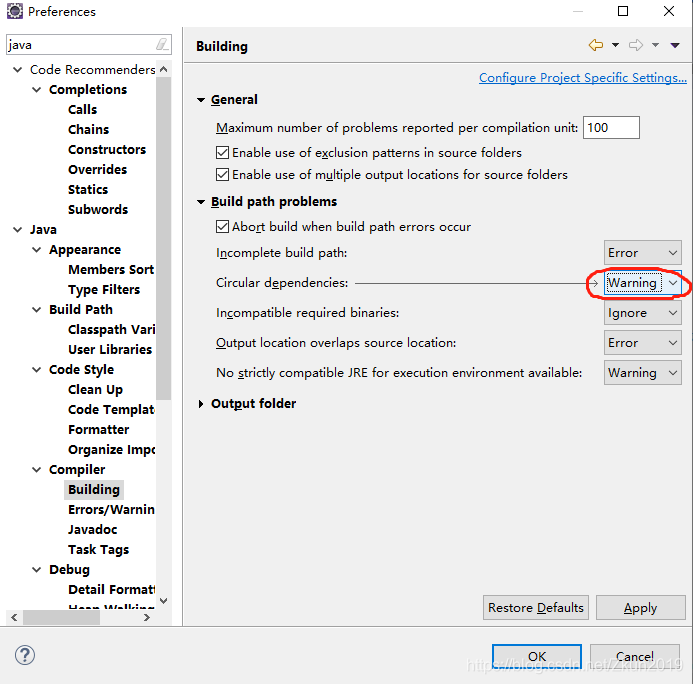

Preferences——>java——>Compiler——>Building——>将Circular dependencies改成Warning

项目报这个问题的原因是A工程依赖B工程,B工程又依赖A工程,在编译的时候就会存在编译A时发现A依赖B,然后去编译B的时候又发现B依赖A,虽说并不一定会导致问题,不过存在死循环的可能,解决方法一,打开java Build Path 将互相依赖的项目remove掉

解决方法二

Preferences——>java——>Compiler——>Building——>将Circular dependencies改成Warning

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?