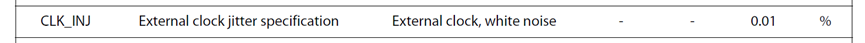

Lora芯片中的sigma-delta ADC直接使用外部晶振进行作为ADC的采样时钟,同时对该时钟的抖动提出了要求,单位表示为百分数,如图1所示,它是什么意思?

图1 Lora芯片中的ADC对于外部时钟抖动的要求

时钟抖动可分为三种抖动类型:时间间隔误差TIE(Time Interval Error)、周期抖动PJ(Period Jitter)和相邻周期间抖动CCJ(Cycle to Cycle Jitter)。周期抖动是多个周期内对时钟周期的变化进行统计与测量的结果,相邻周期间抖动是时钟相邻周期的周期差值进行统计与测量的结果,由于这两种抖动是单个周期或相邻周期的偏差,表征的是短期抖动行为。时间间隔误差又称为相位抖动(Phase Jitter),是指信号在电平转换时,其边沿与理想时间位置的偏移量,通常表征的是长期抖动行为。

从时钟抖动的来源分析,可以把抖动归纳为两大类:确定性抖动和随机性抖动。

确定性抖动是由可识别的干扰信号造成的,这种抖动通常幅度有限,具备特定的(而非随机的)产生原因,而且不能进行统计分析。造成确定性抖动的来源主要有4种:

- 相邻信号走线之间的串扰:当一根导线的自感增大后,会将其相邻信号线周围的感应磁场转化为感应电流,而感应电流会使电压增大或减小,从而造成抖动。

- 敏感信号通路上的

EMI辐射:电源、AC电源线和RF信号源都属于EMI源。与串扰类似,当附近存在EMI辐射时,时序信号通路上感应到的噪声电流会调制时序信号的电压值。- 多层基底中电源层的噪声:这种噪声可能改变逻辑门的阈值电压,或者改变阈值电压的参考地电平,从而改变开关门电路所需的电压值。

- 多个门电路同时转换为同一种逻辑状态:这种情况可能导致电源层和地层上感应到尖峰电流,从而可能使阈值电压发生变化。

随机抖动是不能预测的噪声源,如热噪声(Johnson噪声或散粒噪声),以及半导体加工工艺的局限性等。由于随机噪声是由多种不相关的噪声源叠加的,根据统计理论可以用高斯分布来描述其特性,由此可以得到下面两种对随机抖动幅度的表征:

- 均值

(RMS)抖动,即高斯分布一阶标准偏差δ。一般采用规定的滤波器带宽内的RMS抖动,如光通信领域常用的积分带宽是(12KHz~20MHz)。该值随样本数的增加变化不大,因而这种测量较有意义。但这种测量只在纯高斯分布中才有效,如果分布中存在任何确定性抖动,那么利用整个抖动直方图上的一阶方差来估计抖动出现的可能性就是错误的。- 峰峰值

(Peak to Peak)抖动,即高斯正态曲线上最小测量值到最大测量值之间的差值。根据系统误码率要求的不同,最小和最大值的取值是不一样的,如误码率为10^(-12)时,峰峰值约等于14倍的标准差,即14δ。在大多数电路中,该值会随测量样本数的增多而变大,理论上可达无穷大。因此,这种测量意义不大。- 多个随机抖动源可以用

RMS方式相加。但要得到总的抖动,需要利用峰峰值,以便将随机抖动与确定性抖动相加。

抖动值还可以用其他单位表示,例如单位时间(UI,代表时钟主频的周期)或时间,如图1 Lora芯片中的ADC对于外部时钟抖动的要求所示,其代表假设相位抖动服从高斯分布,均方根值δ为0.01%UI。假设时钟为36M,则时钟抖动均方根值为2.78ps,如果是32M则为3.125ps。

那么为什么在Lora的sigma-delta电路中对于时钟抖动的均方根要求是2.78ps~3.125ps呢?

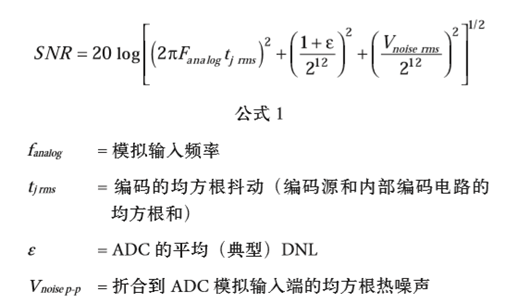

- 一般ADC中抖动对于SNR的影响:

图2 一般ADC的时钟抖动对于信噪比的影响(包含孔径抖动和输入时钟抖动)

对于连续时间sigma-delta转换器而言对于孔径抖动的要求貌似要稍宽于奈奎斯特速率的ADC。连续采样时间sigma-delta转换器架构中有一个过采样系统,并且为了精确的实现输入信号到ADC,大量的输出数据需要被平均。每个样本的抖动贡献都是均方根,与奈奎斯特的孔径抖动对于每次采样输出的直接影响相比,连续采样时间sigma-delta的时钟抖动对于噪声性能的影响显得更加不明显。

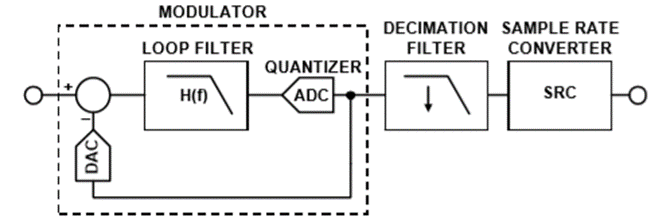

图3 sigma-delta调制器框图

在图3中我们可以看到有两个模块容易受到时钟抖动的影响,那就是量化器和DAC。误差是通过量化过程引入的,但是通过环路增益和类似作用于量化噪声那样的噪声成型技术可以让抖动对量化过程中引入的误差变得忽略不计。但是相反,与DAC有关的时钟抖动错误直接叠加在输入信号端,因此增加了信号带内噪声功率,恶化了调制器的性能,对于信噪比的影响可以使用下式表达。

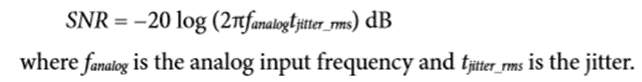

图4 sigma-delta的抖动影响近似

当模拟输入信号是125KHz,时钟抖动是3.125ps时,信噪比为112.2dB,如果输入500k信号,时钟抖动是3.125ps时,信噪比是100dB。当然ADC内部还有孔径抖动,还会进一步恶化信噪比。

4552

4552

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?