文章目录

一、绪论

1.Principle of Equivalence (对等原则) of Hardware and Software:

Any task done by software can also be done using hardware, and any operation performed directly by hardware can be done using software.

2.单位换算

1KB = 210 = 1024 Bytes

1MB = 220 = 1,048,576 Bytes

1GB = 230 = 1,099,511,627,776 Bytes

1Byte = 8 bits

3.发展历史

第零代:机械计算机

Difference Engine (差分机) - Charles Babbage (1791 - 1871)

Punched card tabulating machines (穿孔制表机) - Herman Hollerith (1860 - 1929)

第一代:电子管计算机

Electronic Numerical Integrator and Computer (ENIAC) - John Mauchly and J. Presper Eckert - University of Pennsylvania, 1946

ENIAC被公认为第一个全电子的通用数字计算机。

第二代:晶体管计算机

IBM 7094 (scientific) and 1401 (business)

第三代:集成电路计算机

IBM 360

第四代:超大规模集成电路计算机

世界上第一个微处理器——4004(全功能的4位系统)

4.摩尔定律、洛克定律

(1)Moore’s Law:The density of transistors in an integrated circuit will double every year.(在一个集成电路中晶体管的密度将会每年翻一番)

(2)Rock’s Law:The cost of capital equipment (资产设备) to build semiconductors will double every four years.(建立半导体工厂的主要设备的成本每四年翻一番)

5.计算即服务

(1)软件即服务(SaaS):The consumer of this service buy application services.

(2)平台即服务(PaaS):Provides server hardware, operating systems, database services, security components, and backup and recovery services.

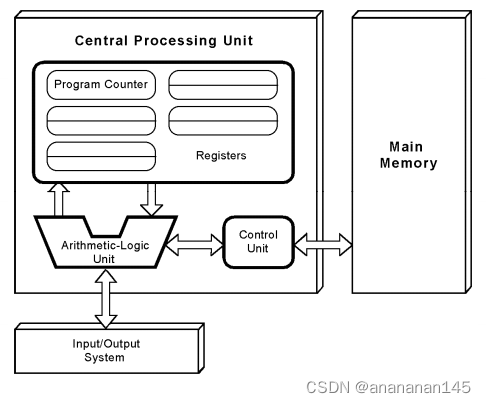

6.冯·诺依曼体系架构

由以下三部分硬件系统组成:

①中央处理单元CPU——控制单元、算术逻辑单元ALU、寄存器和程序计数器

②主存储器系统

③I/O系统

von Neumann bottleneck (冯·诺依曼瓶颈):A single data path between the CPU and main memory.(在主存储器系统和CPU的控制单元之间包含一条单一路径)

非冯·诺依曼体系架构

冯·诺依曼计算机顺序执行指令,因此非常适合顺序处理。非冯·诺依曼计算机不把程序和数据存储在存储器中或者不按顺序处理程序。

eg.哈佛架构——计算机有两根总线,允许同时传送数据和指令。

二、计算机系统中的数据表示

1.bit,byte,word之间的转换

①A bit (位、比特) is the most basic unit of information in a computer.

②A byte (字节) is a group of eight bits.

③Words can be any number of bits or bytes.

2.进制之间的转换(2,8,10,16)

3.原码,反码,补码

One’s complement——反码

Two’s complement——补码

正数的反码=原码,

负数的反码=原码除了符号位都取反,

负数的补码=负数的反码+1

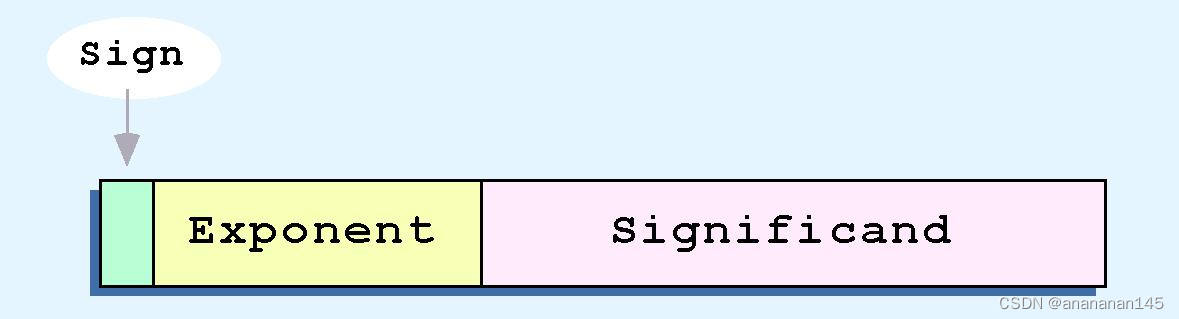

4.浮点数

在数字计算机中,浮点数有符号位、指数部分和小数部分组成。

The sign field is 1 bit

The exponent field is 5 bits

The significand field is 8 bits

excess-15 biased exponent (to avoid representing negative exponents)

使用偏移值为15的移码表示法

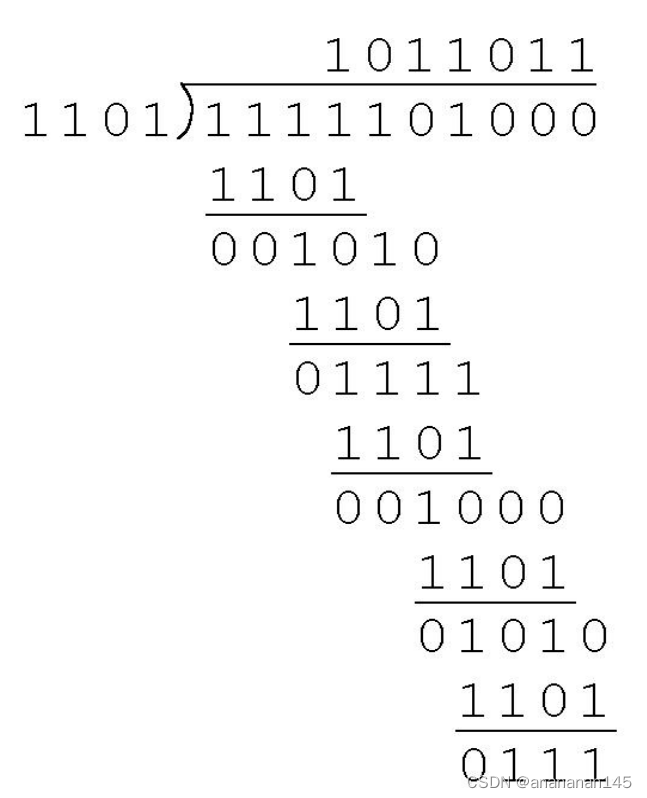

5.Cyclic Redundancy Checks (CRCs,循环冗余码校验)

信息字节=1111101,P=1101,信息字节加上P的位数-1个零,再除以P,执行异或除法,余数0111就是实际的CRC检验和。

6.汉明距离

汉明距离是指在两个码字中有多少位不同。

在这个编码中所有两个码字之间的最小汉明距离称为编码的最小汉明距离。

代码的汉明距离必须至少为2k+1以能够纠正k个错误。

三、布尔代数与数字逻辑

1.布尔运算

XOR——异或

NOR——或非

NAND——与非

四、一个简单的计算机模型MARIE(重点)

1.CPU基础

每个计算机都有一个CPU,它分为两部分——数据通路(datapath)和控制单元(control unit),数据通路是一种由存储单元和算术逻辑单元组成的网络。

(1)寄存器

寄存器是一种存储二进制数据的硬件设备

一个D触发器相当于一位寄存器

寄存器包含数据、地址或控制信息

寄存器是由CPU内部的控制单元进行编址和处理的

(2)算术逻辑单元ALU

功能:用于执行逻辑运算和算术运算

一般情况下,ALU有两个数据输入和一个数据输出

(3)控制单元control unit

功能:负责监视所有指令的执行和各种信息的传输过程;负责从存储器中取指令,对这些指令进行译码,确保数据适时地出现在正确的地方;负责通知ALU应该使用哪一个寄存器,执行哪些中断服务程序。

控制单元使用程序计数器来寻找下一条要执行的指令

2.总线

总线可以以点对点的方式连接两个特定的设备,也可以多个设备共享总线(多点总线)。

一个总线包括——数据总线、地址总线、控制总线、地址总线

四种总线仲裁机制

1.Daisy chain arbitration (菊链式仲裁)——最高级优先

2.Centralized parallel arbitration (集中式平行仲裁)——有一个到总线的请求控制器和仲裁控制器

3.Distributed arbitration using self-selection (自选择的分配式仲裁)——自己决定谁获得控制权

4.Distributed arbitration using collision-detection (冲突检测的分配式仲裁)——以太网使用,如果设备检测到任何冲突,则必须发出另一个请求

3.存储器的组成和寻址方式

(1)存储器可以按字节编址,也可以按字编址。

(2)存储器由随机存取存储器(RAM)芯片构成。

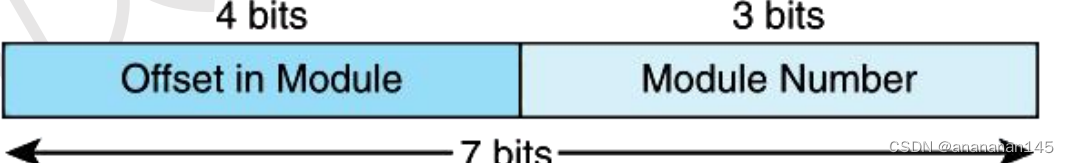

(3)交叉存储器

低位交叉——地址的低位用于选择模块

高位交叉——地址的高位用于选择模块

采用低位交叉时,Module Number(模块号)在低位,Offset in Module(模块内偏移量)在高位。

4.中断

中断是改变系统中流程正常执行的各种事件。

判断(×):Interrupt checking is typically carried out at various times during the execution of a machine instruction.

中断检查通常在指令结束后执行。

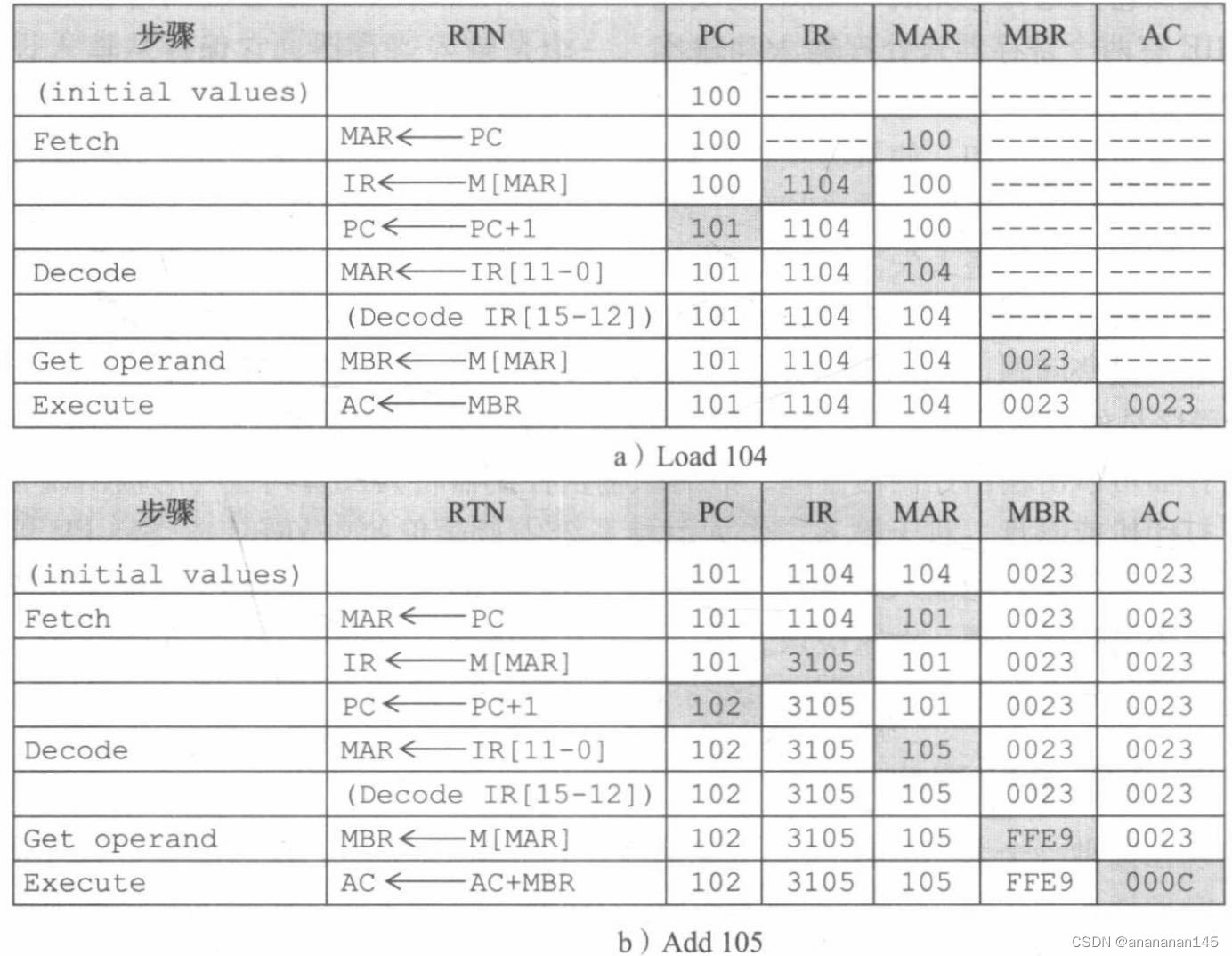

5.MARIE(Machine Architecture that is Really Intuitive and Easy)

(1)MARIE’s seven registers

①Accumulator (累加器), AC:16-bit,holding data that the CPU needs to process.(保存CPU需要处理的数据)

②Memory address register (存储器地址寄存器), MAR:12-bit,holds the memory address of an instruction.(保存所引用数据的地址)

③Memory buffer register (存储器缓冲寄存器), MBR:16-bit,holds the data after its retrieval from, or before its placement in memory.(保存刚从存储器中读取或者将要写入存储器中的数据)

④Program counter (程序计数器), PC: 12-bit,holds the address of the next program instruction to be executed.(保存程序要执行的下一条指令的地址)

⑤Instruction register (指令寄存器), IR:16-bit,holds an instruction immediately preceding its execution.(保存将要执行的下一条指令)

⑥Input register (输入寄存器), InREG:8-bit,holds data read from an input device.(保存来自输入设备的数据)

⑦Output register (输出寄存器), OutREG:8-bit, holds data that is ready for the output device.(保存要输出到输出设备的数据)

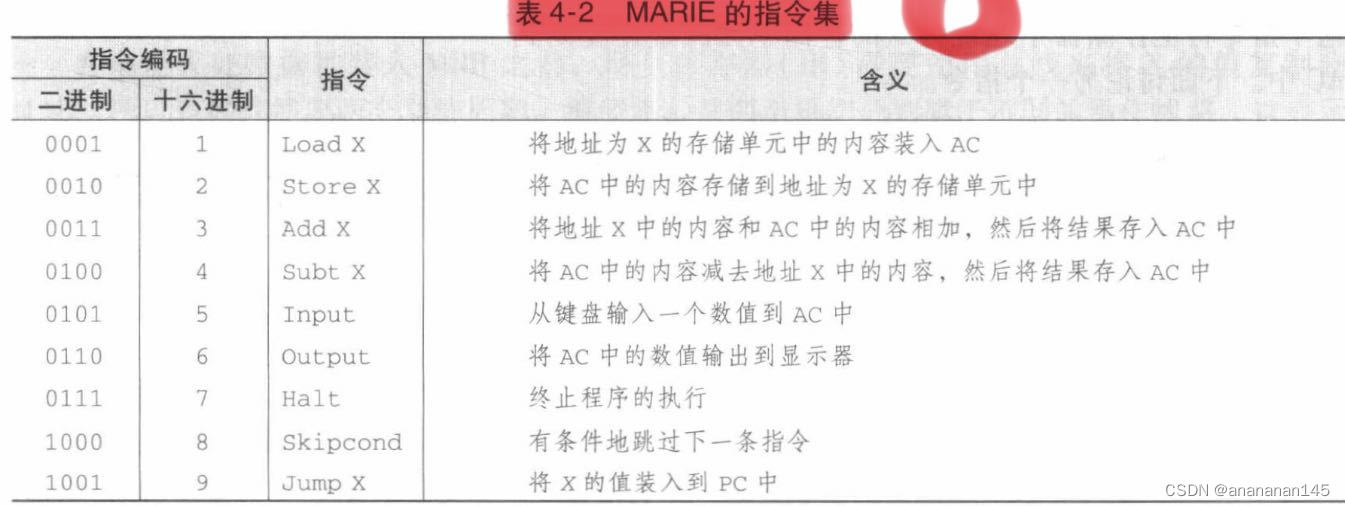

(2)指令集架构ISA(Instruction Set Architecture)

ISA指定了计算机可以执行的指令及其格式。

(3)寄存器传输表示(要会写)

①Load X——把存储单元X的内容加载到AC中

MAR ⬅X

MBR ⬅ M[MAR]

AC ⬅ MBR

②Store X——把AC中的内容存储到存储单元X中

MAR⬅X

MBR⬅AC

M[MAR]⬅MBR

③Add X——存储在地址X中的值加到AC中

MAR⬅X

MBR⬅M[MAR]

AC⬅AC + MBR

④Subt X——从累加器中减去存储在地址X的值,把结果放回AC

MAR⬅X

MBR⬅M[MAR]

AC⬅AC - MBR

⑤Skipcond

6.各种体系架构的优缺点

(1)Intel体系架构

(2)MIPS体系机构

MIPS是一种装载/存储体系结构。

五、仔细审视指令集架构

1.指令格式

(1)指令集架构衡量因素:

程序占用空间的大小

指令集的的复杂程度

指令的长度

指令的总条数

(2)

①定长指令(fixed length)——译码相对容易,速度快但是浪费存储空间

在定长指令中操作数的个数并非固定不变的。

②变长指令(variable-length)——译码更复杂但是节省空间

MARIE系统使用定长指令,包括4位操作码(opcode)和12位操作数(oprand)

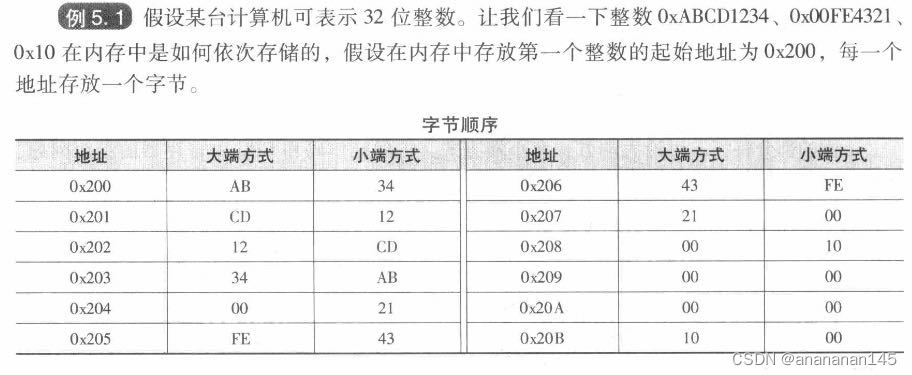

(3)端

大多数UNIX采取大端方式,而个人计算机多用小端方式。

2.三种架构

(1)A stack architecture (堆栈体系架构)

操作数隐式地存放在栈顶

不能随机访问一个堆栈

没有操作数的机器指令必须使用堆栈

(2)An accumulator architecture (累加器体系架构)

操作数隐式存放在累加器中

(3)A general purpose register architecture (通用寄存器体系架构)

被现代计算机体系结构所采纳,现在应用最广泛

3.逆波兰式(后缀表达式)

操作符放在操作数之后

eg.Z = (X × Y) + (W × U)

➡Z = X Y × W U × +

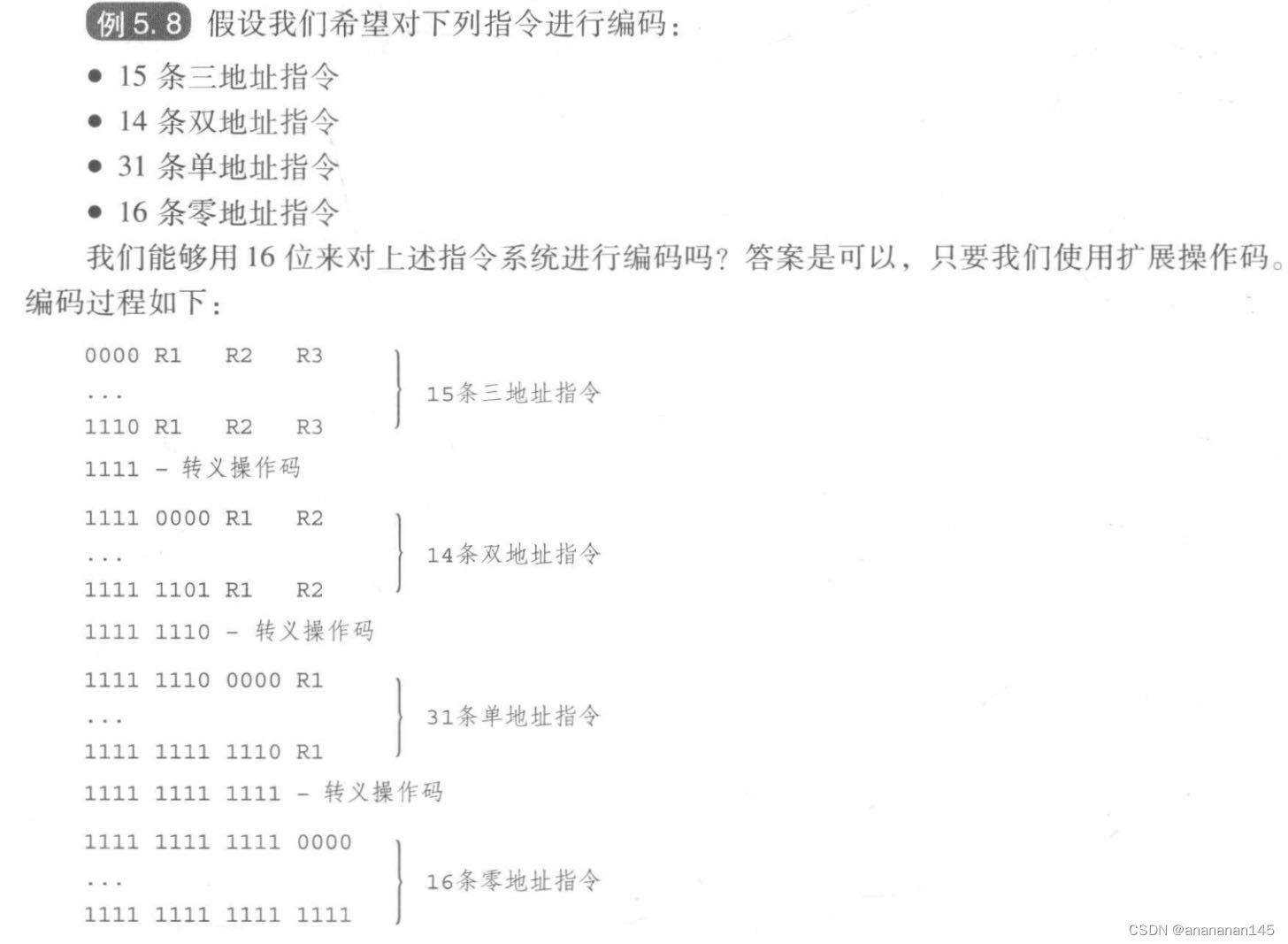

4.扩展操作码(重点)

题型一、转义操作码

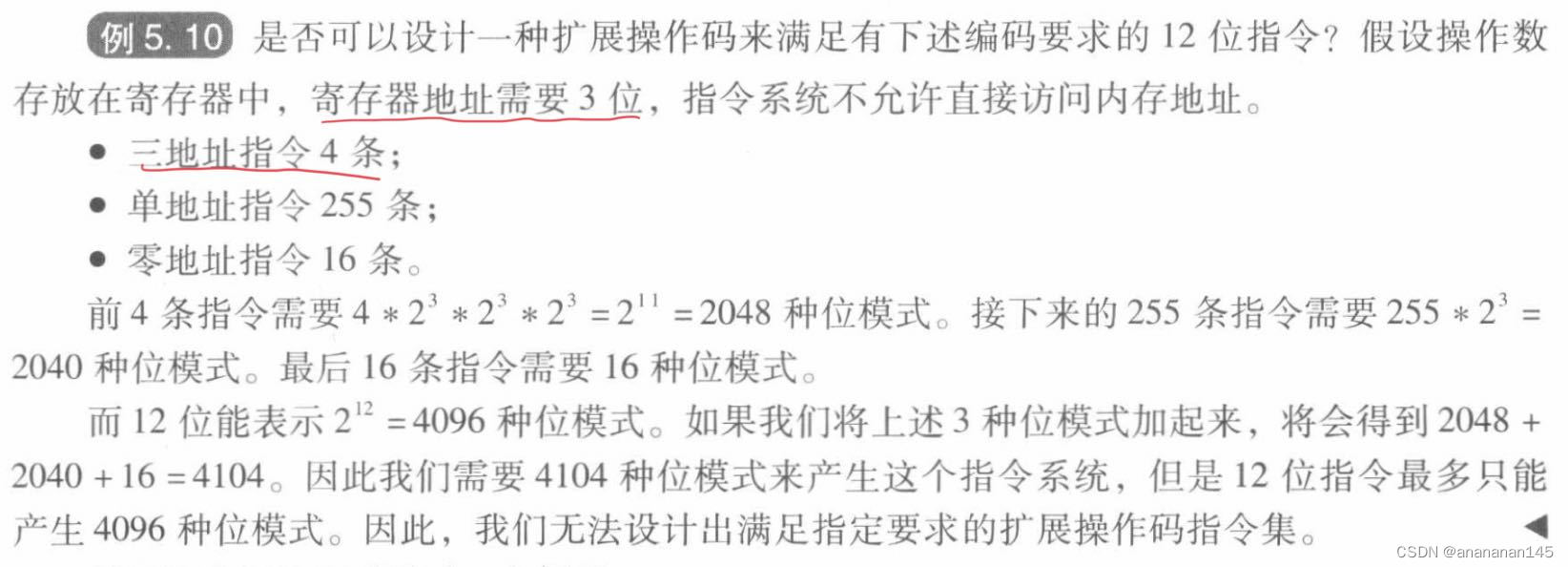

题型二、计算位模式个数,判断是否满足编码要求

注意到寄存器地址要3位,所以三个地址需要九位,前四条指令需要4*29=2048种位模式。

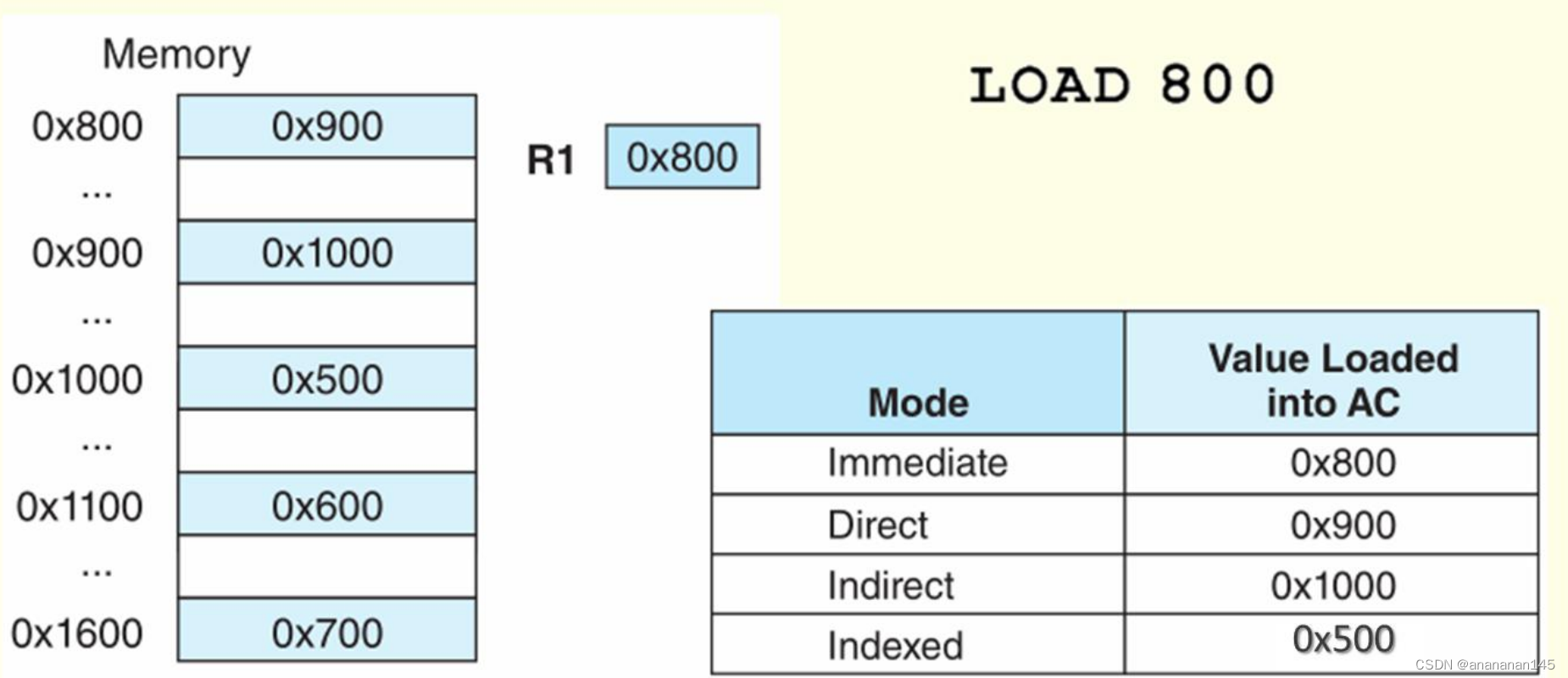

5.寻址方式

1.立即寻址(Immediate Addressing)

2.直接寻址(Direct Addressing)

3.间接寻址(Indirect Addressing)

4.变址寻址(Indexed Addressing)

➡在变址寻址中,0x800加上R1中的0x800=0x1000(十六进制),最后寻到地址0x1000里的0x500。

6.指令流水线(instruction pipelining)

fetch-decode-execute(取指-译码-执行) cycle were broken into the following smaller steps:

- Fetch instruction取指令

- Decode opcode译码

- Calculate effective address of operands计算操作数的有效地址

- Fetch operands取操作数

- Execute instruction执行指令

- Store result保存结果

时钟周期为tp,k段流水线完成n个任务需要时间:(k + n - 1)tp

加速比:ntn/(k + n - 1)tp

三种流水线冲突:

(1)资源冲突Resource conflicts

(2)数据依赖Data dependencies

(3)条件转移语句Conditional branching

7.三种指令集架构实例

(1)Intel

小端存储,双地址结构,变长指令,寄存器-存储器型

(2)MIPS

小端存储,按字寻址,三地址结构,定长指令,只有装载/存储指令可以访问存储器

(3)JAVA虚拟机

JAVA字节码基于堆栈语言,字符用16位Unicode编码,不允许使用无符号整数

(4)ARM

长三操作数指令,简单寻址

装载/存储结构,所有的数据处理必须通过寄存器中的值来处理

六、存储器

1.存储器类型

(1)随机存取存储器RAM——易失性

现代计算机中有两种通用芯片来构造大容量的RAM:SRAM静态随机存取存储器和DRAM动态随机存取存储器。SRAM比DRAM速度更快,价格更贵。

(2)只读存储器ROM——非易失性,长久保存数据

常用于嵌入式系统或者任何不需要改变程序的系统

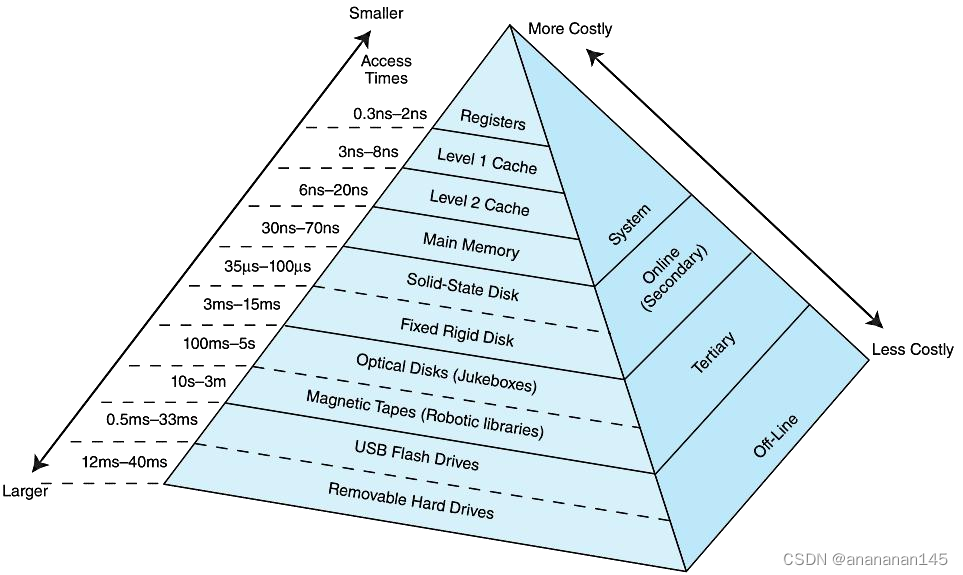

2.存储器的层次结构

为了解决存储器之间的差异,现代计算机系统采用多类型存储器的组合,从而以最优的价格提供最好的的性能,这种方法称为分层存储器(hierachical memory)。

处理器可以直接访问寄存器。一般来说,寄存器访问需要一个时钟周期。

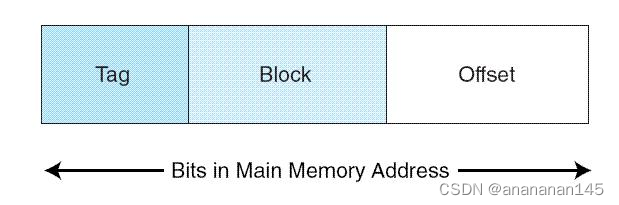

3.缓存映射策略(重点)

(1)Direct Mapped Cache直接映射缓存

若将主存块数加倍,则映射到同一块缓存的主存块数也需要加倍。

(2)Fully Associative Cache全相联映射缓存

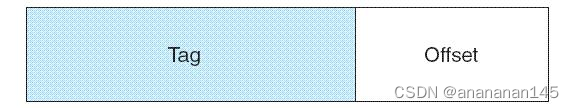

Tag (标记域) , Offset (偏移量域)

allowing a main memory block to be placed anywhere in cache.允许主存的每一个块映射到缓存的任意一个块中

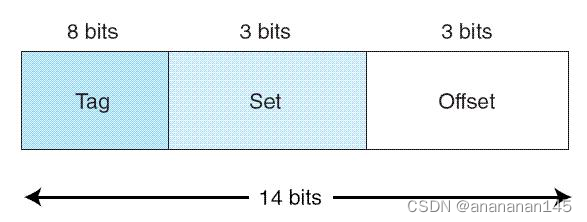

(3)Set Associative Cache组相联映射缓存

掌握相关计算还有跟踪缓存占用情况

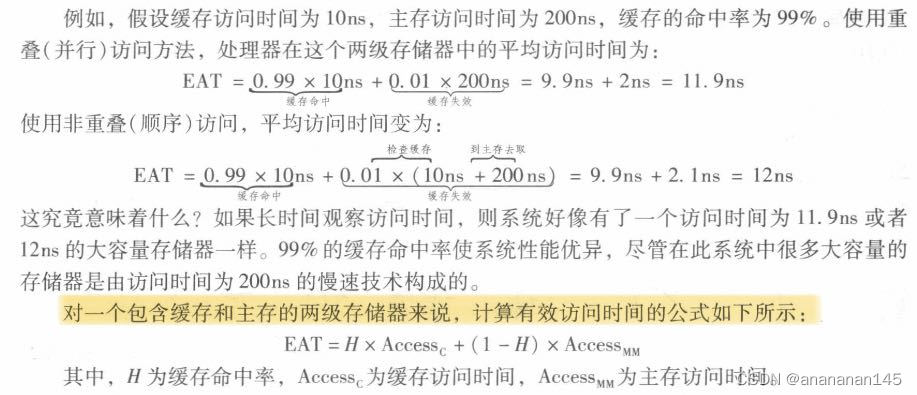

4.有效访问时间EAT

EAT =H × AccessC + (1-H) × AccessMM

H is the cache hit rate (缓存命中率) and AccessC and AccessMM are the access times for cache (缓存访问时间) and the access times for main memory (主存储器访问时间)

overlap/parallel 重叠/并行

5.缓存写策略

(1)写直通write through——同时更新缓存和主存

(2)写回write back——仅当某个缓存块被替换出去时才更新其对应的主存块

6.多级缓存层次结构multilevel cache hierarchies

L1缓存通常称为“内部缓存”,8~64KB

L2缓存64KB~2MB

L3缓存8~256MB

包容缓存(Inclusive cache)——允许数据同时出现在多级缓存

独占缓存(Exclusive caches)

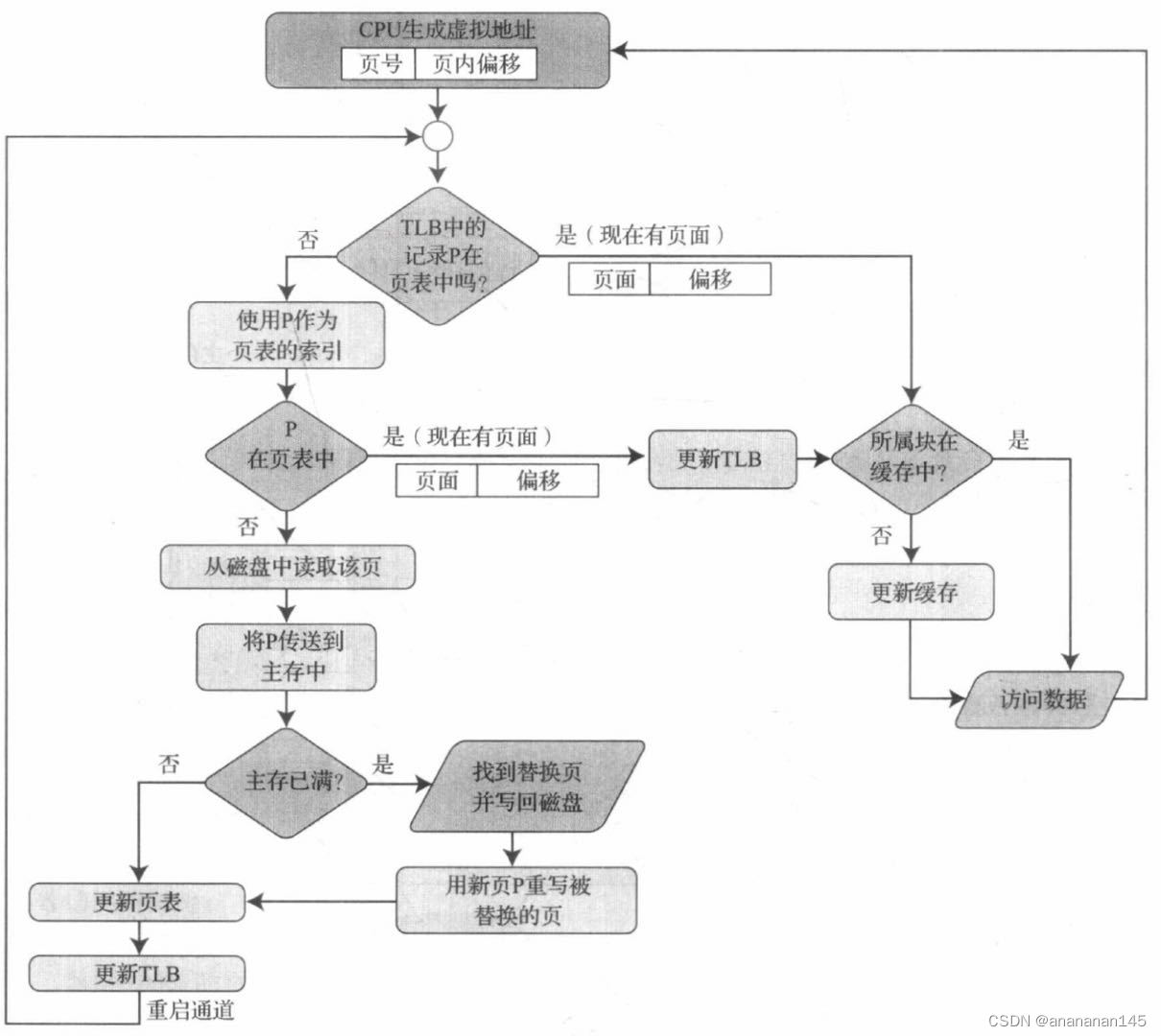

7.虚拟存储器

(1)

paging (分页)——a process of copying a virtual page from disk to a page frame in main memory.(将虚页从磁盘调入主存页面的过程)

Page faults (缺页)——when a requested page is not in main memory and must be copied into memory from the disk.

If the valid bit is 1, the virtual page number is replaced by the physical frame (页面) number.

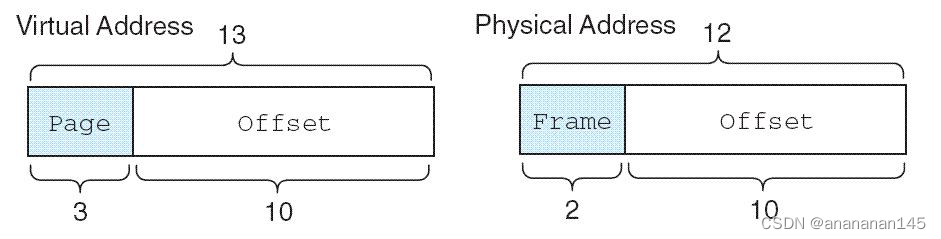

eg.Suppose a system has a virtual address space of 8K bytes and a physical memory address space of 4K bytes, the page size is 1K bytes, and the system uses byte- addressable.

(2)使用分页管理的EAT

主存访问需要200ns,页面失效率为1%,假设需要10ms来访问一个不在主存中的页。一次存储器的有效访问时间为:

EAT =0.99*(200ns +200ns) +0.01*(10ms) =100,396ns

(每次存储器访问都有两次物理主存的访问——一次是访问页表,一次是访问我们希望的实际数据)

(3)转换后援缓冲器TLB

TLB由相联缓存来实现。下面是使用TLB完成地址查找所需的必要步骤:

①从虚拟地址中提取页号

②从虚拟地址中提取出页内偏移

③在TLB中使用并行查找技术来搜索虚拟页号

④如果(虚拟页号#,物理页号#)对在TLB中找到了,则将偏移字段放在物理页号后边,访问主存地址

⑤如果产生了TLB失效,则去访问页表以取出对应的页面号,并更新TLB。如果该页在主存中,则使用对应的页面编号和页内偏移组合来产生物理地址

⑥如果该页不在主存中,则会产生缺页故障/页面失效,并会在处理完缺页故障后,重新启动此次访问

(4)汇总(掌握流程、能复述清楚)

(5)分页、分段

外部碎片——由于段是可以不断分配的,因此主存中的空闲块会变得破碎,最终,主存里会有很多小块,但是没有一块能存放下整个段

内部碎片——由于进程可能不需要页面中包含的整个地址范围,因此,可能有许多页面包含未使用的内存片段。

分页消除了外部碎片,易于管理;

分段消除了内部碎片,可以支持共享和保护。

段页式允许从用户的角度对程序进行分段,又允许从系统的角度对主存进行分页。

七、I/O和存储系统

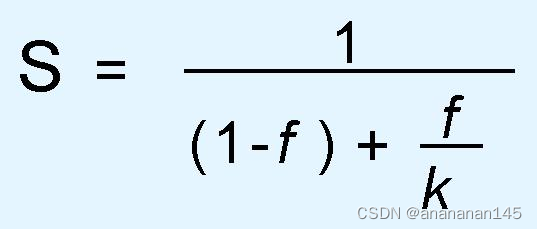

1.Amdahl’s Law 阿姆达尔定律

其中,S代表系统整体性能的加速比;f代表由较快部件完成的部分;k是新部件的加速比。

2.I/O控制方法

(1)Programmed (程序控制的) I/O

一次传输一个字节

(2)Interrupt-Driven (中断控制的) I/O

(3)Memory-Mapped (内存映射的) I/O

每一个I/O的设备都有自己保留的存储块

(4)Direct Memory Access (DMA,直接存储器存取)

The DMA runs at a higher priority and steals memory cycles from the CPU(周期窃取)

(5)Channel (通道控制的) I/O

3.磁盘技术

寻道时间(seek time):磁盘驱动臂定位到指定磁道上所需的时间。

旋转延迟(rotational delay):读/写头定位到指定扇区上方所需要的时间。

存取时间=寻道时间+旋转延迟

传输时间=存取时间+磁盘读取数据时间

(1)固态硬盘(SSD)

优点:拥有比机械硬盘更低的寻道时间,抗摔防震效果明显,读写速度惊快

缺点:写入寿命有限,容量目前有限

两个标准:UBER和TBW

UEBR指不可恢复的误码率,为数据错误的数量除以在整个使用期内模拟所得的读取的总位数。

TBW指写入的百万兆字节,是在磁盘无法满足说明书中的速度和错误率之前可写入磁盘的百万兆字节数。

TBW是磁盘耐久性的度量,UEBR是磁盘可靠性的度量。

(2)光盘

①只读光盘驱动器(CD-ROM)

CD采用780nm长的激光

②数字通用光盘(DVD)

DVD是CD密度的4倍,旋转速度是CD的3倍,DVD采用的是650nm长的激光;

DVD纠错比CD减少了大量的冗余性,并提供了更好的数据保护。

③蓝光光盘

采用405nm的蓝紫色激光,存储空间更大

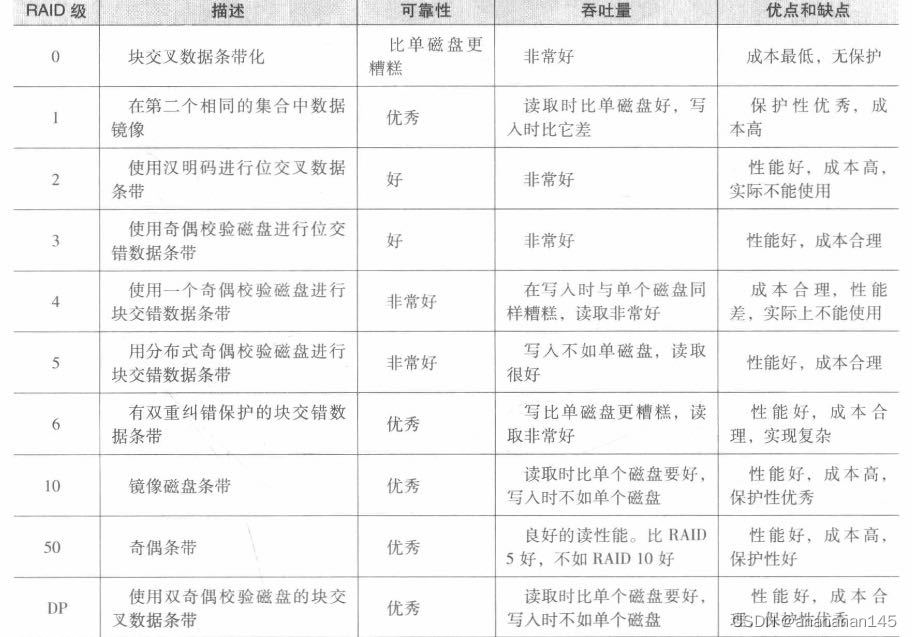

(3)RAID独立磁盘冗余阵列

3.数据库软件

(1)一个企业最宝贵的资源是它所拥有的数据。

(2)数据库管理系统的其中一个核心组件是事务管理器(transaction management components)

每个事务具有的属性:

原子性Atomicity

一致性Consistency

隔离性Isolation

持久性Durability

八、系统软件

1.保护环境

三种在系统中构建安全屏障的方式:virtual machines (虚拟机), subsystems (子系统), and partitions (分区)

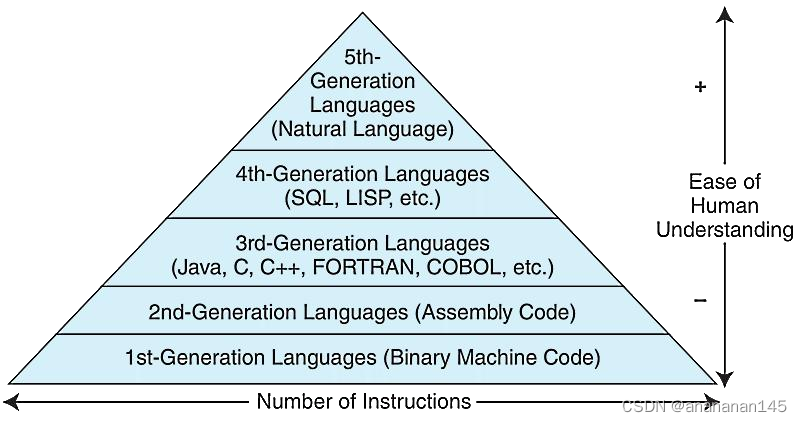

2.编译器

计算机只能理解第一层的二进制机器码

编译器把第二层的汇编代码翻译成第一层的机器码

九、可供选择的体系结构

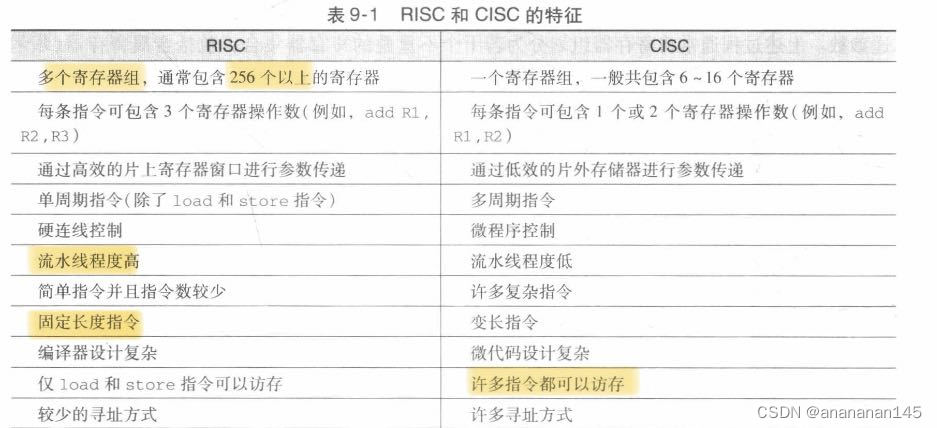

1.RISC和CISC对比

2.富林分类法(Flynn’s Taxonomy)

根据进入处理器的指令数和数据流数

SISD(单指令流单数据流)

SIMD(单指令流多数据流)

MISD(多指令流单数据流)

MIMD(多指令流多数据流)——其中,对称多处理器(SMP)和大规模并行处理器(MPP)区别在于如何使用主存

3.超流水线技术(Superpipelining)

当流水线中某些阶段的执行时间小于时钟周期的一半时,可以引入超流水线技术

4.cache coherence (缓存一致性) problems

①write-through cache update protocol (写直通缓存更新协议)——数据同时写入缓存和内存中

②write-through with update protocol (写直通更新协议)——新值消息广播到其他所有缓存控制器中,确保对其他x副本进行更新(维护所有的缓存,但增加通信量)

③write-through with invalidate protocol (写直通无效协议)

④write-back protocol (写回协议)——它在数据发生变化时仅改变缓存中的值,直到对应的缓存块被替换并写回主存时才发生改变

十、嵌入式系统专题

1.microcontroller (微控制器)

微控制器可编程,可访问各种外设。与通用处理器相比,工作主频更低、寻址空间更小,并且运行在其上的软件不能由用户修改。

看门狗定时器(watchdog timer)——guard against system hangs (挂起) and infinite loops by periodically checking for the system liveness.(通过定期检查系统活动性防止系统挂起或陷入循环)

通用计算机不需要看门狗,因为他们直接和人进行交互。

2.可重构硬件

①可编程阵列逻辑PAL——可编程的与门和固定的或门

②可编程逻辑阵列PLA——或门和与门都提供熔丝或开关

其中,PLA比PAL更加灵活,但速度慢,成本更高。

③现场可编辑逻辑门阵列FPGA——通过一个由交叉开关和多路复用连接构成的路由结构进行互连

3.Memory footprint (内存占用)

内存占用是嵌入式操作系统的一个关键问题。如果操作系统占用太多内存,则可能需要额外的内存,而内存消耗电量。 因此,操作系统越小越好。

4.中断嵌套(interrupt nesting)

中断系统正在执行一个中断服务时,有另一个优先级更高的中断提出中断请求,这时会暂时终止当前正在执行的级别较低的中断源的服务程序,去处理级别更高的中断源,待处理完毕,再返回到被中断了的中断服务程序继续执行的过程。

十一、名词解释

- CPU: Central processing Unit 中央处理单元

- ALU: Arithmetic-Logic Unit 算数逻辑单元

- PC: Program Counter 程序计数器

- CRC: Cyclic Redundancy Checking 循环冗余校验

- Hamming Code:汉明码

- Reed-Solomon Code: 里德-所罗门码

- MUX: Multiplexer 多路复用器

- ISA: Instruction Set Architecture 指令集架构

- CISC: Complex Instruction Set Computer 复杂指令集计算机

- RISC: Reduced Instruction Set Computer 精简指令集计算机

- ISR: Interrupt Service Routine 中断处理程序

- IVT: Interrupt Vector Table 中断向量表

- MARIE: Machine Architecture that is Really Instuitive and Easy

- AC: Accumulator 累加寄存器

- MAR: Memory Address Register 存储器地址寄存器

- IR: Instruction Register 指令寄存器

- RTN: Register Transfer Notation 寄存器传输表示

- RTL: Register Transfer Language 寄存器传输语言

- RAM: Random Access Memory 随机存取存储器

- ROM: Read-Only Memory 只读存储器

- GPR: General-purpose Register 通用寄存器

- RPN: Reverse Polish Notation 逆波兰式

- ILP: Instruction-Level-Parallelism 指令集并行

- MIPS: Microprocessors without Interlocked Pipeline Stages 没有互锁流水线阶段的微处

理器。 - EAT: Effective Access Time 有效访问时间

- CAM: Content Addressable Memory 按内容寻址存储器

- FIFO: First-in First-out 先入先出策略

- LRU: Least Recently Used 最近最少访问(使用)

- SRAM: 静态随机存取存储器

- DRAM: 动态随机存取存储器

- MMU: Memory Management Unit 内存管理单元

- TLB: Translation Lookaside Buffer 转换后备缓冲器

- I/O: Input/Output 输入输出

- DMA: Direct Memory Access 直接内存访问

- RDMA: Remote DMA 远程直接内存访问

- HDD: Hard Disk Driver 硬盘驱动器

- SSD: Solid State Disk 固态硬盘

- RAID: Redundant Array of Independent Disk 独立磁盘冗余阵列

- NVMe: Non-Volatile Memory Express 非易失性内存接口

- PV: Paravirtualization 半虚拟化

- LPAR: Logical Partition 逻辑分区

- KVM: Kernal-based Virtual Machine 基于内核的虚拟机

- HVM: Hardware Virtual Machine 硬件虚拟化/全虚拟化

- VMX: Virtual Machine Extension 虚拟机扩展指令

- DLL: Dynamic Link Library

- GC: Garbage Collection 垃圾回收

- JVM: Java 虚拟机

- JIT: Just-in-time 即时编译

- ACID: 原子性 一致性 隔离性 持久性

- MPP: Massive Parallel Processor 大规模并行处理

- RPC: Remote Procedure Call 远程过程调用

- SMP: Symmetric Multiprocessor 对称多处理器

- VLIW: Very Long Instruction Word 超长指令字体系结构

- UMA: Uniform Memory Access 统一内存访问

- NUMA: Non-uniform Memory Access 非统一内存访问

7660

7660

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?