因为项目上用到的是 海思3536的bt1120接口对接 FPGA。项目上用到的是 1920 x 1080@60Hz. 和 3840 x 2160@30hz.

首先讲一下 1920X1080@60HZ,这里走bt1120接口,走的是单边沿。下面 具体讲一下。

上图看到, BT1120的接口 有 16根 数据线 和 一根 时钟线。

下面说一下接口的时序及说明。

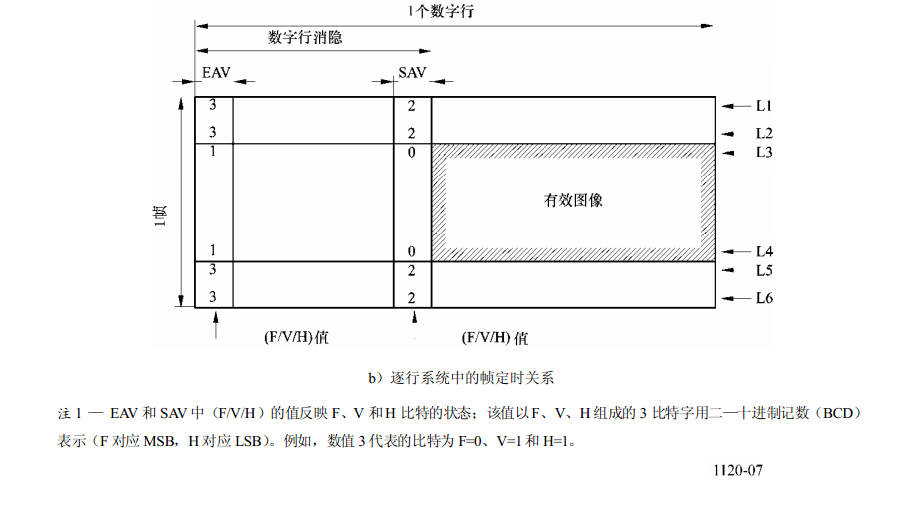

对于一帧视频图像,有视频帧消隐区和 行消隐区。这些概念首先得明白,才能往下看。

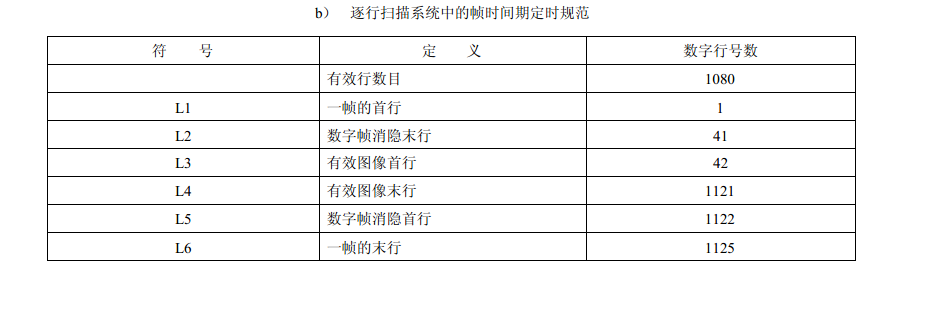

上图我们看到视频中的某一帧的状态。L1 和 L2 是帧消隐区, 同样 L5 和 L6也是帧消隐区。我们看看下图,来说明各个参数的意义。

从上图我们看到了再 L3 和 L4行之间才是真正的有用的 1080行视频数据。

下面我们看看每行的数据的格式:

和

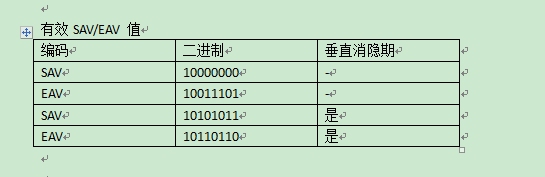

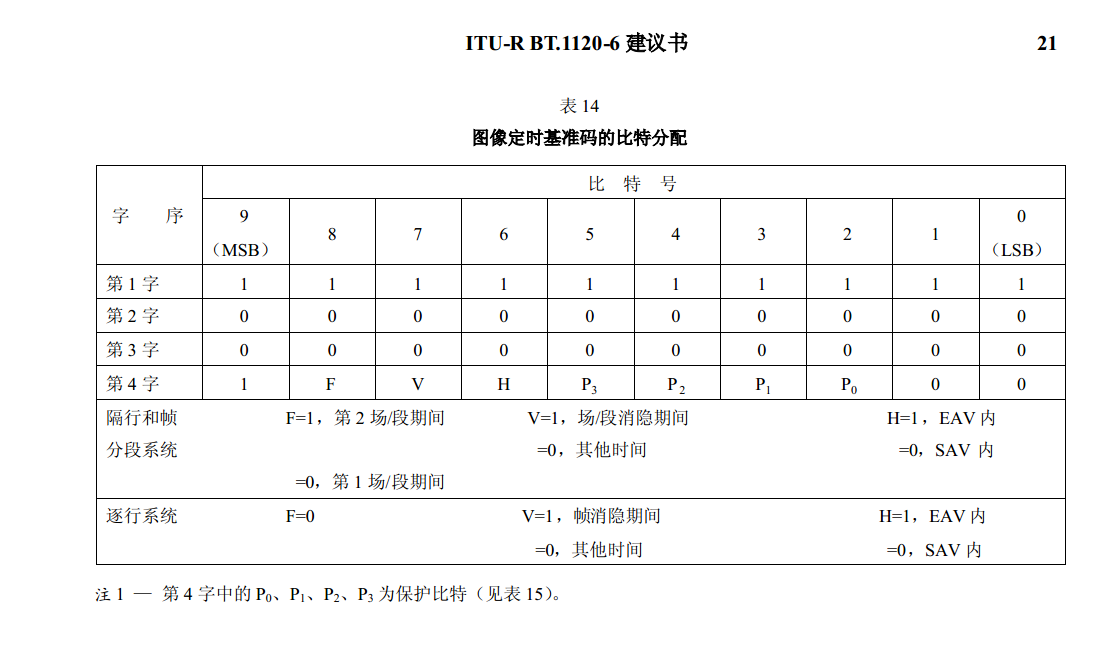

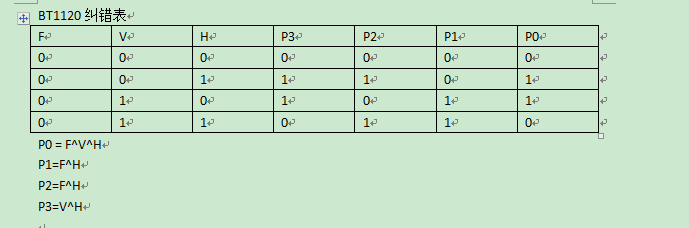

由上面的格式, 我们可以看到每一行在视频传输过程中的格式。在定时基准码的前 3个字节是恒定的。 FF , 00 , 00, 第四个字节 XY是我们需要分析的。我们再好好分析下,EAV和SAV 应该填的数据。

通过以上几个图片,就应该可以知道 EAV 和 SAV可以填什么数据了。也知道 BT1120每行的数据格式。

至于 3840 x 2160@30hz走的是 BT1120的双边沿。

格式是

这里 XY的值 和 单边沿是一样的。只是速率提高了一倍。这样就可以通过 BT1120传输 4k的视频。

211

211

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?