全志A33下面,讲解配置LVDS时序,支持12.1寸屏

最新推荐文章于 2024-08-05 13:57:29 发布

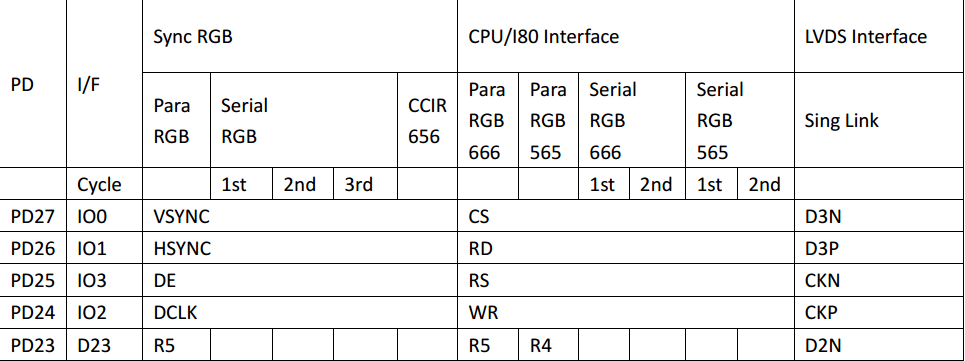

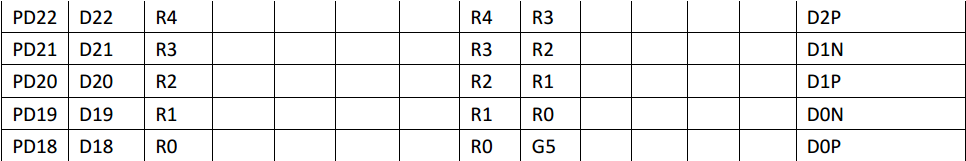

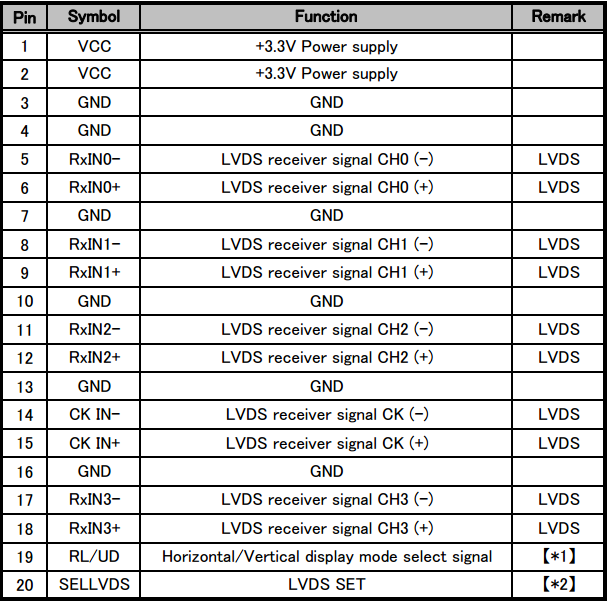

本文详细介绍了在全志A33芯片上配置LVDS时序以支持12.1英寸显示屏的过程。内容包括原理图与管脚定义、时序分析,以及在sys_config.fex文件中修改参数的方法。通过调整行周期、列周期、HBP、HSPW、VBP和VSPW等参数,成功点亮屏幕。

本文详细介绍了在全志A33芯片上配置LVDS时序以支持12.1英寸显示屏的过程。内容包括原理图与管脚定义、时序分析,以及在sys_config.fex文件中修改参数的方法。通过调整行周期、列周期、HBP、HSPW、VBP和VSPW等参数,成功点亮屏幕。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

3003

3003

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?