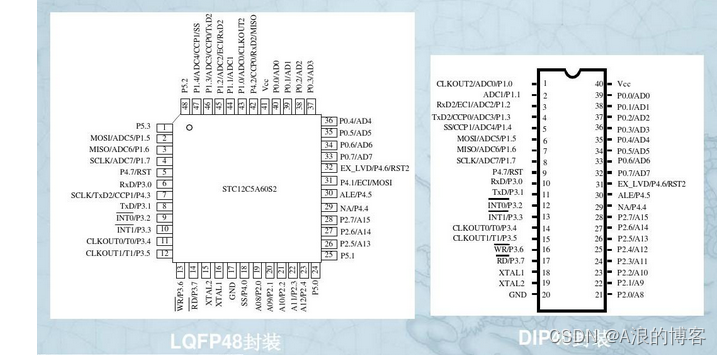

直接上图:

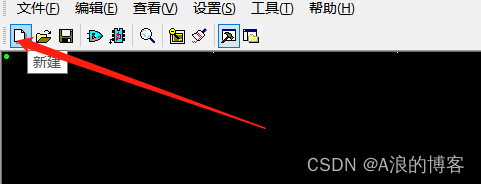

1、打开PadsLogic。

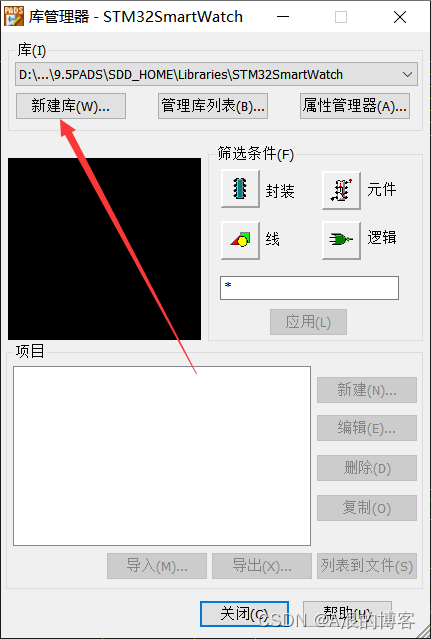

2、建立自己的项目库,建议每个项目都新建一个库来存放封装和原理图。

点击文件→库→新建库

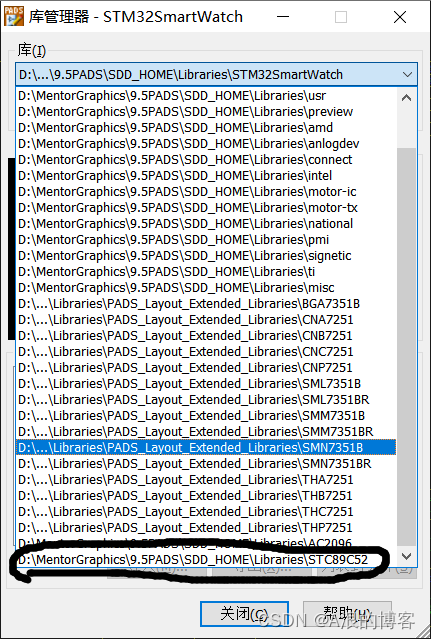

2.2我们建好自己的库之后会在库的下拉菜单中找到刚才新建的库,我这里的命名是STC89C52。

至此,我们的项目库已经建完了。

3、新建完的库什么都没有,那么接下来我们开始原理图库的编辑。

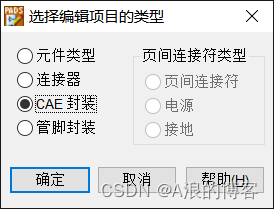

3.1流程:工具→元件编辑器→新建→CAE封装

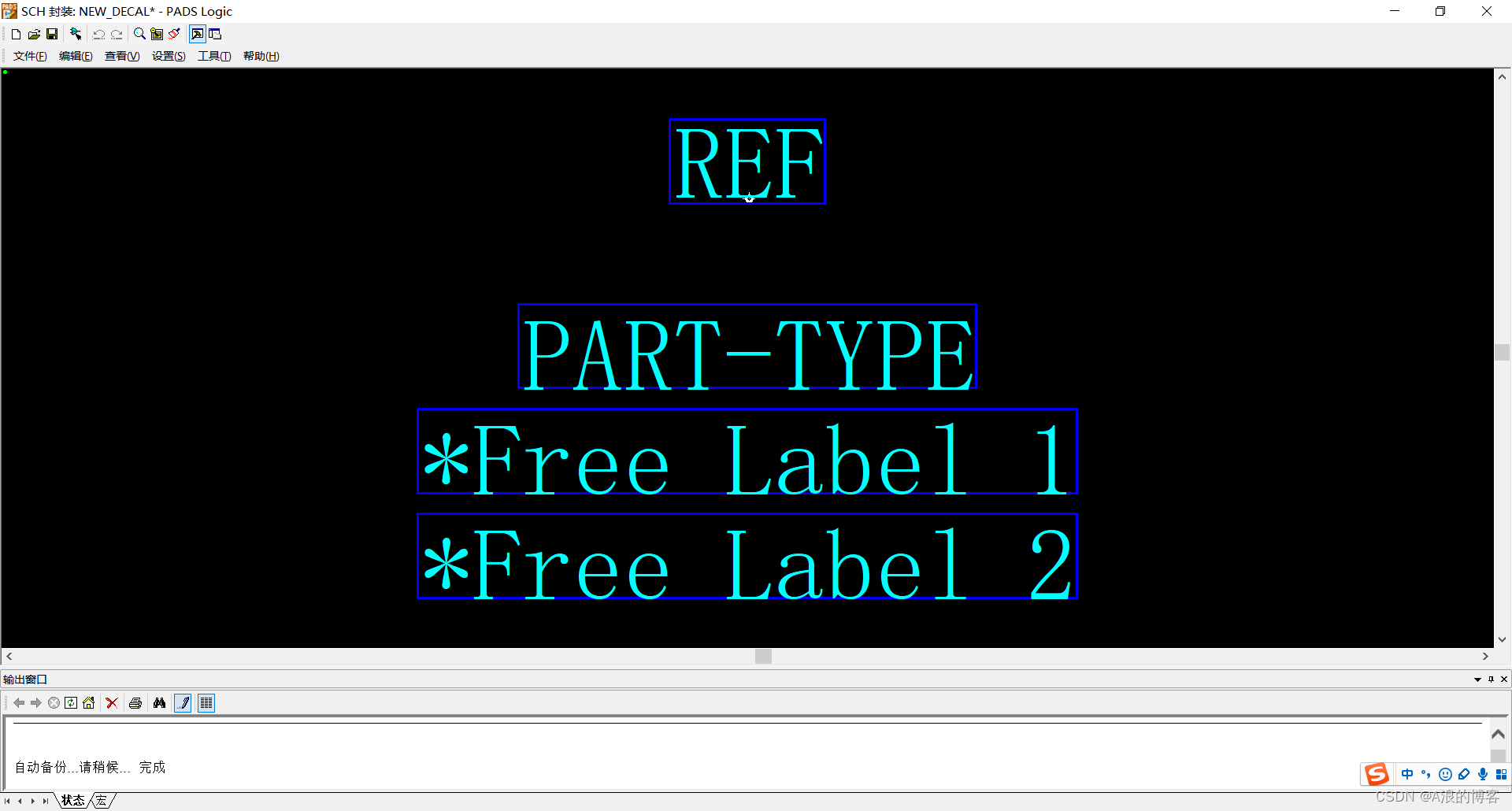

通常这里我们选择CAE封装然后点确定就好了,其他的不用管。接下来是这个界面就对了。

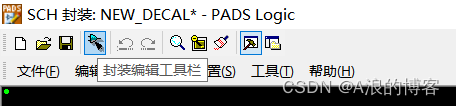

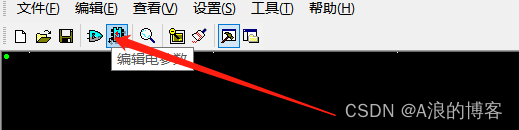

3.2接下来我们打开封装编辑工具栏正式开始做原理图了。

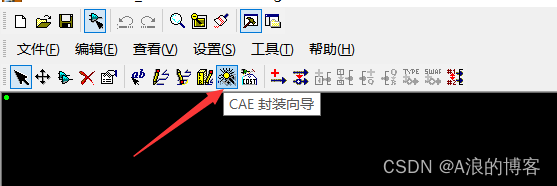

流程:封装编辑工具栏→CAE封装向导

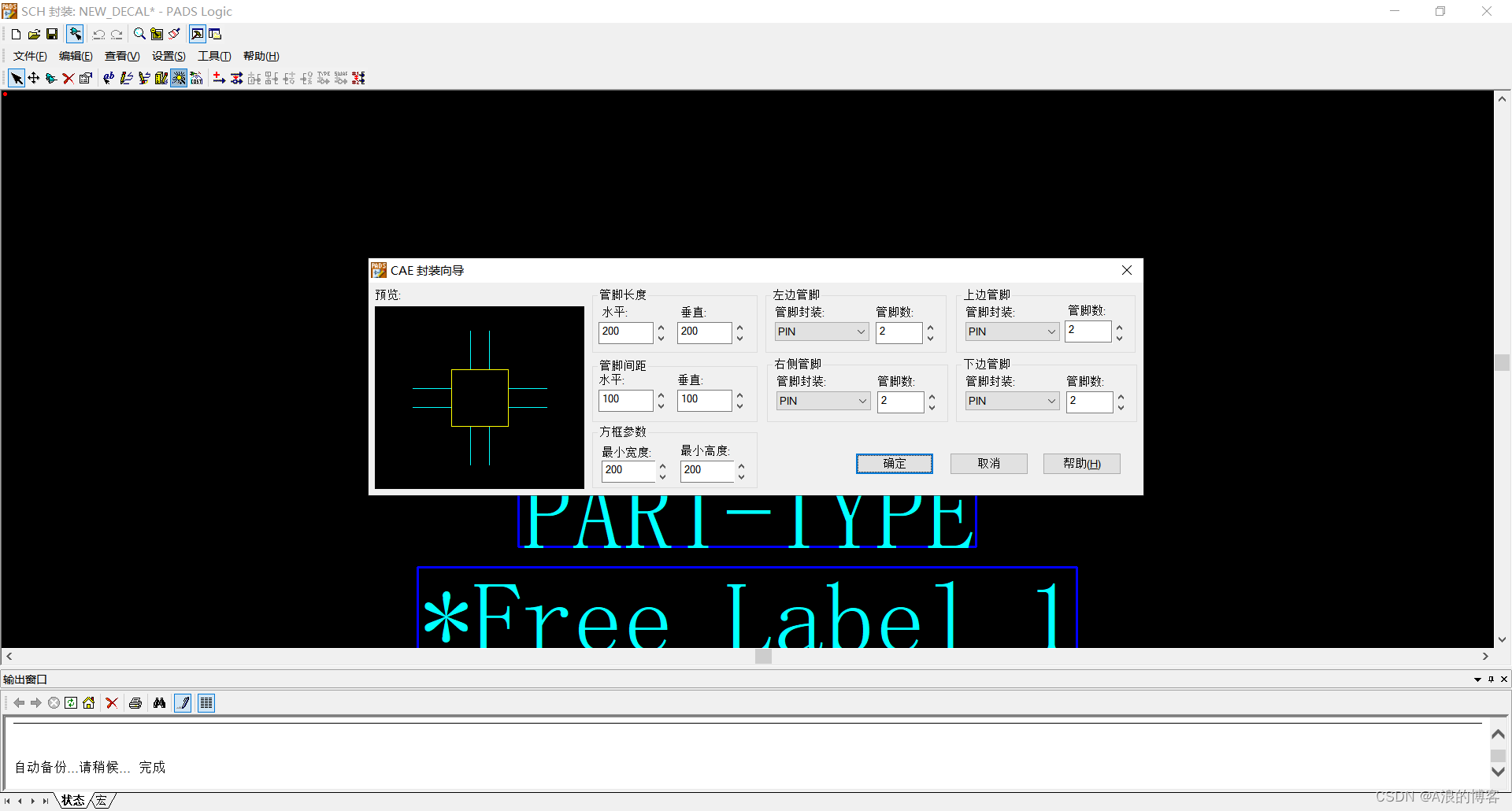

出现下面的界面:

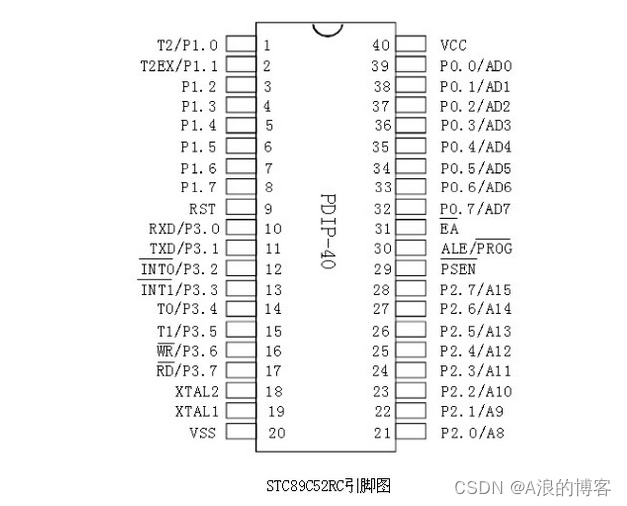

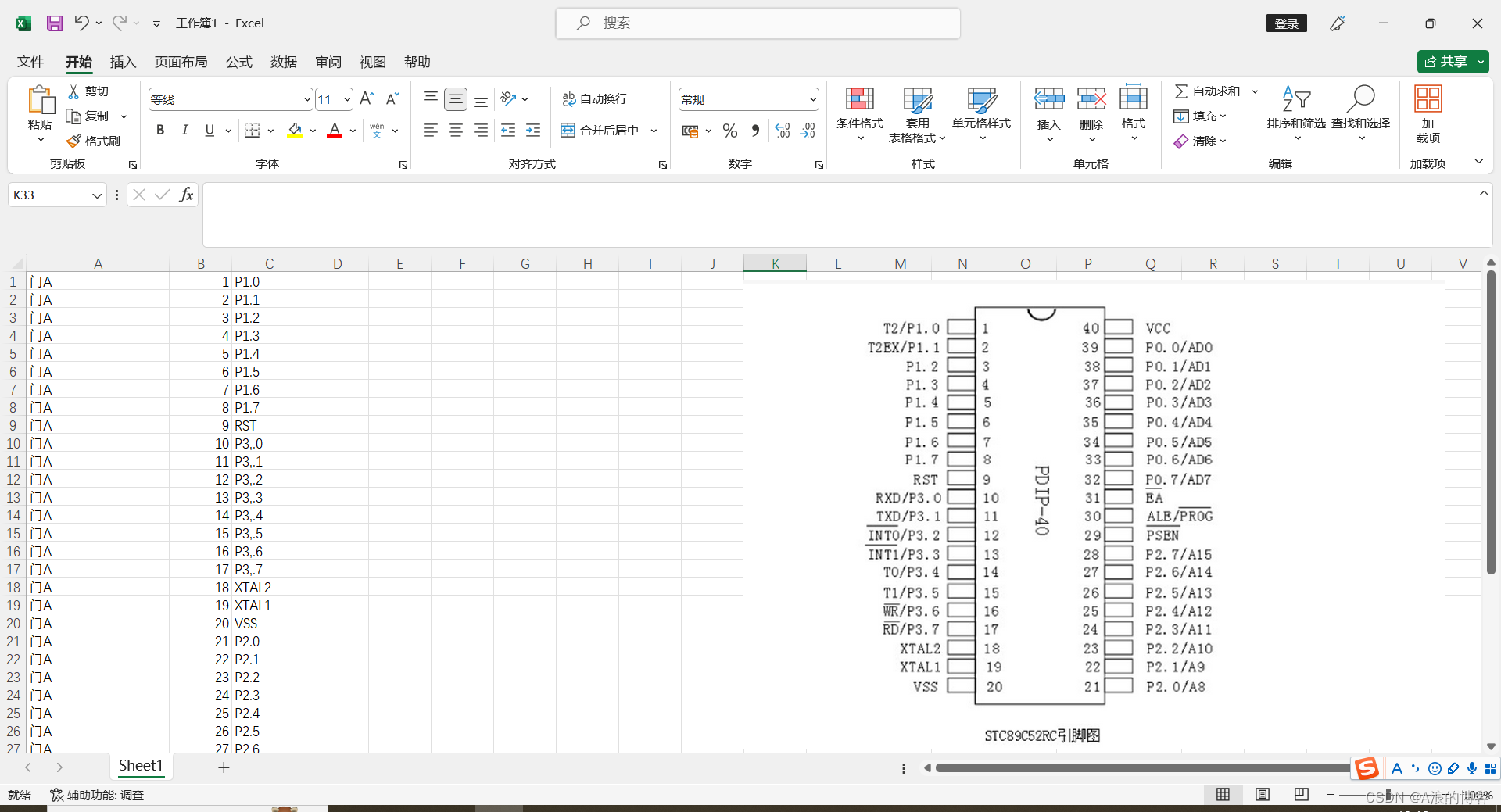

界面中的管脚长度我们一般不去动,默认就好了。管脚间距我们还不清楚,也行放着默认。管脚封装默认,最小宽度改成500!!!!还有上下左右的管脚数。下面附上一张STC89C52的管脚图,可知:左右管脚数分别为20,上下管脚数为0,我们设置一下然后点确定。

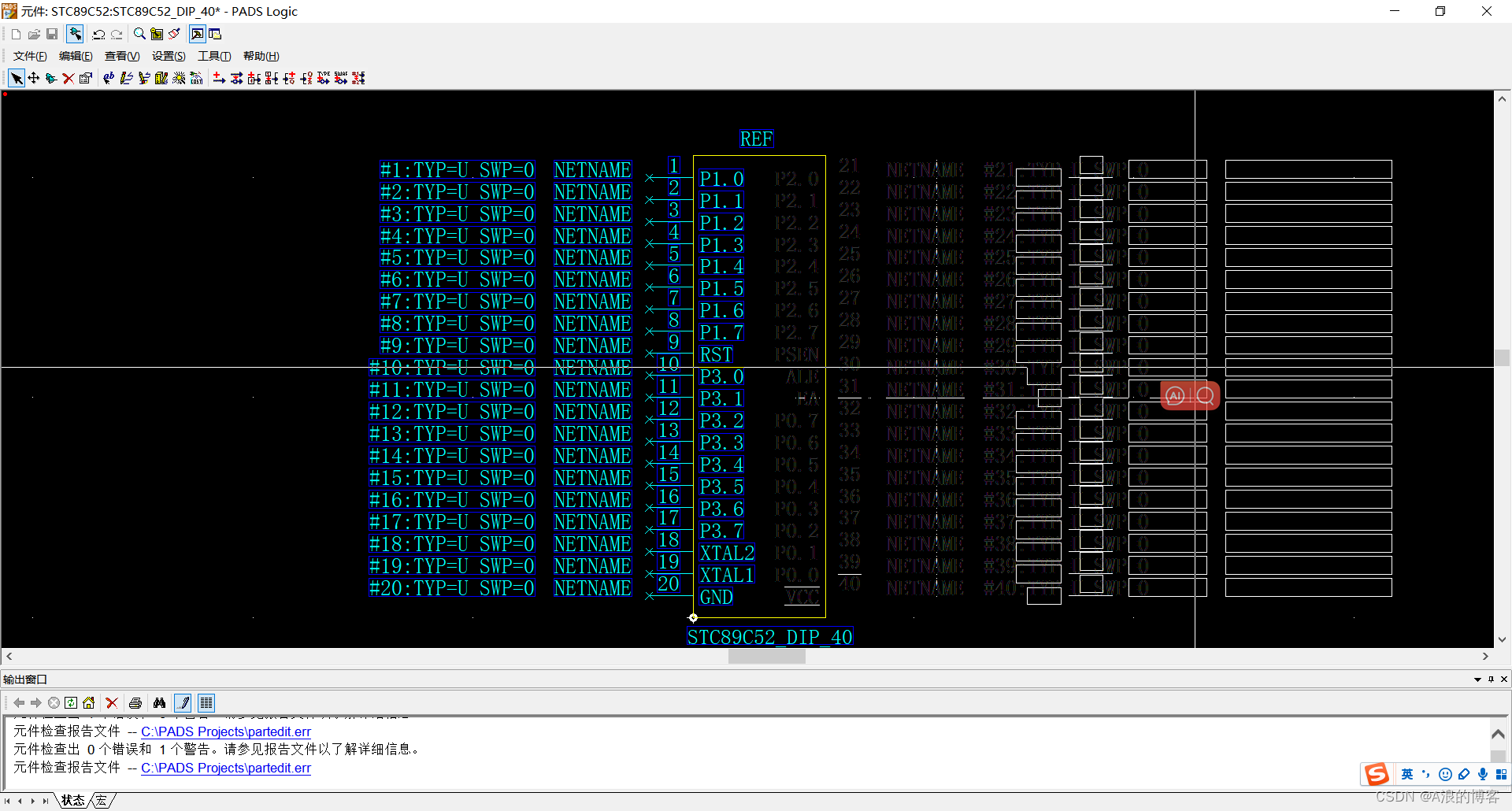

设置好之后长这样:

然后要记得点保存。

这里一定要把保存的库选成我们刚才创建的库,Pads默认是第一个库,这里要记得选一下。

这里的名称我取为STC89C52_DIP_40,是因为这种封装都有一个规范,对应我们上面这种封装就叫做DIP40封装。当然这名称不影响,只是顺便提一下,后面还会涉及到。

保存之后对比我们找到的引脚图显然有出入,因为我们引脚距离、芯片具体尺寸都没改,接下来我们就做这些操作。

3.3修改引脚顺序和引脚名称。

默认元件类型,点确定。

编辑电参数,流程依次是:常规→PCB封装→门→管脚→属性。

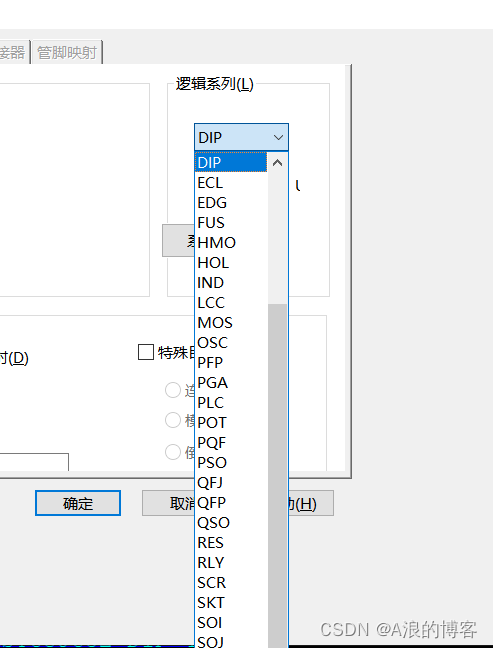

逻辑系列选择DIP(上面说过封装样式都有一个标准,我们STC89C52的封装样式就叫DIP)。

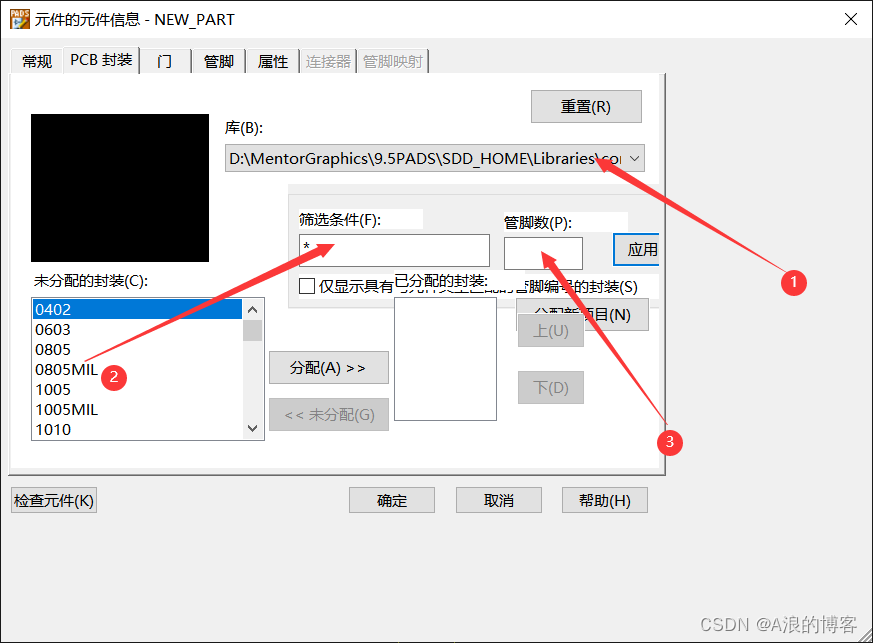

点击PCB封装,找到相应的封装。

这里我们随便选择一个系统自带的库,我选的是common库,筛选条件那里填*DIP*,这个意思是查找不管前面有什么,不管后面有什么,只要中间有DIP这个选项的封装(上面说过封装样式都有一个标准,我们STC89C52的封装样式就叫DIP)。管脚数我们选40,减小查找范围。

然后点击应用。

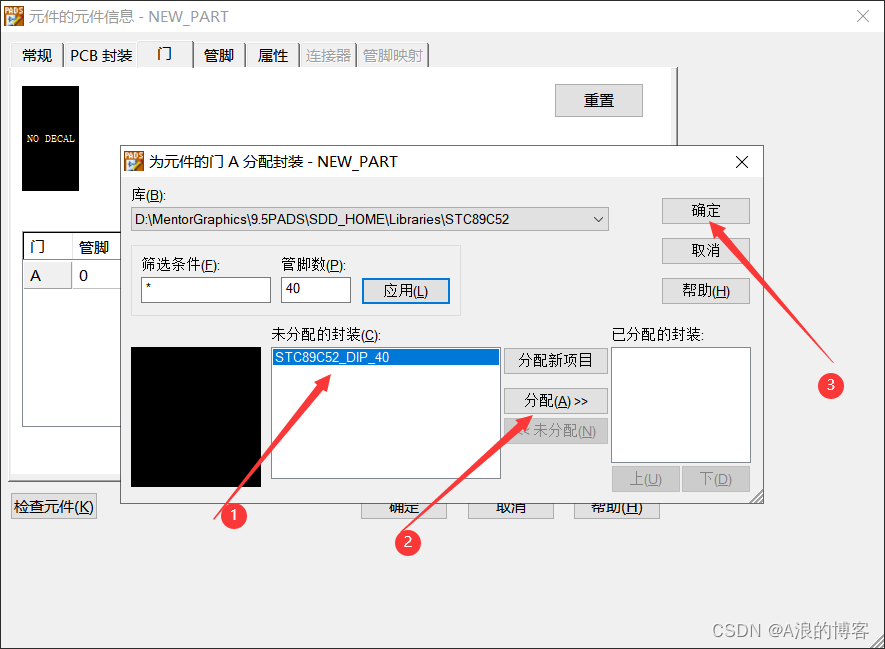

接下来选中跟我们STC89C52长得一样的封装→分配→确定。

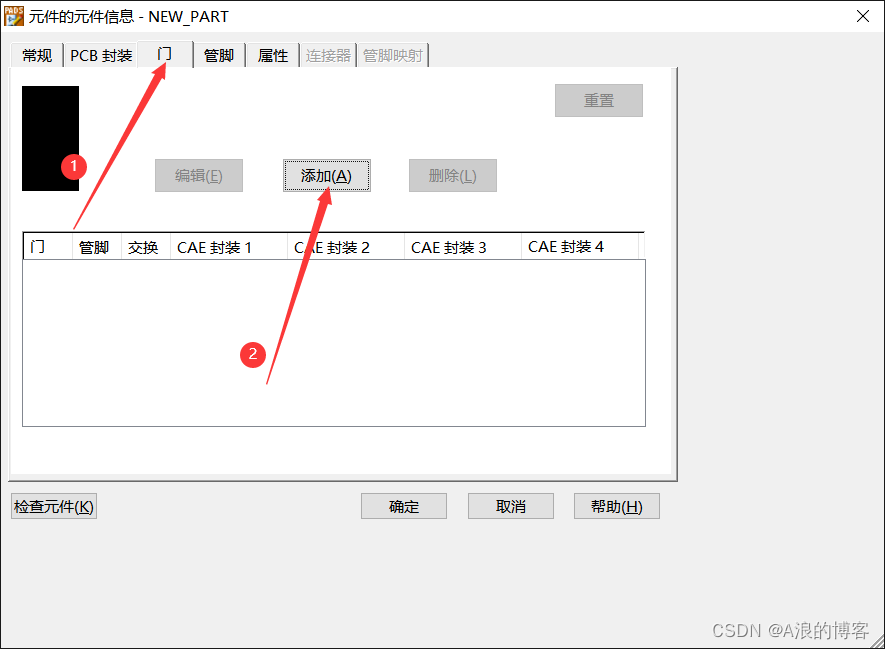

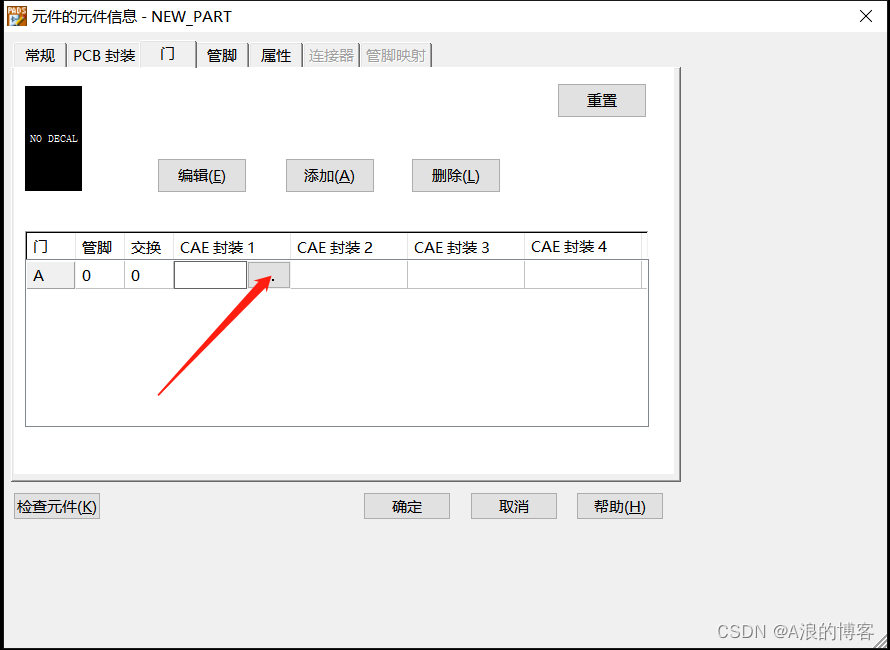

然后是把我们刚才画的CAE封装加进来。

双击CAE封装1,再点击后面的三个点。

照着下面的步骤点击:

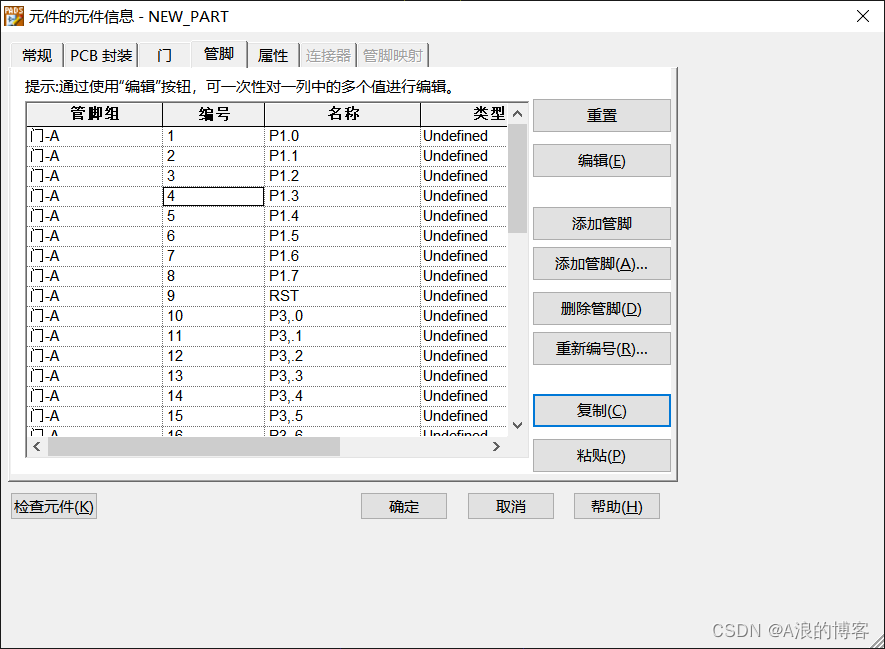

之后点到管脚。我们一共是40个管脚,如果一个一个去命名名称的话会很麻烦,接下来我们就要借助Excel表格来设置管脚。

左键管脚1不放,一直拖到最后

点击复制,打开Excel表格,进行粘贴。

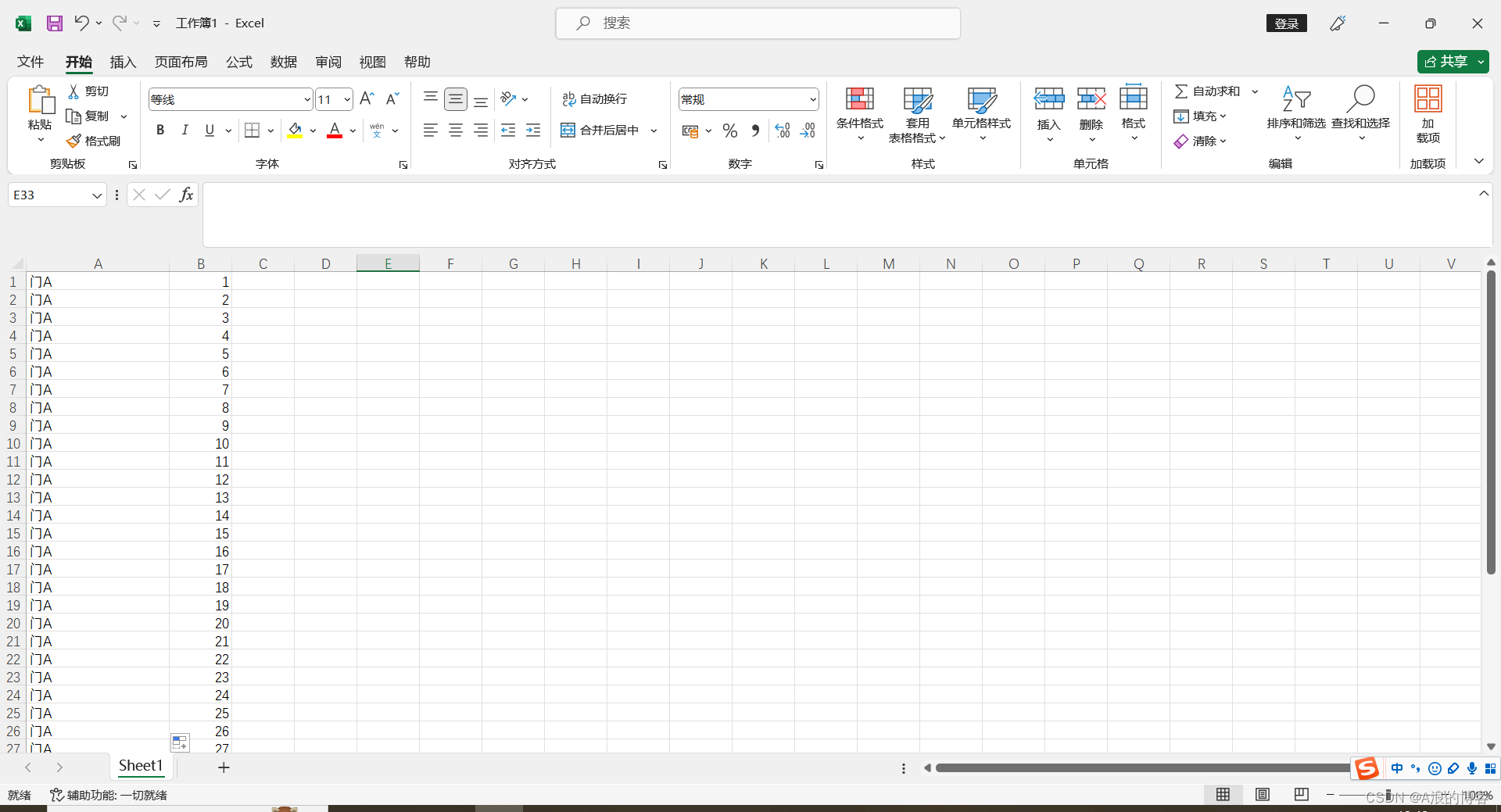

把第一项全改为门A,方法:设置第一个的名称叫做门A,然后下拉到最后一个。之后变成这样:

然后我们根据引脚图在C列开始设置引脚名称。设置好之后张这样:

复制回到Pads,鼠标选中未使用的管脚1,然后点击粘贴,结果会是这样:

点击检查元件看有没有错误。

属性可以先不管。然后点击确定。

我们就得到了下面这样一个界面:

这里发现一个问题,我们引脚没有GND,说明我在网上找的引脚图是错的,这里大家要根据自己商家给的手册里面的引脚图画,经过查证,GND是20脚,这里我回电器件参数→管脚那里将20脚的VSS改为GND。

然后点击保存,弹框直接点击确定就行。

这里看着有点挤,我们可以稍微改一下。

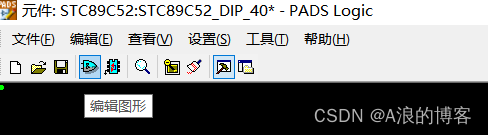

点击编辑图形,稍后弹出的弹窗我们点击确定。

点击封装编辑工具栏

选择修改2D线

鼠标点在器件的框上面,向后拖动,就可以给方框加宽了,下面是我加宽之后的界面:

如果只是修改2D线,效果不是这样的,因为引脚还在原来的地方,所以这里我们鼠标右键点击空白处,选择选择端点,然后框选住右边需要调整位置的所有端点,拖动他们向后放到合适的位置就行了。然后就会得到我上面这张图一样的效果。

如果还需要什么调整,大家可以试着自己调一下。

接下来我们可以发现右边的引脚的顺序跟引脚图是反的,我们要给它调换一下。

我们全部框选住右边的所有引脚,托出去一点,然后右键点击屏幕,选择X镜像,再点击屏幕,再选择Y镜像,然后最后再进行一次X镜像,我们就把引脚顺序调换过来了,然后装到原来的位置。

(此时开始右键):顺提一下:X镜像快捷键是ctrl+shift+f,Y镜像快捷键是ctrl+f。

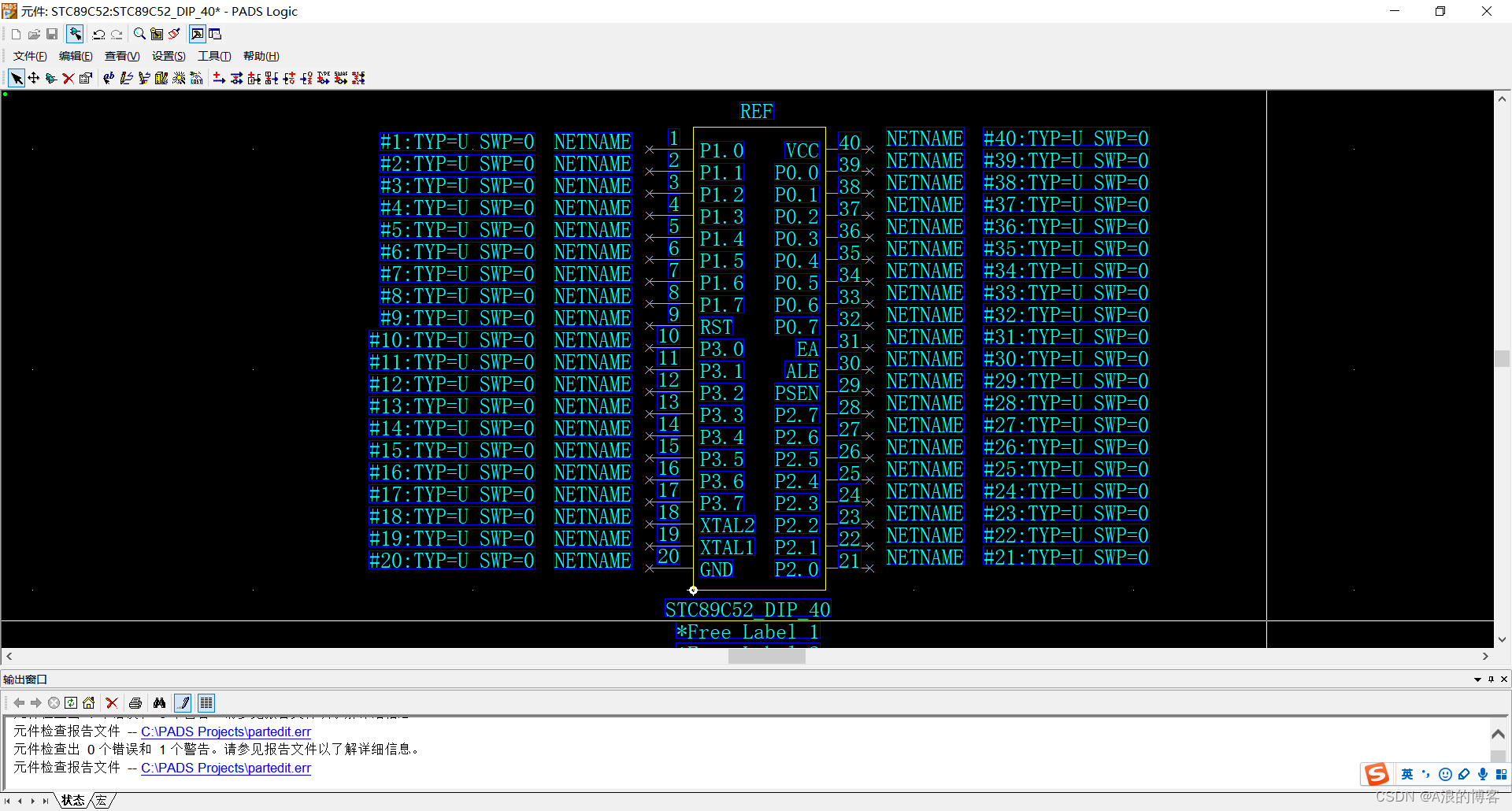

再进行稍调整,就是下面这张图:

至此我们原理图算是绘制完了。我们退出元件编辑器。

8865

8865

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?