1 简介

有时CPU需要与PL进行小批量的数据交换,可以通过BRAM模块,也就是Block RAM实现

此要求。本章通过Zynq的GP Master接口读写PL端的BRAM,实现与PL的交互。在本实验中

加入了自定义的FPGA程序,并利用AXI4总线进行配置,通知其何时读写BRAM。

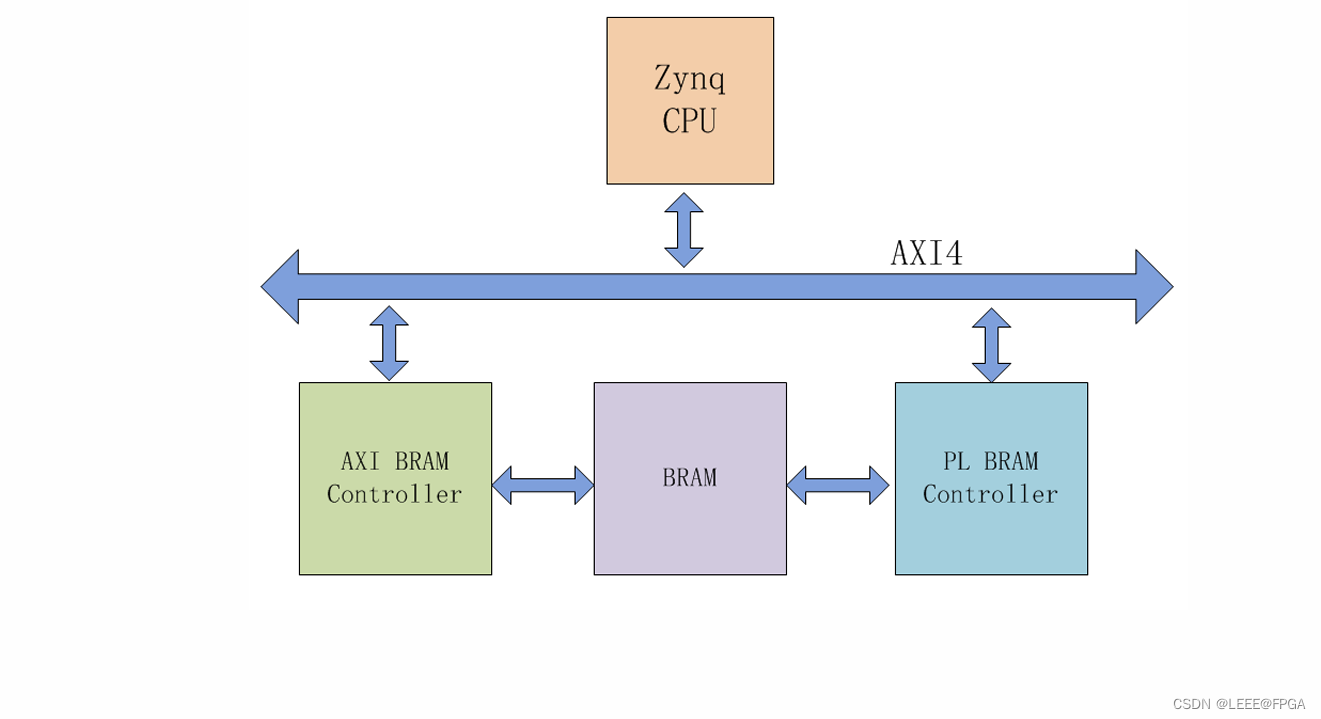

以下为本实验原理图,CPU通过AXI BRAM Controller读取BRAM数据,CPU仅配置自定义

的PL BRAM Controller 的寄存器,不通过它读写数据。

2 PL端

首先添加AXI BRAM Controller 模块,用于PS端控制BRAM,双击打开配置,连接AXI总线,

可用于读写BRAM模块,AXI模式设置为AXI4,数据宽度设置为32位,memory depth不在

这里设置,需要在Address Editor里设置。BRAM端口数量设置为1个,用于连接双口RAM

的PORTA。不使能ECC功能。

本文介绍了如何使用Zynq FPGA的Block RAM (BRAM)来实现处理器系统(PS)与可编程逻辑(PL)之间的数据交互。通过AXI BRAM Controller,CPU可以配置PL中的BRAM控制器,进行读写操作。实验中,PL端包含一个自定义的FPGA程序,使用AXI4总线进行通信,读取BRAM数据并在完成后通过中断信号通知PS端。

本文介绍了如何使用Zynq FPGA的Block RAM (BRAM)来实现处理器系统(PS)与可编程逻辑(PL)之间的数据交互。通过AXI BRAM Controller,CPU可以配置PL中的BRAM控制器,进行读写操作。实验中,PL端包含一个自定义的FPGA程序,使用AXI4总线进行通信,读取BRAM数据并在完成后通过中断信号通知PS端。

订阅专栏 解锁全文

订阅专栏 解锁全文

5996

5996

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?