在时钟设计中,特别是大型时钟网络结构中时钟切换电路是不可避免的,经常会在低速晶振时钟和高速PLL时钟之间切换,但是我们不能直接简单的用mux电路就切了,否则会导致时钟出现毛刺,这对时序电路来说是不可接受的,因此需要特别设计此电路。

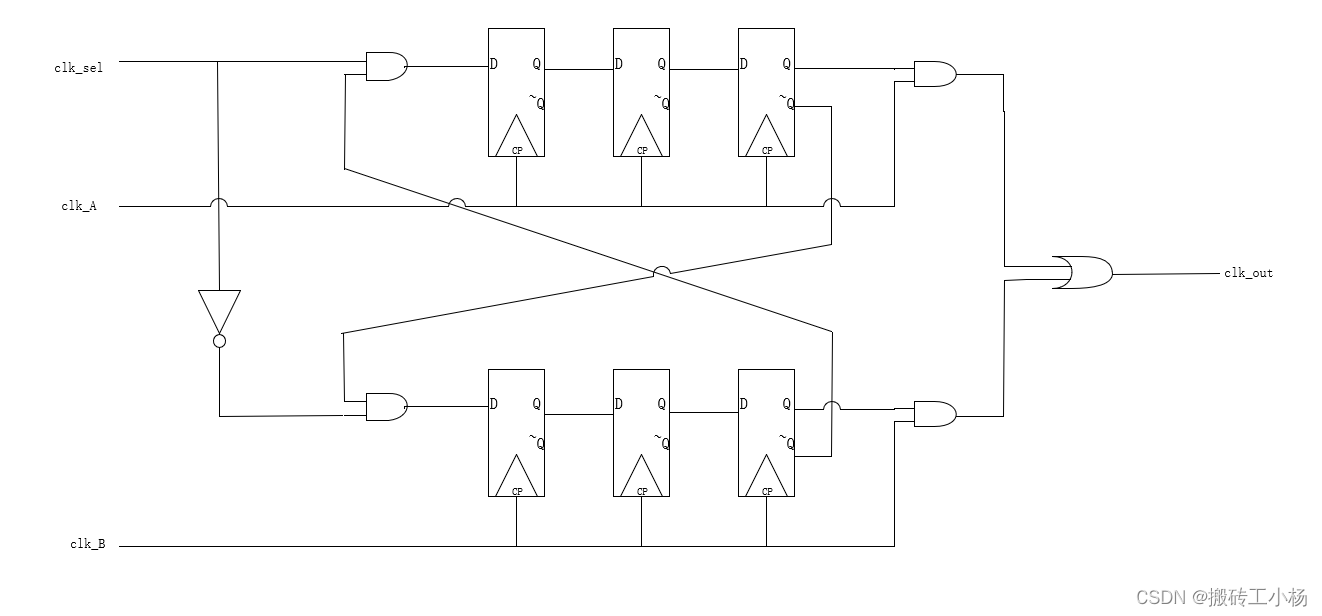

思路是在切换前时钟为低后再切换成新的时钟,这样可以避免毛刺的出现,只可能在最开始出现一点占空比不太对的情况,但是这种影响几乎可以忽略不计,clk选择信号需要先做同步处理,具体电路如下:

写RTLcode的时候尽量全部用standcell代替逻辑描述,这样的处理更严谨,封成一个模块后让后端设为don't touch,不要让综合工具为了优化而动这些寄存器的位置,甚至在中间加了逻辑。

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?