先写个hello.c

然后新建一个makefile文件或者Makefile文件(可以新建一个记事本,再改名字)

语法:

1、#号是注释

2、 目标文件:现在存在的文件

[TAB] 命令 #命令可以递归,也就是倒着来

这里不知道为什么正着来只执行一句 只能倒着来 一定要注意-S -E一定要大写

这里进行填坑,make会把第一个有效语句作为终极目标文件,比如下一个图的第一行是要生成hello.i,那么只会到生成hello.i停止,如果下面还有其他的比它更深的那么不会再执行,可以在第一行加上 ALL:a.out 那么这样不管下面回到a.out才停止

3、伪目标 上面生成以后要想把.i .s等删除 可以直接在makefile设置伪目标

.PHONY:

clear1000:

rm -rf hello.o hello.S hello.i hello

然后调用 make 伪目标名字 即make clear1000

2、联合

这里省去了中间的过程 由.c 到.o 再由.o到运行文件

第二层:

变量 = 即替换 +=即追加 := 即常量

使用变量 $(变量名)

比如原先是

a.o:a.c

gcc -c a.c -o a.o

如果加上替换

TAR=a.o

cc:gcc

那么调用的时候仅

$(TAR):a.c

$(cc) -c a.c -o $(TAR)

换句话说就是将一个字段赋值给某个变量,当使用的时候,可以用变量调用它

第三层 隐含规则

%.c %.o 即表示任意的.c或者.o

*.c *.c 即表示所有的.c 或者.o

out:a.o b.o c.o

gcc a.o b.o c.o -o out

那么a.o b.o c.o的生成都需要进行gcc

那么便可以直接

%.o:%.c

gcc -c %.c -o %.o

第四层

通配符 $@所有的目标文件 $^所有的依赖文件 $<所有的依赖文件的第一个文件

%.o:%.c

gcc -c %.c -o %.o

直接可以换成

%.o:%.c

gcc -c $^ -o $@

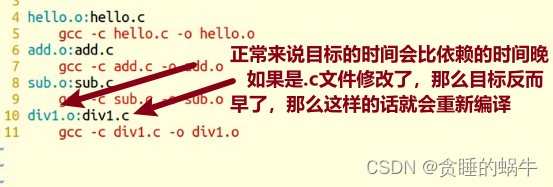

makefile的作用:如果在多个文件中的一个修改了,避免让没有修改文件也编译

如果仅修改某一个文件,重新使用make运行时,没有修改的文件并不会进行编译还是用的以前的,而修改的会重新进行编译,make是比较智能的,原因在于:

2704

2704

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?