经过几天的学习,终于把avalon总线接口IP模块的编写及嵌入搞定,现在总结如下:

首先需要说明的是总线接口,每一个avalon slave模块包含的信号有两类:一种是与avalon master模块进行通信的内部接口信号,另外一种是用于控制外设的外部接口,外设可以是片上的外设或者片外的外设。可以由用户决定。关于avalon总线的介绍,可以参考ALTERA公司的avalon bus spec.pdf文档,在文档中有关于avalon 总线的详细说明,没有必要细看,只需要作为手册查询即可,用到时再去翻看。

在定义好IP模块的接口后,剩余部分的编写与一般的控制逻辑就没有区别了,不必详述。

在此以自己编写的DDS模块为例介绍IP模块的设计过程。

DDS模块的组成包括控制寄存器,相位累加器,地址生成逻辑,和数据存储器;

控制寄存器包括当前的频率控制字,相位初始值,控制字寄存器;

相位累加器生成当前的相位;

地址生成逻辑根据相位累加器的结果形成对数据存储器的寻址地址;

数据存储器由megaWizard Plug-in Manager生成;其中包含所要产生的波形数据;

1, Rom生成过程

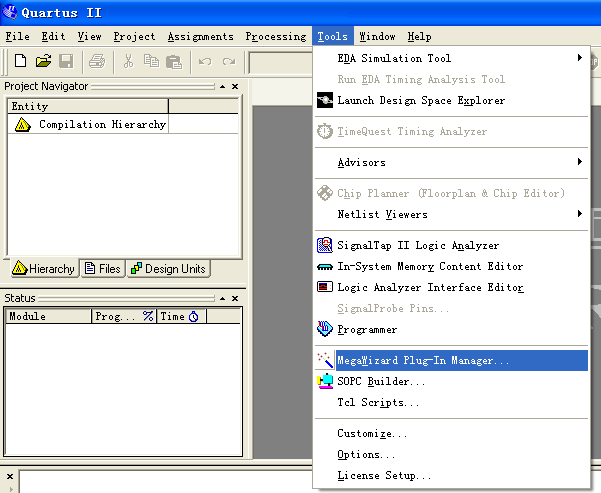

选择MegaWizard Plug-In Manager…,弹出下面的对话框。

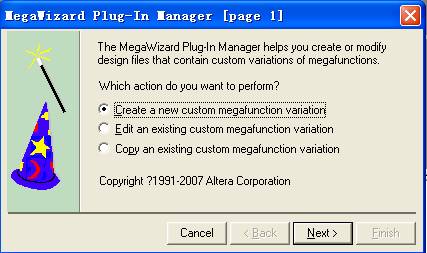

默认新建一个定制的megafunction

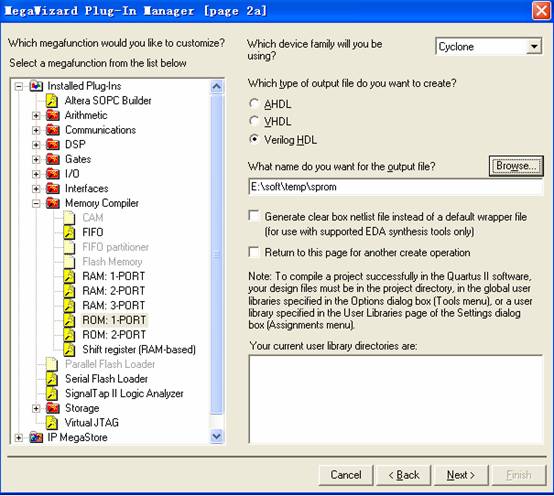

器件栏选择对应的器件系列,这里选择Cyclone,会列出改器件系列中可以使用的Megafunctions,此处选择 ROM:1-PORT,在名称栏中选择要存放的目录及文件名称,这里选择为sprom,单击下一步。

在How many 8-bit words of memory?栏中选择要建的ROM的大小,以字节计算。第四步默认即可选择下一步,到第五步。

在初始化数据栏中,需要注意此处可以先填入要使用的初始化文件,可以有两种格式,hex或者mif文件,这两种文件均可以通过Quartus II的新建文件中的other files生成。在需要仿真时需要将该初始化文件放到仿真根录下,在编译工程时,也需要将改初始化文件放到工程文件的根目录中,否则无法正常初始化。

我曾尝试修改sprom.v文件使其指向对应目录下的文件,不成功,因为在编译后,sprom.v被修改。

Altera_mf为仿真sprom需要的对应的库文件,在MOdelsim仿真时,需要对该文件进行编译,否则报错。该文件在Quartus安装目录中,可以查看help信息,得到具体位置。

选择要生成的文件,其中sprom.v为必须的。--inst为实例化模板

2, 将IP嵌入到系统中

新建系统后,选择 Create New Component选项

弹出对话框,显示要生成的文件的信息,结构组成

选择Add HDL File…,添加设计完成的verilog文件,上图显示为正在分析编译综合,综合完成后,若没有错误,会弹出如下对话框,但有时会出现此处分析正确,但在系统综合时出错的情况。

AVALON_dds.v分析完毕

所有文件分析完毕后,在Top Level Module中选择顶层模块,此处显示错误,可以不用理会,在后面的步骤中将会消除该错误。

将输出端口,映射到s1接口上,export为外部接口之意,另外和系统的接口需要选择对应的高电平或者低电平有效信号,若选择错误,可能导致系统不能正常工作。

修改后的界面

Slave地址对齐方式,一般情况下,选择寄存器模式,只有在外接存储器时,才部分选择Memory,两者的区别在于系统生成时,是否会将数据进行动态对齐。详见总线协议。

在此处单击move non_signal Interfaces去掉没有信号的接口,此后,将前面提到的错误将自动消失。

添加软件文件,用于软件对其进行访问。

根据自己的需要修改对应的信息,并单击Finish,弹出下面的对话框。

单击Yes,将生成对应的模块。

264

264

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?