近几年众核硬件逐渐被应用到数据仓库产品当中。目前主要的众核硬件包括以Intel SCC为代表的众核CPU、以Intel志强融核系列为代表的众核协处理器、以NVIDIA和AMD为代表的众核GPU。本文第一章介绍目前的主要的众核硬件及其特性,并从性价比和通用性方面对众核硬件进行比较;第二章介绍目前数据仓库中典型操作符在众核硬件上的优化技术。

1. 主要众核硬件

1.1. 多核CPU

多核的CPU虽然不是严格意义上的众核,但是在目前的很多研究中都将多核CPU视为和众核具相似的硬件而进行比较研究。多核CPU目前通常认为是8核及以下的通用CPU,每个核都有独立的L2和L1 Cache,多个核之间需要通过共享的内存或者L3 Cache才能交换数据。但核心数量并不是多核与众核的严格分界线,Intel目前核数最多CPU可以达到10个核。多核与众核的主要区别在于通用性和体系结构方面。1.2. 众核CPU

众核的CPU目前并不常见,在市场上没有销售。以Intel SCC为代表的众核CPU只提供给合作的高校和科研院所作为研究用途。在近几年的论文中常可以看见SCC的身影。Intel SCC中集成了48个对等的核,即每个核的功能和性能都是一样的,且每个核都有专属的L2 Cache。每两个核集成在一个tile中,共24个tile组成一个4*6的矩阵,之间通过CPU内部的告诉总线连接。每个tile中的两个核共享一部分(16KB)L1 Cache,这部分共享的L1 Cache成为MPB(Massage Passing Buffer)。所有tile中的MPB又可以被任意一个核访问,从而构成了一个384KB L1 Cache。

SCC中的每个核具有1GHz的主频和较强的逻辑计算能力,支持的指令集和普通的CPU类似。从而在增加核数的同时保证了通用性。此外,特殊的Cache设计使得可以针对具体的计算任务做出优化。

1.3. 众核协处理器

协处理器通过高速总线和CPU连接或者PCI-E借口连接到北桥上,是辅助CPU完成特定计算任务的计算器件。ARM架构的微处理器可以支持多大数十个协处理器,在嵌入式终端和智能设备中应用非常广泛。在通用计算平台上,Intel也推出了志强融核系列的协处理产品。至强融核协处理器其实是一款搭载众核处理器、显存(GDDR5)、PCI-E16X接口的外设,通过PCI-E插槽接入主板,通过北桥和CPU、主存连接。

目前的志强融合协处理器最多继承61个核,其中一个核是处理PCI-E数据传输的,其他60个核是对等的计算单元。支持的板载内存的类型为DDR5,具有300+GB/s的访存带宽,最大可以支持16GB的板载内存。较GPU而言,协处理器支持的板载访存带宽相近,但支持的最大内存大出1-2倍,同时协处理器的核数相对较少、但逻辑计算能力更强、通用性更好。

1.4. 众核GPU

众核GPU是目前最为常见的众核硬件。主要的GPU厂商NVIDA和AMD都提供了众核的GPU产品。其中NVIDA实现的CUDA技术应用已经非常广泛。在架构上GPU和协处理器有相似之处。但众核GPU中的核心计算能力较强、逻辑能力很差,因此GPU的专用性更强,通用性更差。此外,GPU中的核心通常被分为若干个组,每个组中有几十个核心,这些核心可以同时执行同一条指令、处理不同的数据,即SIMP。1.5. 众核硬件比较

在通用性方面1、多核CPU:通用,直接通过数据总线访问系统内存,带宽20-30GB/s;

2、众核 CPU:通用性稍差,架构类似GPU和协处理器,但可以直接访问系统主存,目前还没推广

3、众核协处理器:和GPU类似,单核的计算能力和逻辑运算能力更强,通用性更好一些。

4、众核GPU: 浮点计算能力强,逻辑运算能力差,显存几GB,带宽200GB/s,但需要通过PCI-E总线从主存取数据(PCI-E 16x :4GB/s),通用性差

能耗、性价比的比较

GPGPU的性价比最高、能耗最低,但软件开发成本高,在部分算法中性能并不突出 Many-core CPU总体好于multi-core CPU Multi-core CPU在某些复杂计算中表现突出。

总结下来,除了通用的多核CPU以外,many-core并不是共享所有的主存和cache的,无论CPU还是GPU都是NUMA(Non Uniform Memory Access Architecture,非统一内存访问架构)的架构。 算法要访问数据。要提高并行度,就要提高数据访问的局部性 GPU和协处理器访问系统内存的带宽会比访问本地内存地带宽低50倍以上。

2. 众核上数据仓库优化技术

2.1. 缓存的优化

众核处理器通常在缓存方面都有着和通用的多核CPU不同的设计,比如SCC就支持L1 Cache的跨核访问。在数据仓库算法中,表扫面算法由于数据局部性不好,数据如果经过多级缓存进入核中处理势必会影响效率,因此优化时可以针对表扫描算法,将数据直接加载到MPB中,进而进入核中做谓词过滤。2.2. 连接算法的优化

数据仓库中常用的连接算法包括sort-merge连接和hash连接。Sort-merge连接由于排序和归并的过程中,多个线程(核)并不需要共享数据,因此很适合在众核硬件上实现。但是sort-merge本身有很多的局限性,比如数据仓库中的连接通常在维表和事实表之间进行,而事实表是非常大的,sort-merge要求事实表实现在连接属性上排序,排序的代价是非常大的。

更为通用的hash连接由于在hash划分数据和连接时,多个线程(核)需要访问共享的哈希表和哈希桶,如果不做优化,在众核上是不可能有明显的性能提升的。因此出现了一些优化的技术。

常见的优化技术是基于Bucket的,即先将数据划分为不相关的Bucket再做链接。那么算法就分为分桶和连接两个部分。

在分桶阶段,为了利用多核达到性能的提升,也要保证多个核心不能有共享的数据,常用的算法有两种:

1、类似quickSort的分桶算法

Step1: 将array中hash值末位为0和为1的元素分开

Step2: 对分开的两个子array分别按照hash值末两位的值分开,依次递归,直到子array中元素个数小于某个阈值

2、两阶段分桶算法

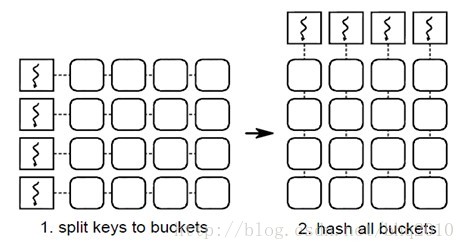

Hash桶的个数是固定的,第一阶段,各个core将数据表的一段hash到自己的桶里。 第二阶段,各个core将某一列上的桶合并。如图2.1所示。

图2.1. 两阶段分桶算法示意图

第一种算法的复杂度较高一些(n*log n),后一种算法虽然是线性的时间复杂度,但是要求分桶的个数预先固定,在数据倾斜的情况下就会导致分桶的不均衡。

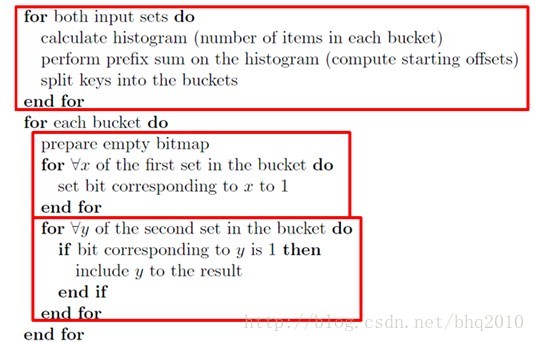

分桶之后的连接算法可以采用基于位图的连接算法。如图2.2所示,第一阶段是分桶,第二阶段是在左表的一个分桶上计算出一个位图,其实就是一个布隆过滤器,第三阶段基于左表的位图来过滤右表的分桶,避免了不必要的连接操作,也就避免的大量的内存访问。

图2.2. 基于分桶的连接算法

此外,连接算法的优化方面,由于数据仓库中维表很小,可以在维表上做完谓词过滤、得到一个布尔向量,将布尔向量读入到各个核的缓冲区中,和事实表做连接。

还有一种称为Invisible Join 的连接优化技术,是一种查询重写技术。由于维表比较小,当维表和事实表连接时,将连接条件转换成事实表上的谓词。 如:事实表的一个外键连接到维表的一个主键上。如果维表的主键上的值在一个连续范围内,可以将其重写成事实表外键上的一个between谓词,从而避免了反复对维表的随机访问。

2万+

2万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?