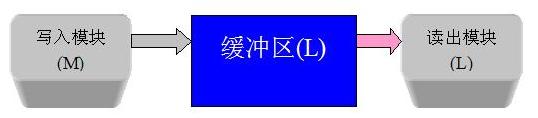

在程序的两个模块间进行通讯的时候,缓冲区成为一个经常使用的机制。

如上图,写入模块将信息写入缓冲区中,读出模块将信息读出缓冲区。这样使得:

- 将程序清晰地划分模块,建立良好的模块化架构,使得写入和读出成为高聚合,低耦合的模块。

- 对于写入和读出的处理可能产生的快慢不均匀的情况进行平衡,使得整个处理的速度趋于平滑的均匀状态,避免出现读出模块处理的慢速使得写入模块等待使得响应速度下降的状况;同样,也避免写入模块的快慢不均匀,使得读出模块忙闲不一的情况。

- 可以增加处理的并发性。由于写入和读出模块的良好设计和划分,可以使得它们彼此隔离和独立,从而,使用线程和进程产生不同的并发处理,并通过缓冲区大小的调节,使得这个处理达到良好的匹配和运行状态。例如,写入模块可以有N个线程或进程,读出模块可以有M个线程和进程,缓存冲区可以配置L的大小。N、M、L可以通过模拟试验设定适应具体应用的值。也可以建立一套自动调节的机制,当然,这样会造成设计的复杂性。

缓冲区显然不适合下面的情况:

- 数据的接收处理原本就是密切相关,难以划分模块。

- 处理中的模块间明显不存在处理不均匀的情况,或者不是主要问题。

- 需要同步响应的情况。显然,写入端只是将信息push到队列中,并不能得到读出端的处理响应信息,只能适合于异步的信息传递的情况。

缓冲区的设计:

- 缓冲区是一个先进先出队列。写入模块将信息插入队列;读出模块将信息弹出队列。

- 写入模块与读出模块需要进行信息的协调和同步。

- 对于多线程和多进程的写入或读出模块,写入模块间以及读出模块间需要进行临界区处理。

本文介绍了环形队列作为程序模块间通讯的缓冲区,讨论了其在处理速度不平衡、并发性和异步信息传递中的作用。详细阐述了环形队列的数据结构,包括其先进先出特性,以及在多线程环境中的同步和临界区处理。通过提供C++实现的环形队列类,展示了如何设计适用于共享内存的环形队列,为后续的进程间通讯和等待策略设计奠定了基础。

本文介绍了环形队列作为程序模块间通讯的缓冲区,讨论了其在处理速度不平衡、并发性和异步信息传递中的作用。详细阐述了环形队列的数据结构,包括其先进先出特性,以及在多线程环境中的同步和临界区处理。通过提供C++实现的环形队列类,展示了如何设计适用于共享内存的环形队列,为后续的进程间通讯和等待策略设计奠定了基础。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

975

975

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?