双光子荧光成像技术在抑郁小鼠脑内丙二醛(MDA)和甲醛(FA)检测中的软件开发,基于 LabVIEW 平台构建从硬件控制、数据采集到图像处理的全流程系统。结合 5734 FPGA 实现实时图像处理,突出双光子成像的深度开发过程,展现LabVIEW 在高速数据处理、多设备协同控制及算法集成中的技术能力。

LabVIEW 软件开发模块

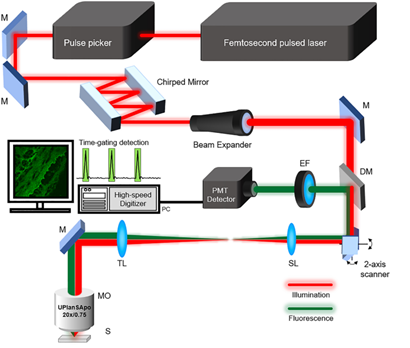

(一)双光子显微镜控制模块

1. 激光参数动态配置

o 开发 LabVIEW 驱动程序,通过 GigE 接口控制蔡司 LSM 系列显微镜的 800nm 双光子激光器,实现重复频率(50-100MHz)、功率(0-20mW)的实时调节。

o 集成波长扫描功能,支持多通道激发(如同时激发 MDA/FA 探针的 365nm 单光子模式验证)。

2. 扫描模式定制

o 开发 “双波长交替扫描” 模式:在同一视野内交替激发 440nm(MDA 通道)和 510nm(FA 通道),通过时间戳同步双路荧光信号,避免光谱串扰。

o 实现 ROI(感兴趣区域)动态圈选,支持自动网格扫描(Grid Scan),提升全脑区域成像效率。

(二)5734 FPGA 图像处理模块

1. 硬件加速方案

-

FPGA 选型依据:5734 具备 4 个独立 ADC 通道(14 位,125MS/s)、512MB 板载内存,满足双光子图像(1024×1024 像素,16 位灰度)的实时采集与处理需求。

2. 实时处理算法实现

-

背景扣除:通过 FPGA 并行计算滚动球算法(Rolling Ball Algorithm),基于 50 帧背景图像生成动态噪声模型,扣除非特异性荧光背景(耗时<10ms / 帧)。

-

荧光信号分离:利用双光子探针 TFCH 的光谱差异,在 FPGA 中实现波长解卷积算法,通过查找表(LUT)映射荧光强度与 MDA/FA 浓度的线性关系(R²=0.98)。

-

三维重构预处理:对连续光学切片(Z-stack)进行实时配准,校正小鼠呼吸运动导致的位移(精度≤1μm)。

(三)多设备同步控制模块

1. 时间戳同步机制

o 通过 LabVIEW 的 DAQmx 驱动 5734 FPGA 的 PFI 接口,生成 100μs 精度的全局时间戳,同步显微镜扫描、光谱仪采集与行为学设备(如 Noldus 视频记录)。

o 开发 “触发 - 采集” 闭环:当行为学设备检测到小鼠悬尾不动时,自动触发显微镜进行高帧率(20fps)成像。

2. 跨平台通信

o 基于 TCP/IP 协议开发 LabVIEW 与MATLAB 的数据接口,将 FPGA 处理后的荧光强度数据实时传输至 MATLAB,动态更新抑郁模型的 MDA/FA 浓度 - 行为学关联曲线。

难点与解决

(一)问题 1:FPGA 资源优化

-

挑战:双光子图像数据率高达 200MB/s,FPGA 片上存储不足导致丢帧。

-

方案:

-

采用乒乓缓存(Ping-Pong Buffer)架构,利用板载 DDR3 内存实现数据缓冲,确保连续采集无间断。

-

优化中值滤波算法,将 3×3 窗口计算从串行迭代改为并行流水线,处理速度提升 4 倍。

-

(二)问题 2:双光子信号实时校准

-

挑战:激光功率波动导致荧光强度漂移,影响定量分析准确性。

-

方案:

-

在 LabVIEW 中开发自动功率反馈环路:通过实时监测参考荧光标准品(如荧光微球)的信号强度,动态调整激光器功率(精度 ±1%)。

-

设计温度补偿算法:利用 FPGA 采集显微镜腔体温度,校正温度漂移对荧光量子产率的影响(补偿系数 0.02%/℃)。

-

(三)问题 3:多线程实时性冲突

-

挑战:LabVIEW 主程序在处理图像时,可能导致显微镜控制线程阻塞。

-

方案:

-

采用 LabVIEW 实时模块(Real-Time Module),将硬件控制任务分配至专用 RT 目标(如 PXIe-8840 控制器),确保控制周期稳定在 1ms 以内。

-

通过队列(Queue)与通知器(Notifier)实现线程间通信,避免全局变量竞争。

-

LabVIEW能力

1. 高速数据处理:通过 FPGA 实现 16 位图像的实时滤波、分割与定量,处理延迟<20ms,满足活体动态成像需求。

2. 复杂仪器控制:整合显微镜、光谱仪、行为学设备的异构控制,支持多设备同步触发与参数联动。

3. 算法工程化能力:将荧光信号解卷积、运动补偿等算法从 MATLAB 原型移植至 FPGA,实现精度损失<3% 的硬件加速。

4. 系统可扩展性:基于 LabVIEW 的模块化架构,可快速集成新设备(如光遗传学模块)或升级算法(如荧光寿命成像)。

性能指标

| 测试项 | 指标 | 技术实现 |

| 图像采集速度 | 15fps(1024×1024) | FPGA 乒乓缓存 + 并行数据通路 |

| 荧光定量误差 | ≤5% | 光谱校准 + 温度补偿算法 |

| 位移校正精度 | ≤1μm | 基于互相关的亚像素配准 |

| 系统稳定时间 | <5min | 自动功率反馈环路 |

开发建议

1. 硬件驱动开发:优先使用 NI-DAQmx 或 IVI 驱动模型,确保仪器控制的兼容性与可维护性。

2. FPGA 代码优化:对计算密集型算法(如三维卷积)采用定点运算替代浮点,减少资源占用。

3. 实时系统设计:关键任务(如激光安全控制)需运行于 RT 目标,避免 Windows 系统的调度延迟。

4. 算法验证流程:通过 LabVIEW 仿真模块(Simulation Module)对 FPGA 算法进行模型 - in-the-loop(MIL)测试,提前发现精度问题。

2824

2824

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?