What is the purpose of a testbench ?

testbench允许我们通过仿真来验证设计的功能,它包括了设计以及驱动设计的激励.

(1)产生不同类型的输入激励;

(2)利用产生的激励驱动设计;

(3)设计处理输入产生输出;

(4)对比设计的输出与期望的输出;

(5)如果发现功能bug则修改设计以修复bug;

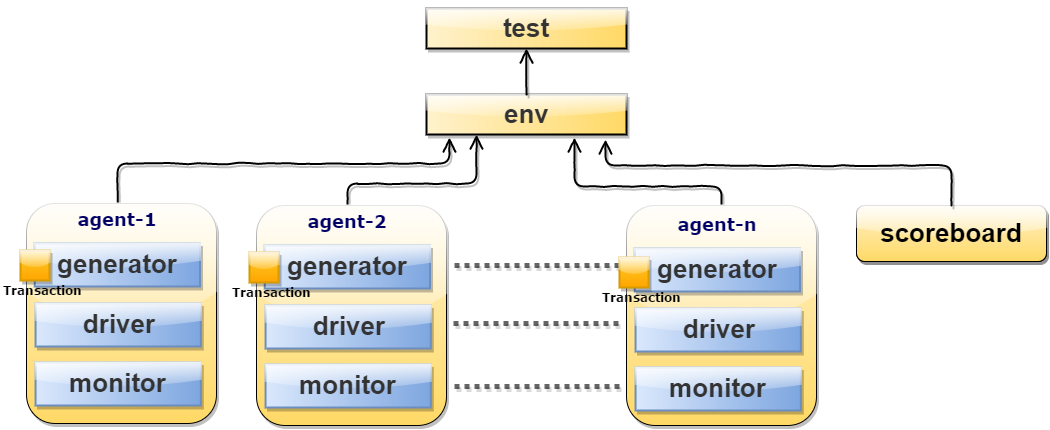

Components of a testbench

一个简单的testbench由以上几部分组成,下面详细介绍.

What is DUT ?

DUT(design under test)是由verilog或VHDL描述的硬件设计.

// All verification components are placed in this top testbench module

module tb_top;

// Declare variables that need to be connected to the design instance

// These variables are assigned some values that in turn gets transferred to

// the design as inputs because they are connected with the ports in the design

reg clk;

wire en;

wire wr;

wire data;

// Instantiate the design module and connect the variables declared above

// with the ports in the design

design myDsn ( .clk (clk),

.en (en),

.wr (wr),

. ...

.rdata);

// Develop rest of the testbench and write stimulus that can be driven to the design

endmoduleWhat is an interface ?

接口就是由许多数据端口组成的一捆线.

What is a driver ?

当一个drver需要驱动一些信号值进入到DUT中时,它会调用接口中的task,而不用具体知道这些信号之间的时序关系,信号之间的时序关系由接口提供.

How does the driver know what to drive ?

generator将产生的有效数据发送到driver,两者之间通过接口通信.

Why is a monitor required?

monitor的作用是收集DUT产生的数据,并将它们发送给scoreboard.

What is the purpose of a scoreboard?

scoreboard有一个DUT的参考模型,参考模型会得出激励所对应的期望结果.输入在送入DUT的同时也会送入scoreboard,所以如果DUT存在错误,其产生的结果就不会与期望的结果匹配.通过比较DUT的输出和参考模型的输出,我们就可以检测到DUT中的错误.

Why is an environment required ?

encironment可以使验证更加灵活,这意味着在将来可以加入更多的component.

What does the test do ?

test可以例化environment对象,并以我们的方式配置它.我们或许会有很多的test,但是直接改变environment是不方便的,因此我们需要参数化的environment.

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?