这里写目录标题

P0

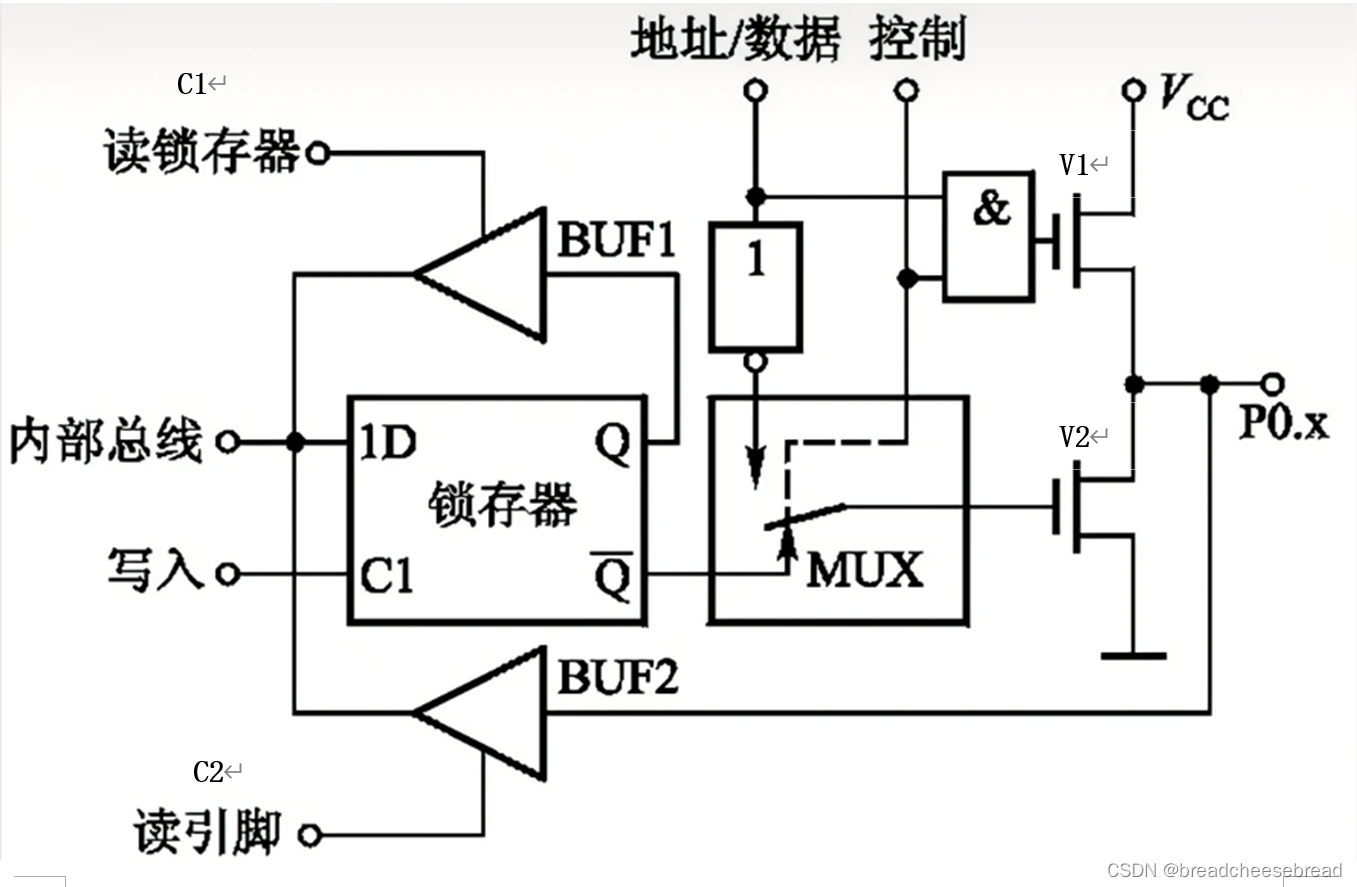

- 多路开关MUX决定P0.x是作数据/地址引脚还是作通用I/O引脚。

- 三态缓冲器BUF1,BUF2由C1,C2控制是读锁存器还是读引脚

作数据/地址引脚

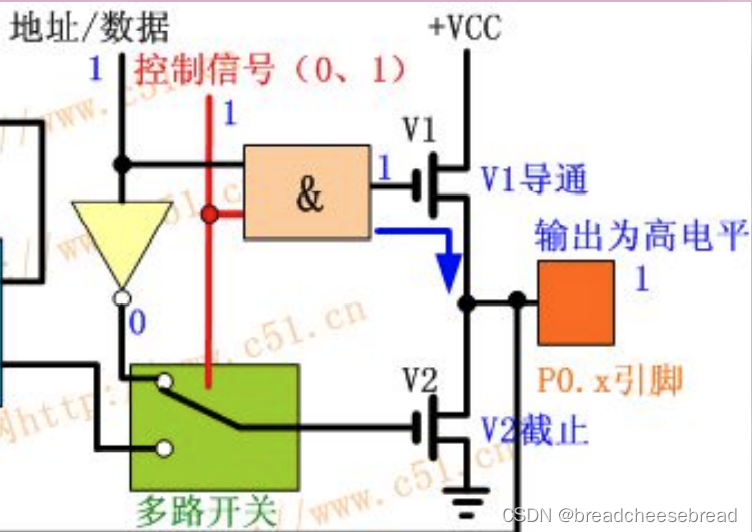

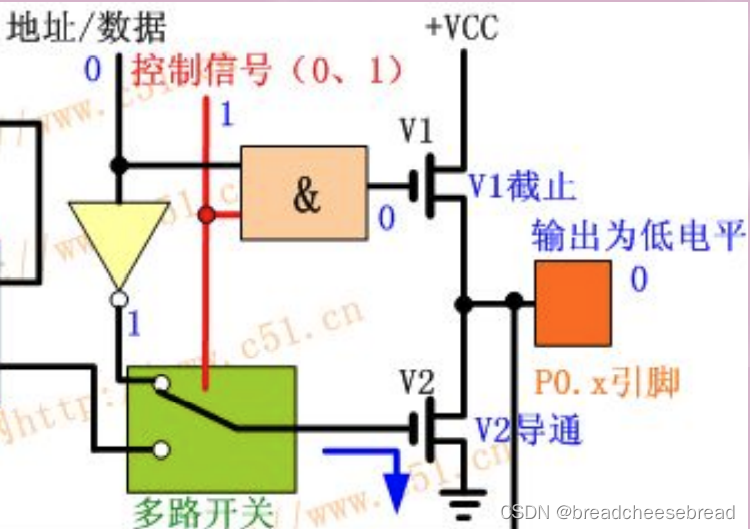

控制线置1,MUX连通地址/数据线,此时作P0.x数据/地址引脚

发出信号

- 数据/地址线置1,V1导通,V2截止。P0.x输出1的数据/地址信号;

- 数据/地址线置0,V1截止,V2导通。P0.x输出0的数据/地址信号;

接受信号

- 数据输入:在取数据期间,“控制”信号为“0”,V1管截止,多路开关也跟着转向锁存器反相输出端Q非;CPU自动将0FFH(11111111,即向D锁存器写入一个高电平‘1’)写入P0口锁存器,使V2管截止(高组态时才能读数据),在读引脚信号控制下,通过读引脚三态门电路将指令码读到内部总线。

注意:当P0作为地址/数据总线使用时,在接收数据前,CPU自动向P0口锁存器写入0FFH,破坏了P0口原来的状态。因此,不能再作为通用的I/O端口。

作通用I/O引脚

控制线置0,MUX连通D锁存器,此时作P0.x通用I/O引脚(此时V1永久截止)

- 输出1:内部总线输出1,C1端给入时钟信号,使得 Q

本文详细解析51单片机的P0、P1、P2、P3口的工作原理。P0口在作数据/地址引脚时,需在接收数据前写入0FFH;作通用I/O引脚时,需附加外部上拉电阻。P1口为准双向口,作输入时需先写入1。P2口通常作为高8位地址总线,也可作通用I/O口。P3口具有第二功能,能自动切换功能模式。

本文详细解析51单片机的P0、P1、P2、P3口的工作原理。P0口在作数据/地址引脚时,需在接收数据前写入0FFH;作通用I/O引脚时,需附加外部上拉电阻。P1口为准双向口,作输入时需先写入1。P2口通常作为高8位地址总线,也可作通用I/O口。P3口具有第二功能,能自动切换功能模式。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

1247

1247

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?