1、简介

1.1、eSPI的优势

eSPI(Enhanced Serial Peripheral Interface)即加强型SPI总线,物理层跟SPI高度相似,协议层是Intel独有的通信协议,自2016年推出后,逐渐成为主流,并取代LPC成为PC中CPU与EC、BMC、SIO的新一代通信协议。

特点:

1、低功耗

2、低pin脚

3、中带宽

4、旁带pin脚作为带内信息

5、实时Flash共享

6、取代PCH和EC的SMBUS通信

7、可升级带宽

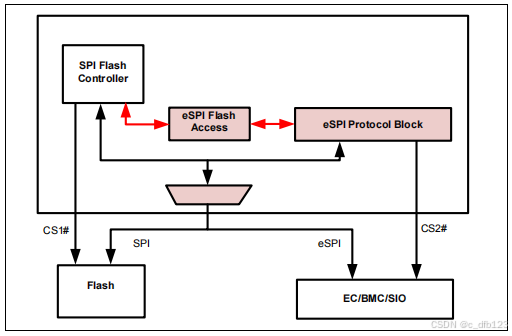

1.2、总线示意图

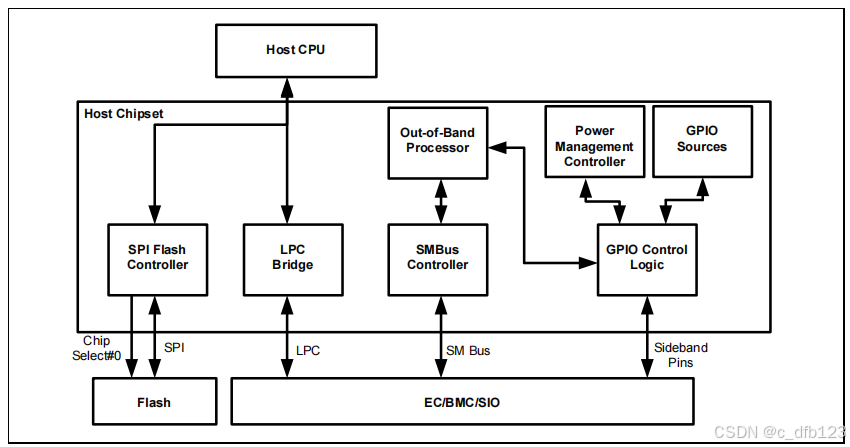

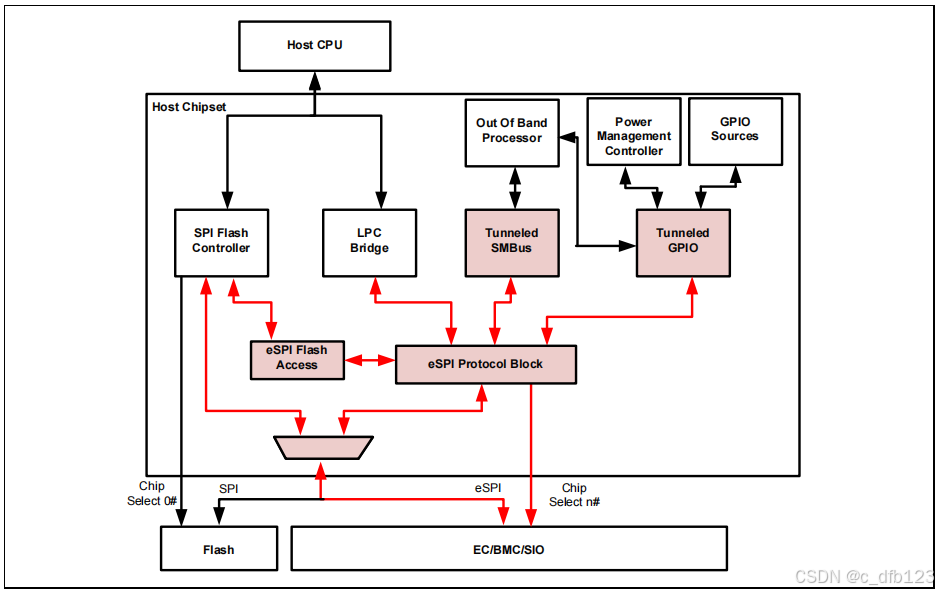

1、LPC总线的架构

2、eSPI总线架构

2、eSPI架构描述

2.1、引脚描述

| 序号 | 引脚名称 | 描述 | 备注 |

| 1 | CS# | 片选信号 | 主机用以选中从机的信号线 |

| 2 | CLK | 时钟信号 | 用以同步数据的信号线 |

| 3 | Alert# | 断言信号 | 从机用以主动产生请求的信号线 |

| 4 | IO0 | 输入输出信号0 | 数据传输信号线,Single模式下,作为主机控制的数据线 |

| 5 | IO1 | 输入输出信号1 | 数据传输信号线,Single模式下,作为从机控制的数据线,也可以作为Alert信号线 |

| 6 | IO2 | 输入输出信号2 | 仅在Quad模式下使用,作为数据线 |

| 7 | IO3 | 输入输出信号3 | 仅在Quad模式下使用,作为数据线 |

| 8 | Reset# | 复位信号 | 用以复位主机或者从机 |

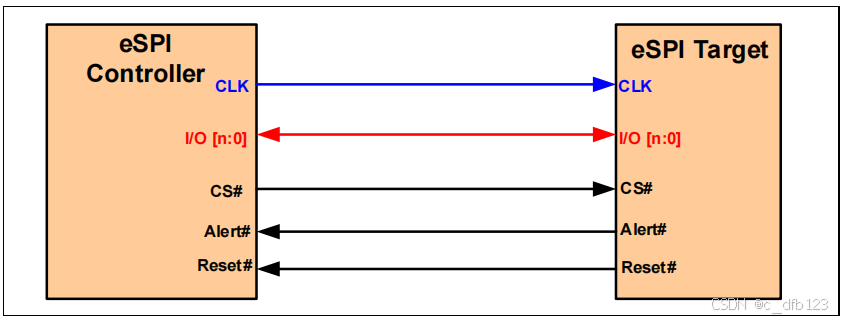

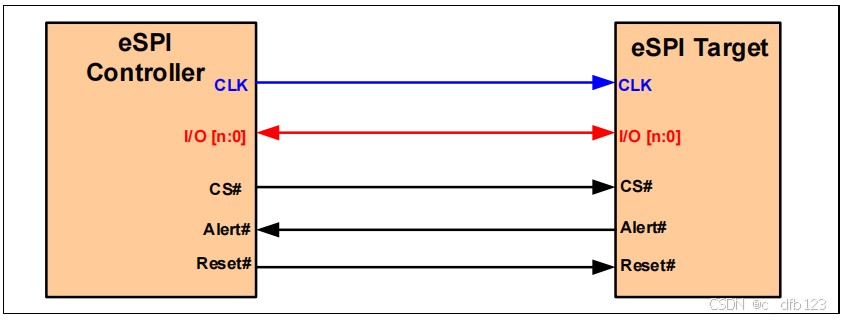

从表1来看,正常eSPI通信中,至少有5个信号是必须存在的,即CS#, CLK, IO0, IO1, Reset#,相较于LPC的7个必选信号线 + 6个可选信号线,即13个信号线而言,eSPI是5个必选信号线 + 3个可选信号线,即8个信号线。pin脚节约很多,符合eSPI优势中第二点描述。

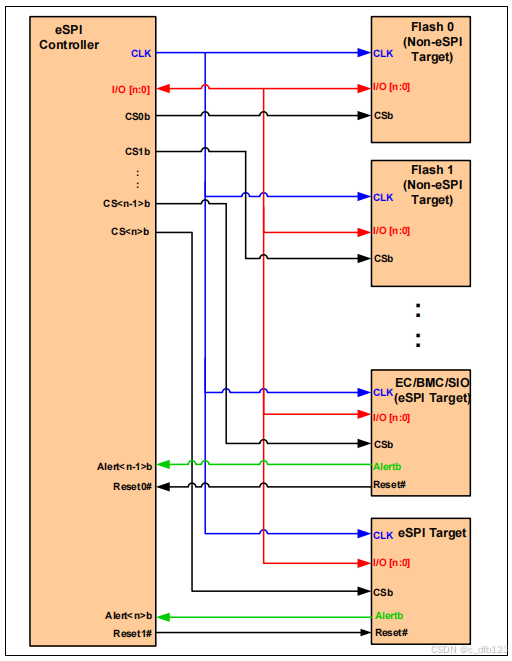

2.2、eSPI系统拓扑图

eSPI是由SPI总线延伸而来,其总线连接非常相似,由一主多从,一主一从,不论是哪种连接方式,均是通过片选信号来选择从机进行通信。不同于SPI的是,eSPI中多了一个复位信号线,该复位信号线是用来复位主机或者从机,因此,复位信号线的传输方向就分为如下两种。

下图是eSPI主机外挂了四个从机,但是其中两个是SPI从机,两个是eSPI从机;SPI从机没有复位信号线,eSPI从机有复位信号线。复位信号线可以由主机到从机,也可以由从机到主机。具体需要结合实际的应用需求,从机在设计时需要对Reset信号线的传输方向进行可配置。

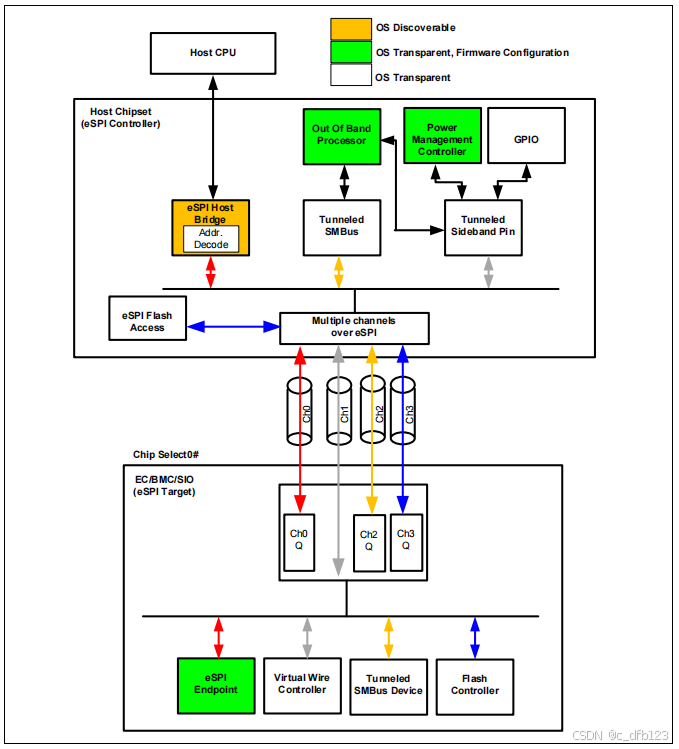

2.3、架构描述

目前eSPI使用的系统拓扑图中,一主一从是目前经常使用的方式,因此本文主要以一主一从的方式对eSPI展开描述。

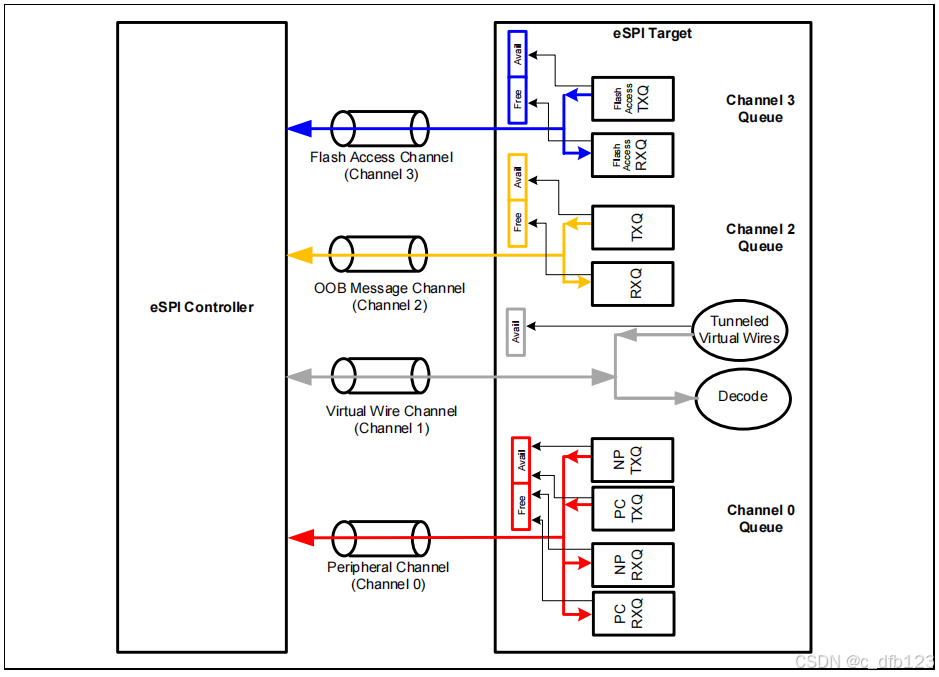

eSPI总线结构中,传输层有四个通道,在传输层章节会详细描述这四个通道。此处仅简单介绍。

1、Peripheral Channel(Channel 0),即外设通道,图中红色箭头的传输通道,该通道主要是用来传输一般的系统IO数据,比如地址0x0080,0x0060/0x0064等系统IO的地址数据。常见的Port80,ACPI,UART等都是通过Peripheral Channel传输数据。

2、Virtual Wire Channel(Channel 1),即虚拟线通道,图中灰色传输箭头,该通道主要是用来传输实体pin的电平状态,比如常见的Slp_S3/4/5等时序信号,以及SCI、SMI等中断。

3、Out Of Band Channel(Channel2) ,带外通道,图中黄色传输箭头,该通道主要是用来取代SMBus信息传输机制。比如获取CPU的温度和RTC时间等。

4、Flash Share Channel(Channel 3),flash共享通道,图中蓝色传输箭头,该通道主要是用来传输存放在Share ROM中的EC固件,EC透过eSPI总线从Share ROM中抓取EC固件至EC的芯片中。

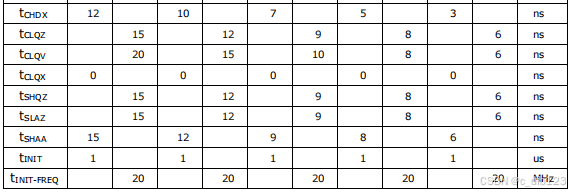

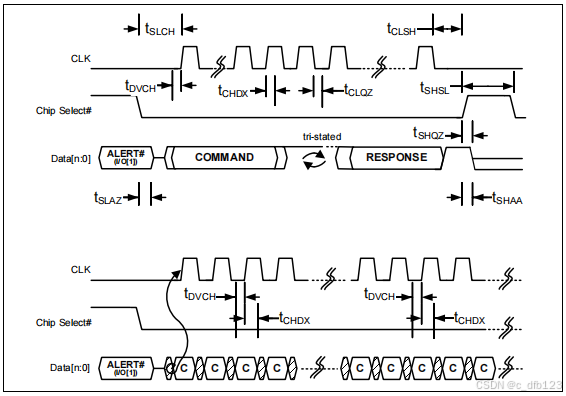

3、总线协议

eSPI协议跟SPI的模式0相同,默认状态下,时钟信号线为低,由主机控制。片选信号线为高,也由主机控制,IO[n:0]根据实际物理的连接情况决定控制权,如果是Single模式,IO0由主机控制,IO1由从机控制,IO2和IO3不使用。如果是Dual模式,IO0和IO1,主机和从机均可以控制,IO2和IO3不使用。如果是Quad模式。IO0/1/2/3,主机和从机均可以控制。IO[n:0]默认上拉。

主机或者从机在时钟的下降沿传输数据,时钟沿的上升沿采样数据。当Reset#信号拉高时,片选(CS#)信号要为高,时钟要为低。

所有的数据均是以字节(8bit)为单位。

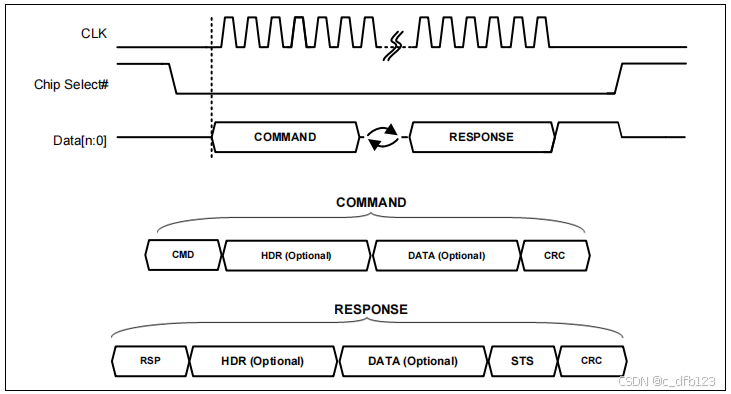

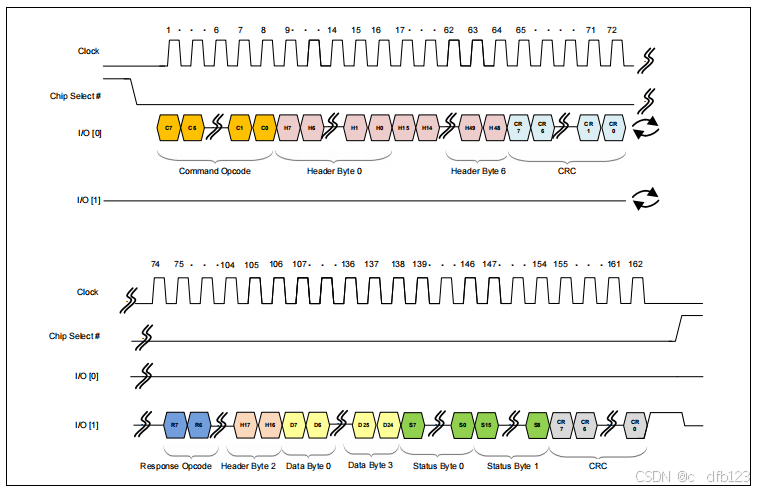

3.1、 基础协议

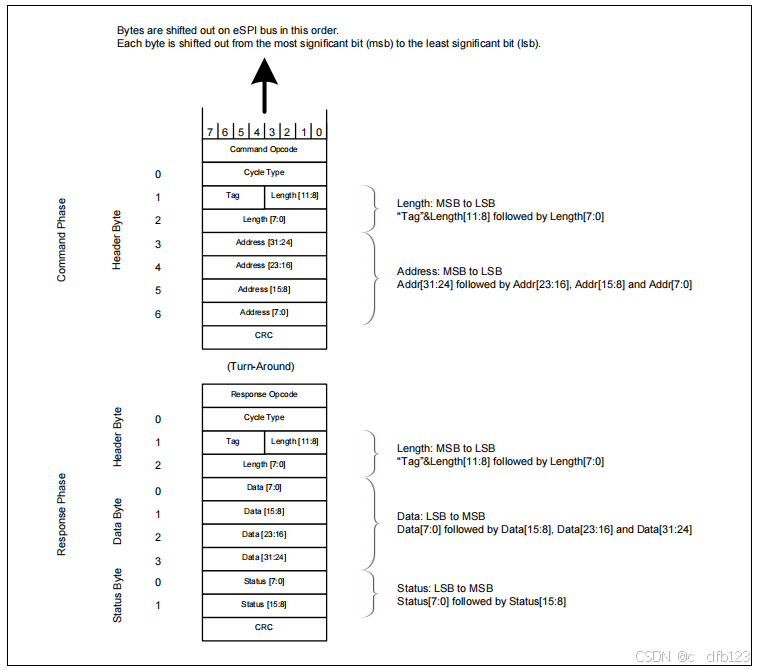

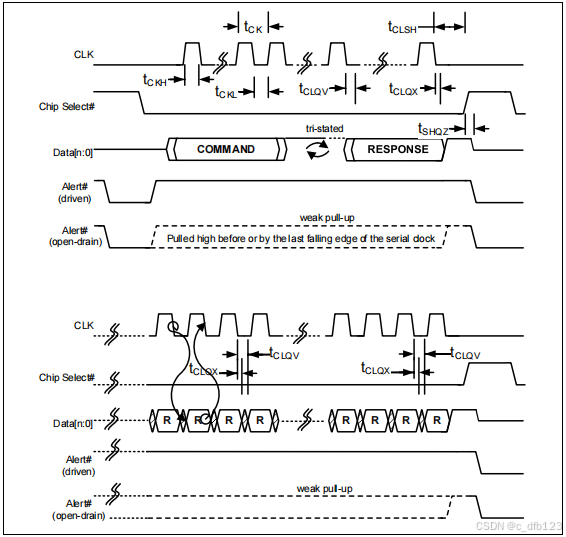

如下图是eSPI基础协议图,任何eSPI协议都可以概括如下,均有Command + Response两部分组成。

3.1.1、Command阶段

由CMD + HDR + DATA + CRC组成,其中,HDR和DATA是可选项,

-

CMD ---- Opcode,即操作码,详见表2 命令操作码。

- HDR ---- Header,命令的头部信息,主要包括Cycle Type + Tag + Length + Address。(HDR会在第四章节的传输层介绍)。

- DATA ---- Data,即实际要携带的数据。

- CRC ---- Cyclic Redundancy Check,即循环冗余校验,用以校验主机下发的全部字节。(CRC在第5章节的链路层详细介绍)。

3.1.2、Response阶段

由RSP + HDR + DATA + STS + CRC组成,其中,HDR和DATA是可选项,

- RSP ---- Response命令,即应答命令,(会在第四章节的传输层介绍)。

- HDR ---- Header,命令的头部信息,主要包括Cycle Type + Tag + Length + Address。(HDR会在第四章节的传输层介绍)。

- DATA ---- Data,即实际要携带的数据。

- CRC ---- Cyclic Redundancy Check,即循环冗余校验,用以校验从机回复的全部字节。(CRC在第5章节的链路层详细介绍)。

3.1.3、操作阶段:

3.1.3.1、从机操作

- 从机请求信号有两种,一种是驱动Alert# pin,一种是驱动IO1,在一般的Single模式下,IO1具有Alert#功能,也节省了pin脚。配置会在第6章节的一般配置寄存器中体现。

- 非Single模式下,从机请求信号必须使用Alert# pin,Alert# pin有两种配置模式,一种是推挽,一种是开漏,开漏配置的Alert#,必须要内部弱上拉。配置会在第6章节的一般配置寄存器中体现。

- 不论是IO1还是Aler#驱动,从机拉低请求信号线时,必须等到片选(CS#)拉低后再释放。

- 主机发送信息过程中,从机不对任何信号线控制,保持为tri-state。

- 在SET_CONFIGURATION命令发出Enable CRC之前,CRC可不需要检测。

3.1.3.2、主机操作

- 传输开始总是以片选(CS#)拉低时进行。

- 主机发送完信息后,会一直产生时钟,直到收到从机的全部应答信息后恢复时钟至默认态。

3.2、 Command

命令操作码,只能由主机发出,命令由一个字节(8bits)构成。命令操作码体现在四个通道中。2.3章节已经给出了eSPI的四个通道的介绍,表2列举了四个通道的命令操作码。表3说明了C1C0表示的长度含义。

| 命令操作码 | 编码[7:0] | 描述 | 备注 |

| 外设通道(Peripheral Channel) | |||

| PUT_PC | 0000_0000b | 主机下发一个中转或者完成的Header和可选数据。 | 除非从机的PC_FREE置起,否则,主机不能下发PUT_PC命令 |

| GET_PC | 0000_0001b | 主机响应并回读一个中转或者完成的Header和可选数据。 | 除非从机的PC_AVAIL置起,否则,主机不能下发GUT_PC命令 |

| PUT_NP | 0000_0010b | 主机下发一个非中转或者完成的Header和可选数据。 | 除非从机的NP_FREE置起,否则,主机不能下发PUT_NP命令 |

| GET_NP | 0000_0011b | 主机响应并回读一个中转或者完成的Header和可选数据。 | 除非从机的NP_AVAIL置起,否则,主机不能下发GUT_NP命令 |

| PUT_IORD_SHORT | 0100_00C1C0b<1> |

主机下发一个简短的非中转IO读请求包。

| 除非从机的NP_FREE置起,否则,主机不能下发PUT_IORD_SHORT命令 |

| PUT_IOWR_SHORT | 0100_01C1C0b<1> | 主机下发一个简短的非中转IO写请求包。 | 除非从机的NP_FREE置起,否则,主机不能下发PUT_IOWR_SHORT命令 |

|

PUT_MEMRD32_SHORT

| 0100_10C1C0b<1> | 主机下发一个非中转32位的内存读请求包。 | 除非从机的NP_FREE置起,否则,主机不能下发PUT_MEMRD32_SHORT命令 |

|

PUT_MEMWR32_SHORT

| 0100_11C1C0b<1> | 主机下发一个非中转32位的内存写请求包。 | 除非从机的NP_FREE置起,否则,主机不能下发PUT_MEMWR32_SHORT命令 |

| 虚拟线通道(Virtual Wire Channel) | |||

| PUT_VW | 0000_0100 | 主机下发一个虚拟线数据包给从机 | 无 |

| GET_VW | 0000_0101 | 主机响应并获取从机请求的虚拟线数据包 | 无 |

| 带外通道(Out Of Band Channel) | |||

| PUT_OOB | 0000_0110b | 主机下发一个OOB数据包给从机 | 除非从机的OOB_FREE置起,否则,主机不能下发PUT_OOB命令 |

| GET_OOB | 0000_0111b | 主机响应并获取从机请求的OOB数据包 | 除非从机的OOB_AVAIL置起,否则,主机不能下发GUT_OOB命令 |

| 闪存进入通道(Flash Access Channel) | |||

|

PUT_FLASH_C

| 0000_1000b | 主机下发一个回复给从机请求操作Flash的命令包 | 除非从机的FLASH_C_FREE置起,否则,主机不能下发PUT_FLASH_C命令。 该命令仅用于MAFS模式 |

| GET_FLASH_NP | 0000_1001b | 主机响应并下发获取从机的FLASH请求命令包 | 除非从机的FLASH_NP_AVAIL置起,否则,主机不能下发GET_FLASH_NP命令。 该命令仅用于MAFS模式 |

| PUT_FLASH_NP | 0000_1010b | 主机主动下发一个非中转的进入Flash命令数据包 | 除非从机的FLASH_NP_FREE置起,否则,主机不能下发PUT_FLASH_NP命令。 该命令仅用于SAFS模式 |

| GET_FLASH_C | 0000_1011b | 主机响应并回读从机回复的Flash数据包 | 除非从机的FLASH_C_AVAIL置起,否则,主机不能下发GET_FLASH_C命令。 该命令仅用于SAFS模式 |

| 独立通道(Channel Independent) | |||

| GET_STATUS | 0010_0101b | 主机响从机拉中断请求的相关事件 | 详见第3.4章节状态介绍 |

| SET_CONFIGURATION | 0010_0010b | 主机主动配置eSPI相关配置 | 具体配置信息详见6.2章节能力和配置寄存器 |

| GET_CONFIGURATION | 0010_0001b | 主机主动获取从机的eSPI相关配置 | |

| RESET | 1111_1111b | 带内复位命令操作码 | 软复位从机 |

| Encoding[1:0]C1C0 | 请求长度(字节) |

| 00b | 1 |

| 01b | 2 |

| 10b | 保留 |

| 11b | 4 |

注意:请求长度不能与4字节地址有交叉,因此3字节长度不允许。

3.3、Turn-Around

Turn-Around(TAR),此阶段主要是主机发送完消息后,等待从机应答,应答前有两个时钟周期的间隔期。

主机在发送消息中的最后一个字节CRC发送完毕后,会驱动IO[n:0]为高,然后进入TAR期,这个期间的时长固定为两个时钟脉冲。从机在第二个时钟脉冲的上降沿开始接手IO[n:0],下降沿时,切换输出数据,并驱动IO[n:0],TAR期之后的第一个上升沿,固定IO[n:0],因为此时主机会采样IO[n:0]。

3.4、Response Phase

此阶段是从机应答阶段,最少有三部分组成,即Response + STS + CRC。其中CRC不在协议范围内,在第5章节由硬件自动完成。

3.4.1、Response Command

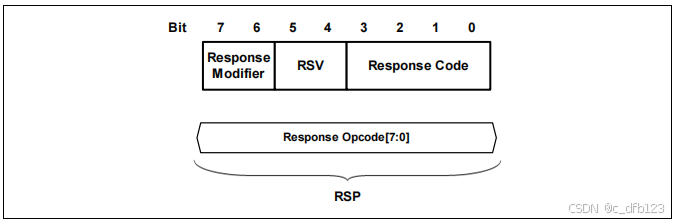

从机应答命令占据一个字节,位表示如下:

- bit[7:6]: 应答修改器(如果从机无应答,该位是00b)

- bit[5:4]: 保留(如果从机无应答,该位是00b)

- bit[3:0]: 应答码

3.4.1.1、应答修改器

默认是0,如果在应答时,有某一个通道的数据需要携带,则这两个bit位需要由从机自动设为相应的值。表4说明了应答修改器表示的含义。

| Encoding[7:6] R1R0 | 描述 |

| 00 | 没有数据携带 |

| 01 | 外设通道数据携带 |

| 10 | 虚拟线通道数据携带 |

| 11 | Flash通道数据携带,仅适用于SAFS模式 |

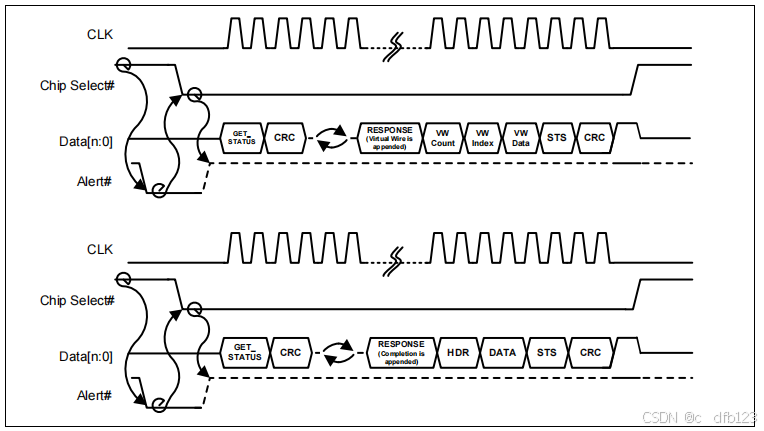

下图给出了应答时,携带了虚拟线通道数据或者是完成某个操作的应答数据。展示了主机在收到从机的中断请求时,主机获取从机的状态,从机顺带把数据跟随状态一并给到主机。

3.1.4.2、应答码

应答码是从机特有的,主机在下发相应的命令给到从机后,从机需要应答。应答码如表5所示。

| 应答码 | Encoding[3:0] | 描述 |

| Accept | 1000b | 主机下发的命令或者数据,从机正常接收 |

| Defer | 0001b | 主机下发某一个片段的数据,从机需要延迟完成 |

| NON_FATAL_ERROR | 0010b | 从机接收的数据没有致命的安全性错误,该错误不影响正常的命令接收 |

| FATAL_ERROR | 0011b | 接收的命令有致命的错误,例如FREE未置起,主机仍旧下发该通道的数据 |

| WAIT_STATE | 1111b | 增加一个字节的延迟。比如主机回读从机,从机数据还没有准备好,需要增加延迟字节。 |

| NO_RESPONSE | 1111b | 从机异常,不能正常响应主机的命令. 这里需要跟WAIT_STATE区别一下,此应答码的高4位也为1,即应答是1111_1111b,也就是从机不驱动IO[n:0] |

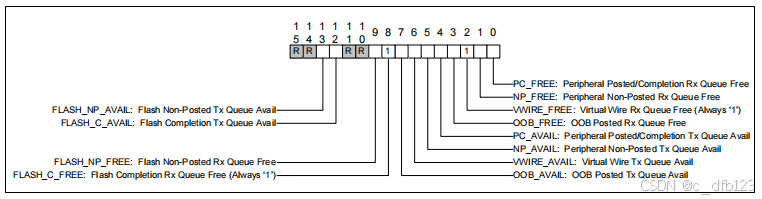

3.4.2、状态

从机应答,除了应答码,还要回复当前从机的状态(STS),状态有两个字节(16bits)组成,下图展示了状态位的实际含义。

表6展示了各状态位的含义。

| 状态名称 | 位 | 描述 |

| 从机接收队列空闲 | ||

| PC_FREE | 0 | 为‘1’表明外设通道可以接收及时反馈接收结果的数据或者完成数据 |

| NP_FREE | 1 | 为‘1’表明外设通道接收非及时反馈接收结果的数据或者完成数据 |

| VWIRE_FREE | 2 | 该位总是‘1’,表明虚拟线通道可以任意场景接收数据,不受流控制。 |

| OOB_FREE | 3 | 为‘1’表明,OOB通道可以接收数据。 |

| FLASH_C_FREE | 8 | 为‘1’表明,Flash通道可以接收及时反馈接收结果的数据或者完成数据。 |

| FLASH_NP_FREE | 9 | 为‘1’表明,Flash通道可以接收非及时反馈接收结果的数据或者完成数据。 |

| 从机发送队列满 | ||

| PC_AVAIL | 4 | 为‘1’表明,外设通道有及时反馈的数据要发送 |

| NP_AVAIL | 5 | 为‘1’表明,外设通道有非及时反馈的数据要发送 |

| VWIRE_AVAIL | 6 | 为‘1’表明,虚拟线通道有数据要发送 |

| OOB_AVAIL | 7 | 为‘1’表明,OOB通道有数据要发送 |

| FLASH_C_AVAIL | 12 | 为‘1’表明,Flash通道有及时反馈的数据要发送 |

| FLASH_NP_AVAIL | 13 | 为‘1’表明,Flash通道有非及时反馈的数据要发送 |

3.5、Alert阶段

Alert主要是从机状态发生变化时,拉低Alert# pin(Dual or Quad模式)或者IO1 pin(Single模式)通知主机下发GET_STATUS命令,从机返回2个字节的状态指示。从机主动产生Alert事件的条件是只要3.4.2章节中描述的状态位中,任意一个状态位发生变化,都会产生Alert请求。

产生Alert请求的条件只有如下两种:

- AVAIL由0->1

- FREE由1->0

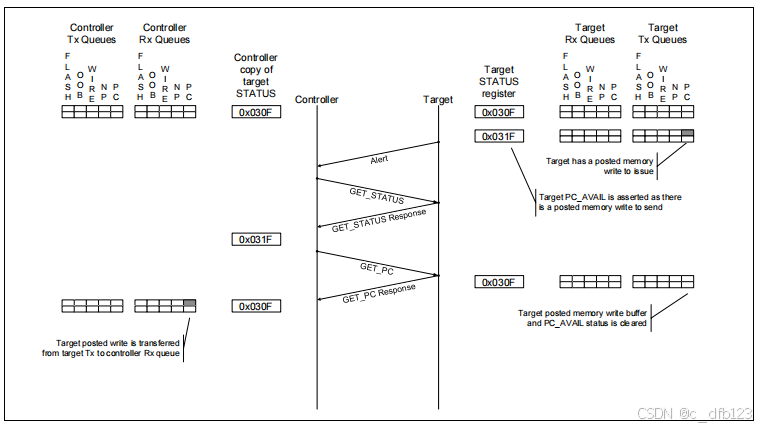

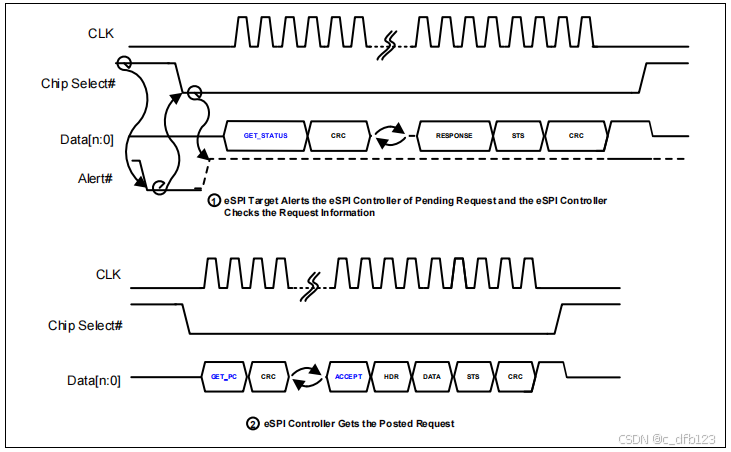

下图展示了外设通道的从机有完成数据需要反馈给主机,即PC AVAIL置起。

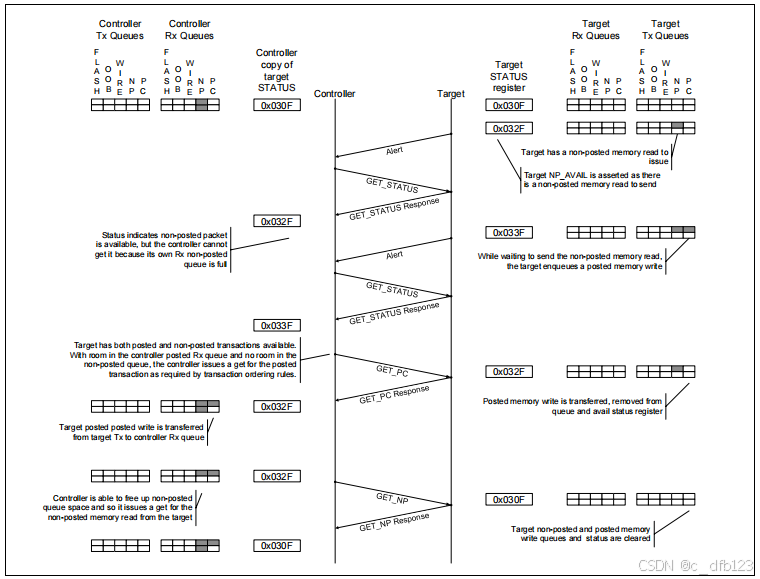

如果有Non-Posted事件(未及时需要反馈结果的信息)和Posted事件(及时需要反馈结果的信息)同时产生请求,Posted和Non-Posted优先级高,下图展示了NP_AVAIL和PC_AVAIL均置起的流程图。

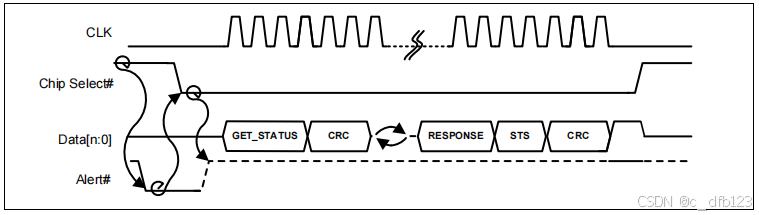

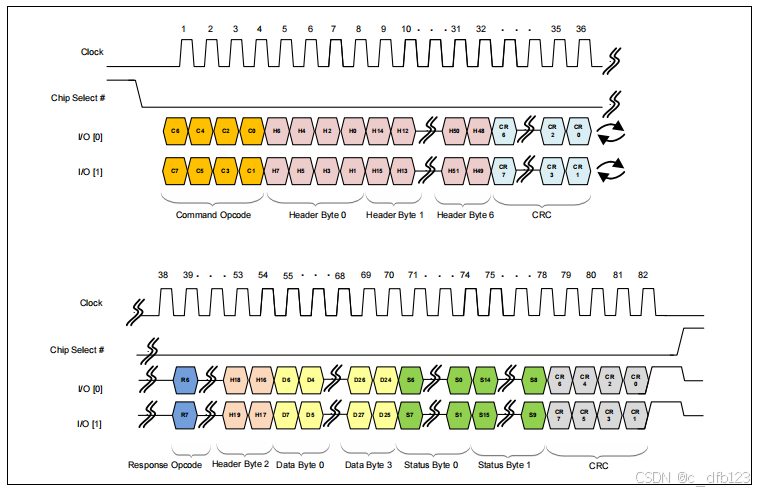

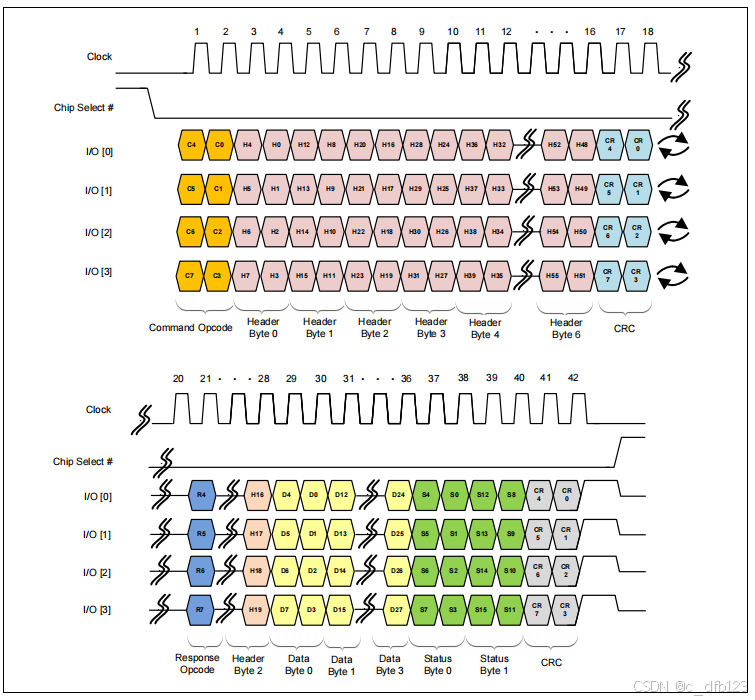

GET_STATUS命令的数据流如下图:

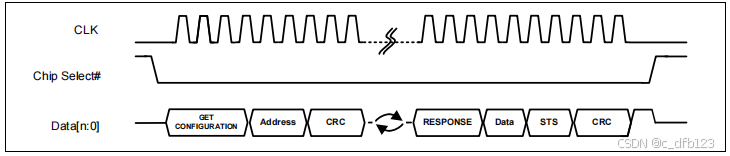

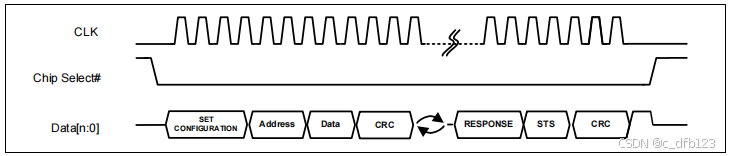

3.6、配置阶段

eSPI在通信前,会先进行一系列的通道配置和通信能力配置。涉及到GET_CONFIGURATION和SET_CONFIGURATION两个命令(两个命令分别如下图所示),配置参数在第6章节详细介绍。

- 配置能力参数由4字节数据组成。

- 偏移地址是2个字节(16 bits)组成。

- 地址是4字节对齐,因此16位地址的低两位必须是00b。

- 16位地址的高四位默认是0,从机需忽略高四位,识别低12位即可。

3.7、传输类型

3.7.1、Non-Posted传输

借用了PCIe中的消息类型,专业术语叫“非报告性事件”。我理解为非立即返回结果的事件。

比如A去买奶茶,点完饮料后等待商家做好奶茶,奶茶做好后,告诉A,让A去取。这个例子说明了,Non-Posted事件是一种非立即返回结果的事件。

此类消息类型只在外设和Flash通道中涉及,比如GET_NP/PUT_NP,PUT_FLASH_NP/GET_FLASH_NP这两个通道四个命令。

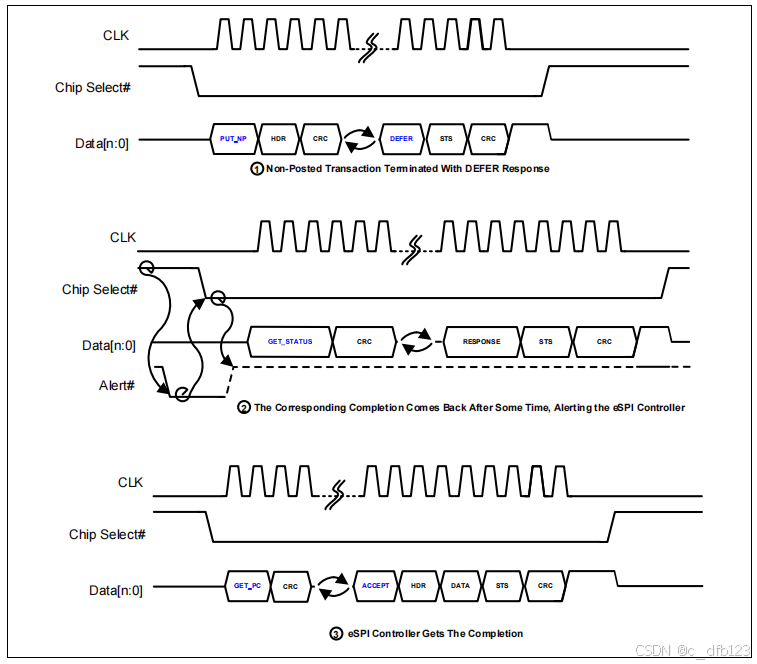

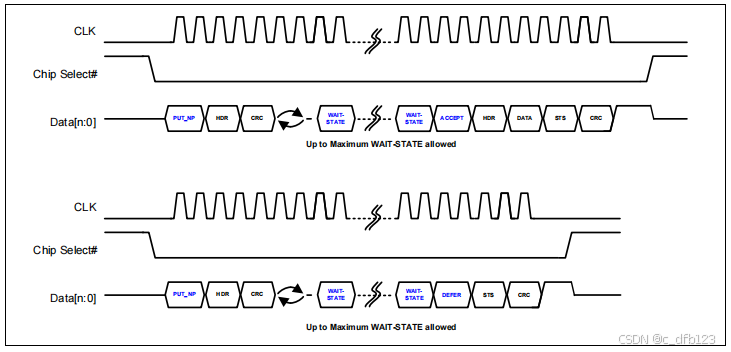

下图是主机下发PUT_NP命令给从机,从机应答为Deffer以示延迟。从机需要将数据准备好后通过产生Alert事件让主机下发GET_PC将数据回读,从机应答为Accept表示此次传输完成。

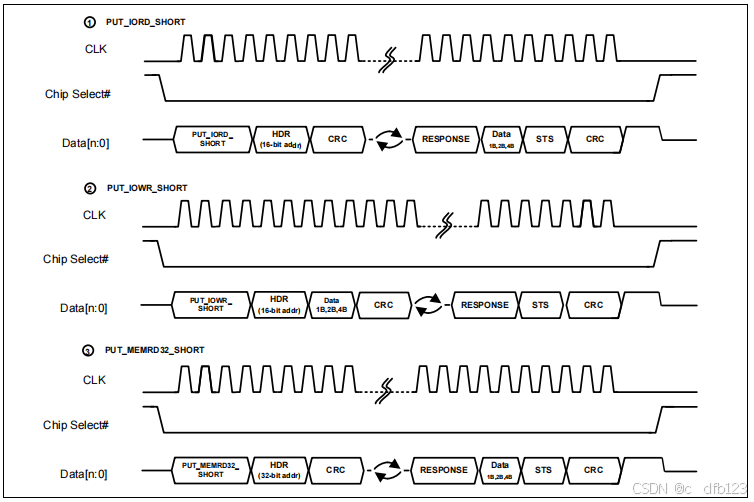

一般简短的IO信息传输虽也有Non-Posted消息类型,从机也可以回复Deffer以示延迟,但是为了提高通信效率,一般简短的IO信息,从机在应答时可以插入一定数量的WAIT_STATE来让从机准备数据。如下图是简短的IO消息传输。应答码都是Accept。

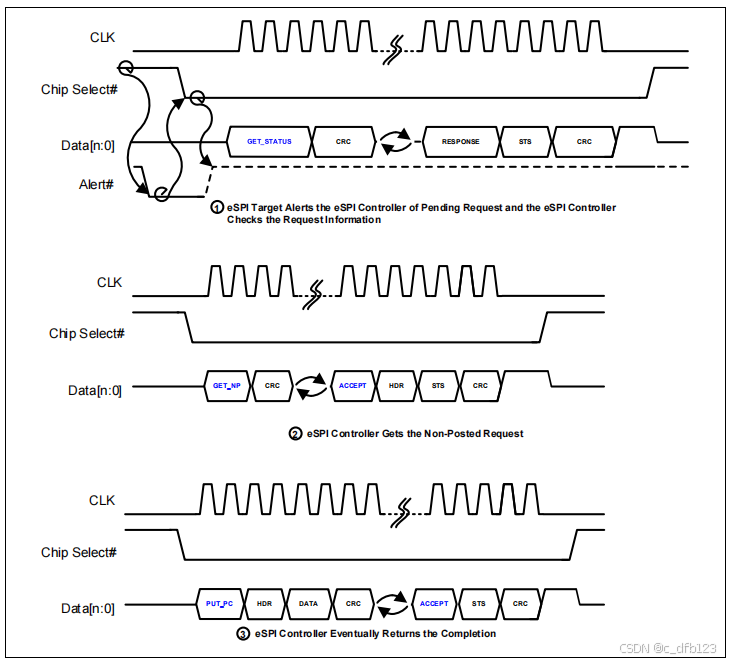

从机可以主动产生Alert请求主机进行Non-Posted通信,下图是从机主动产生Alert请求主机进行Non-Posted通信。

3.7.2、Posted传输

与Non-Posted传输不同,此类通信传输的专业术语是“报告性事件”,我认为是立即返回结果的事件。比如,A呼叫B,B立马应答,不需要B进行等待后再应答。

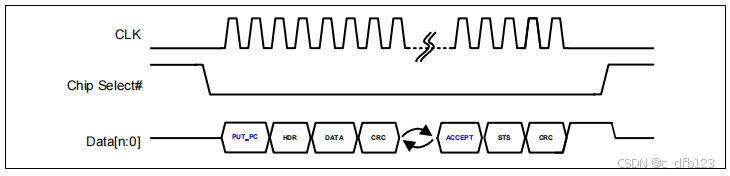

因此,从机的应答码只能是Accept,其他的应答码都是不合理的。下图是一般的Posted传输数据流。

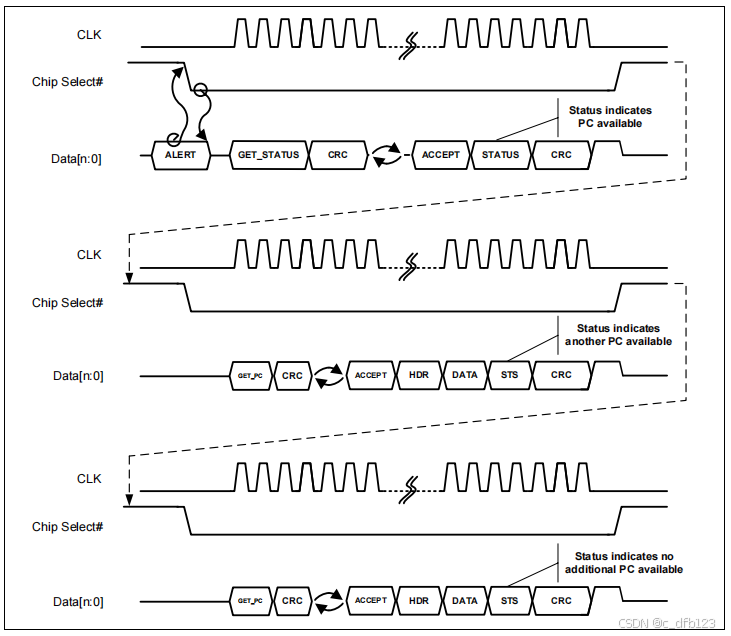

从机主动产生Alert请求主机获取Posted类型信息,数据流如下图。

下图是连续的Posted类型数据传输。

3.8、WAIT_STATE

主机下发数据结束后会进入TAR阶段,TAR结束后,从机需要应答,但是如果从机的数据还没准备好,从机会回复一定数量的WAIT_STATE告诉主机,数据未准备好需要进行等待。WAIT_STATE占据一个字节,其值为0x0F,从机最多可回复16个WAIT_STATE。最大回复个数在eSPI初始化配置里体现,由主机进行配置。

4、传输层

此章节详细介绍eSPI的数据流格式。

4.1、数据格式

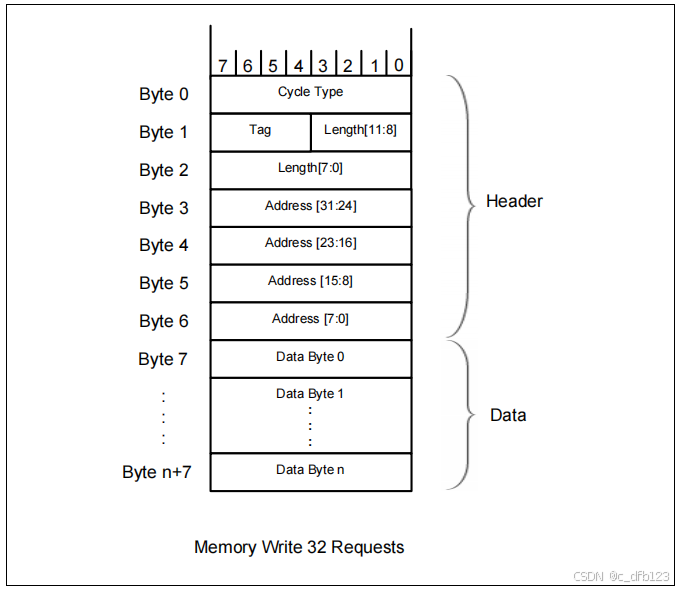

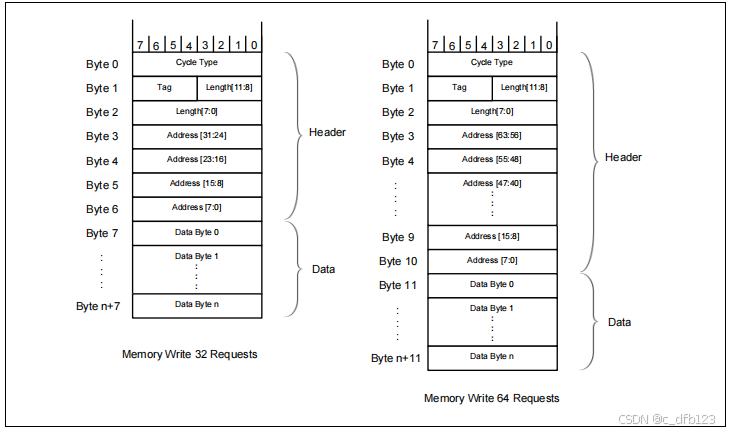

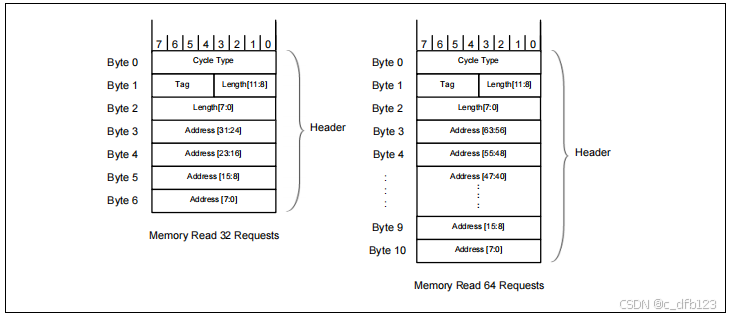

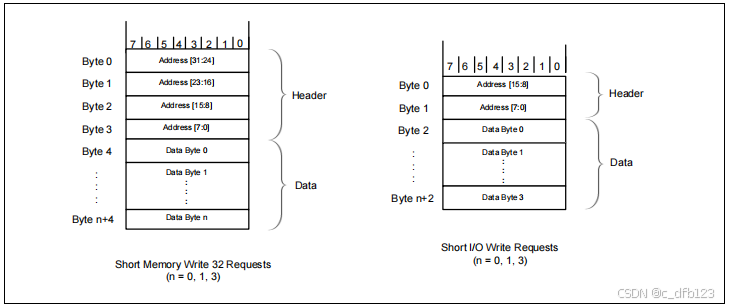

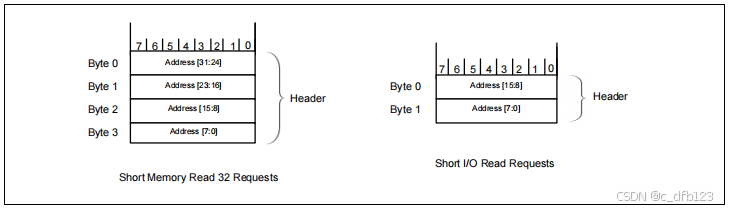

一般的数据格式如下图。由Header + Data组成。

Header = Cycle Type + Tag + Length + Address。

4.1.1、 Cycle Type

循环类型主要是用来指示主机下发命令操作码的具体行为,比如主机透过外设通道下发PUT_NP命令操作码,从机识别到是一个Non-Posted信息类型,但是这个命令操作码操作什么,需要Cycle Type呈现。Cycle Type涉及到eSPI三个通道,即Peripheral Channel,OOB Channel,Flash Channel。Cycle Type涉及到方向由DN(主机到从机),UP(从机到主机)

表7展示了各通道中Cycle Type的具体含义。

| Cycle Type | Encoding[7:0] | 方向 | 命令类型 | 描述 |

| Peripheral Channel | ||||

|

Memory

Read32

| 0000_0000b | UP/DN | Non-Posted | 32位内存读请求 |

|

Memory

Read64

| 0000_0010b | UP/DN | Non-Posted | 64位内存读请求 |

|

Memory

Write32

| 0000_0001b | UP/DN | Posted | 32位内存读写请求 |

|

Memory

Write64

| 0000_0011b | UP/DN | Posted | 64位内存写请求 |

| Message |

0001_ | UP/DN | Posted | 外设通道信息请求 |

| Message with Data | 0001_ | UP/DN | Posted | 外设通道携带数据的信息请求 |

|

Successful

Completion

Without

Data

|

0000_0110b

| UP | Completion | 成功完成传输,回复时未携带数据 用于内存或者IO的写通信 |

|

Successful

Completion

With Data

|

0000_1 | UP/DN | Completion | 成功完成传输,回复时携带数据 用于内存或者IO的读通信 |

|

Unsuccessful

Completion

Without

Data

| 0000_1 | UP/DN | Completion | 未成功完成传输,回复时未携带数据 用于内存或者IO的通信 P1总是1,表明是最后一个拆分序列或者序列全部完成 |

| OOB Channel | ||||

|

OOB

(Tunneled

SMBus)

Message

|

0010_0001b

|

UP/DN

|

Posted

| 用于传输SMBUS信息 |

| Flash Channel | ||||

|

Flash Read

| 0000_0000b | UP/DN | Non-Posted | 读Flash |

|

Flash Write

| 0000_0001b | UP/DN | Non-Posted | 写Flash |

|

Flash Erase

| 0000_0010b | UP/DN | Non-Posted | 擦除Flash |

|

Successful

Completion

Without

Data

|

0000_0110b

| UP | Completion | 成功完成传输,回复时未携带数据 用于Flash的写或者擦除的通信 |

|

Successful

Completion

With Data

|

0000_1 | UP/DN | Completion | 成功完成传输,回复时携带数据 用于Flash的读通信 |

|

Unsuccessful

Completion

Without

Data

| 0000_1 | UP/DN | Completion | 未成功完成传输,回复时未携带数据 用于Flash的通信 P1总是1,表明是最后一个拆分序列或者序列全部完成 |

| RPMC OP.1 |

0 | DN | Non-Posted |

Replay Protected

Monotonic Counter

(RPMC) Opcode 1

|

| RPMC OP.2 |

0 | DN | Non-Posted |

Replay Protected

Monotonic Counter

(RPMC) Opcode 2

|

其中可变参数定义如下

如表8所示

如表9所示

如表10所示

| Encoding[ | 描述 |

| 000 | 在接收端终止传输 |

| 其它 | 保留 |

| Encoding[ | 描述 |

| 00 | 表示拆分序列的中间序列 |

| 01 | 表示拆分序列的第一个序列 |

| 10 | 表示拆分序列的最后一个序列 |

| 11 | 表示拆分序列全部完成传输 |

| Encoding[ | 描述 |

| 00 | 表明RPMC针对于第一个Flash设备进行操作 |

| 01 | 表明RPMC针对于第二个Flash设备进行操作 |

| 10 | 表明RPMC针对于第三个Flash设备进行操作 |

| 11 | 表明RPMC针对于第四个Flash设备进行操作 |

4.1.2、Tag

针对于Non-Posted信息类型,tag用以对拆分片段编号,编号没有顺序要求,只要不为0,就说明通信不是一次完成。比如从机请求主机下发GET_NP,从机需要发送一个对主机内存的读操作,这一操作不能一次通信就可以完成,需要拆分两个片段,第一个片段,主机下发GET_NP获取从机的请求信息,从机发给主机的HDR中,Tag为1。

主机准备好数据后,通过PUT_PC将从机请求的数据下发给从机,从机需要回复

4.1.3、Length

占据12个bit的Length,最大能表示4K空间,Length出现在外设通道中对内存的访问,OOB通道中的通信,Flash通道中的通信,表示实际数据的长度。而VW通道中的Length,表示有多少对Index和Data。

虽然Length可以表示4K空间,但是不能超过相应通道的最大Payload,相应通道的最大Payload会在eSPI初始化时进行握手配置。

Length有以下几点需要注意:

- 对于Memory和Flash的读,Length必须是实际请求的Payload大小。

- 对于Flash写,Memory写,OOB信息,Cycle Type中Completion with Data,这些数据包中的Length指示实际携带的数据大小。

- 未携带数据的Completion without Data 和 Un-Successful Completion,Length必须为0。

- 对于简短的IO信息,不需要带有Length字段。

4.1.4、Address

该字段出现在Peripheral Channel、OOB Channel,Flash Channel这三个通道中,用以指示传输数据的地址。

以下是对地址的规定:

- 对于简短IO信息传输的16bit地址,该地址是System IO的实际地址。

- 对于4GB空间及其以下的访问,只能使用32-bit的内存访问。

- 对于超过4GB空间的访问,需要使用64-bit访问,

- 从机具有Bus-Master能力的,需要支持64-bit地址格式访问主机内存。

- 对于简短IO信息和简短内存访问,地址不能超过双字地址边界(一般是8字节地址)

- 内存访问可以在任意地址开始和结束,但是开始或者终端地址不能超过实际的内存地址边界。

- 开始地址和长度的组合,不能跨越4K地址边界。

4.1.5、Data

实际传输过程中携带的有效数据。

4.2、通道

多个独立的数据流控共享同一个物理总线。

GET_*,PUT_*,这两种命令开头囊括了所有的命令。

*_AVAIL,*_FREE两中标志位,体现了从机的状态。

在eSPI数据流控中,仅有四个通道,分别是Peripheral,VW,OOB,Flash四个通道,还有独立的三个命令,分别是SET_CONFIGURATION,GET_CONFIGURATION,GET_STATUS命令。

4.2.1、Peripheral Channel

外设通道,通道号是0,该通道在eSPI总线中是一个不需要软件过多参与解析的通道,ACPI,Port80,UART等常用的设备,其数据传输依托于eSPI的外设通道。

Host开机、关机、重启会触发PLTRST#(Platform Reset)信号,此信号会复位eSPI外设通道。

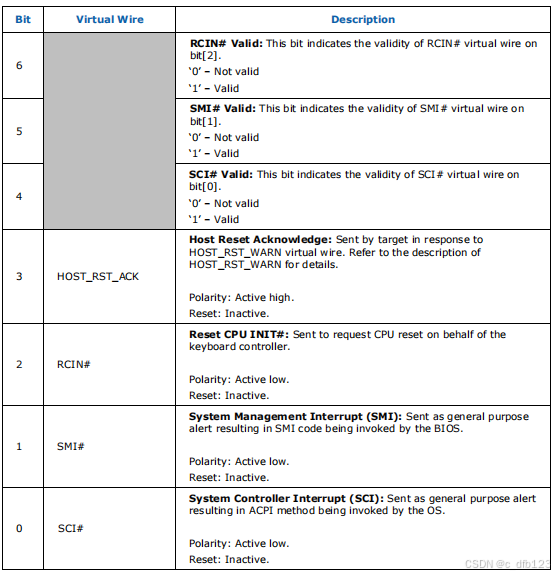

关机时,主机先透过VW通道发送HOST_RST_WARN,然后从机会回复HOST_RST_ACK,从机回复HOST_RST_ACK之后,Peripheral Channel和VW Channel均不能使用。

外设通道传输包的格式只有四种,Memory Request,short IO/Memory command Opcode,Completion,Message。

下面分别介绍上述四种传输包格式:

1、Memory Request

该传输包涉及到的命令是PUT_NP,GET_PC,GET_NP,PUT_PC

2、short IO/Memory command Opcode

该传输包涉及到的命令是PUT_IORD_SHORT,PUT_IOWR_SHORT,PUT_MEMRD32_SHORT,PUT_MEMWR32_SHORT。

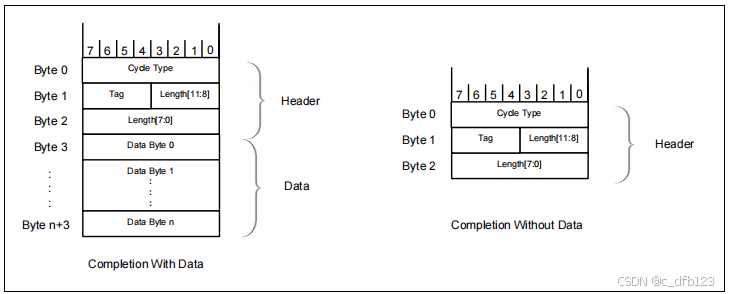

3、Completion

该传输包涉及到的命令是GET_PC,PUT_PC;Cycle Type有三种,即

4、Message

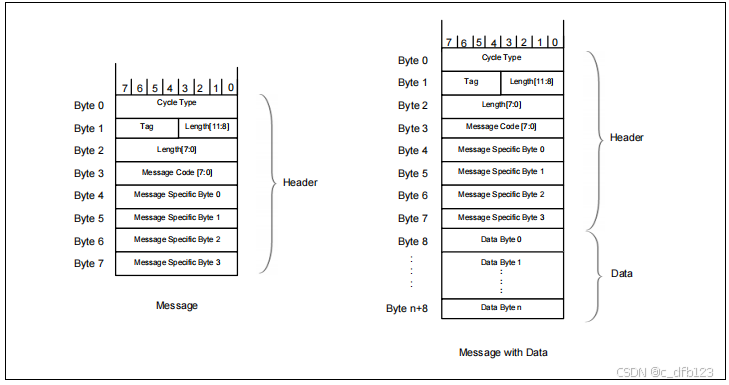

Message传输是Posted信息类型,涉及命令仅是PUT_PC和GET_PC;Cycle Type是Message和Message with Data。其中Message的length必须是0,Message with Data中的Length只是表示Data Byte的个数,不包括Message Specicific byte。

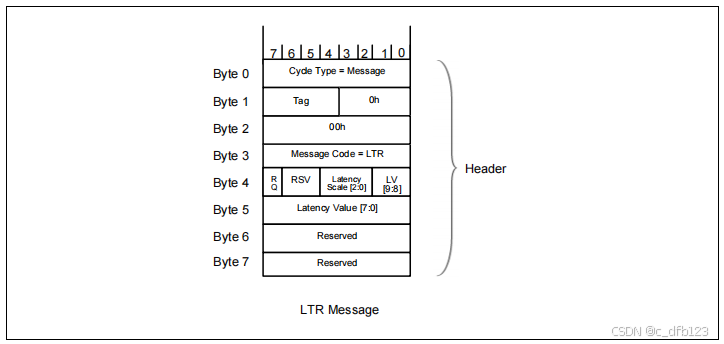

4.2.1.1、LTR

基于外设通道传输Message的是Latency Tolerance Reporting(LTR),该信息主要是用来实现从机对主机Memory的读写操作延迟限度设置。eSPI主机是必须支持LTR Message,那么从机支持Bus Master时,必须支持LTR Message。

如果从机有对主机Memory有读写要求,那么LTR必须支持。在读写主机Memory前,必须发一笔初始化LTR Message,一般推荐在外设通道使能后短时间内发送一笔LTR Message。

无论什么时候,从机的请求操作主机Memory的状态发生变化,都要发送一笔更新的LTR Message。其中就包括延迟降低或者升高。

连续两个LTR Message需要再500us内完成。

LTR使用的传输包是Message。格式如下图。

| Message bit(s) | 描述 |

| RQ | Requirements(RQ): 1:有请求延迟需求 0:没有请求延迟服务需求,eSPI不支持Bus Master时,该位为0 |

| LS[2:0] | Latency Scale(LS):最大延迟时间

000 :Value times 1 ns

001:Value times 32 ns

010 :Value times 1,024 ns

011 :Value times 32,768 ns

100 :Value times 1,048,576 ns

101 :Value times 33,554,432 ns

110 - 111 :Reserved

|

| LV[9:0] | Latency Value(LV):延迟时间值,参考LS |

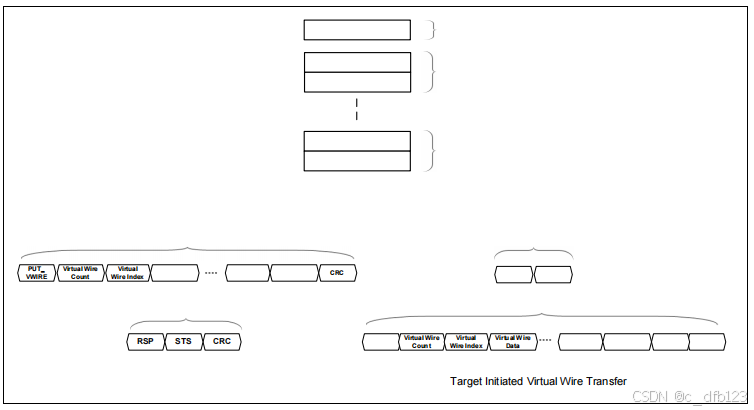

4.2.2、Virtual Wires Channel

Virtual Wires Channel(VW)主要用来传输旁带引脚状态个GPIO引脚状态作为带内信息,还有一些中断(IRQ),比如SCI,SMI,Serial IRQ等。

VW的命令组成,有Command Opcode + Count+ Index + Data + CRC(Count表示有多少对Index和Data,Count默认为0,表示有一对Index和Data)

VW不受限于流控制,因此,接收方在VW通道使能后随时准备接收VW信息。同时为保证低延迟性,VW通道的优先级比其它通道的优先级更高。

VW最多支持64个Index和Data对,一对表示一个Group,一般推荐从机支持8个Group或者更多。Count定义如表12

| Bits | 描述 |

| 7:6 | 保留 |

| 5:0 | 最多支持64个Group。 |

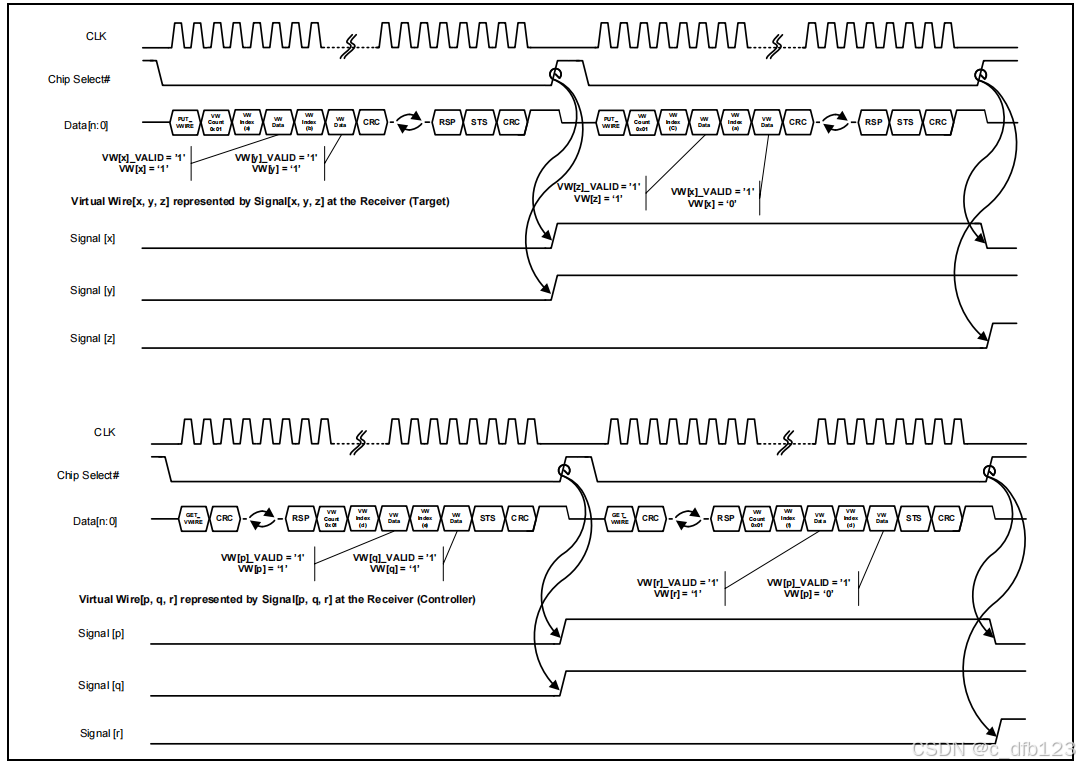

一些系统状态的电平信号可透过eSPI总线的VW通道告知从机,还有主机也可以通过VW 控制从机的GPIO状态。透过VW通道传递信号的有效性eSPI的CS#信号失效后才有效,如下图所示。

比如,当主机通过VW通道控制从机的GPIO状态,从机GPIO引脚变化在eSPI的CS#信号失效后才有效。或者主机的一些系统状态引脚信号被从机接收时,须在eSPI的CS#信号失效后才确认有效。

4.2.2.1、VW Index

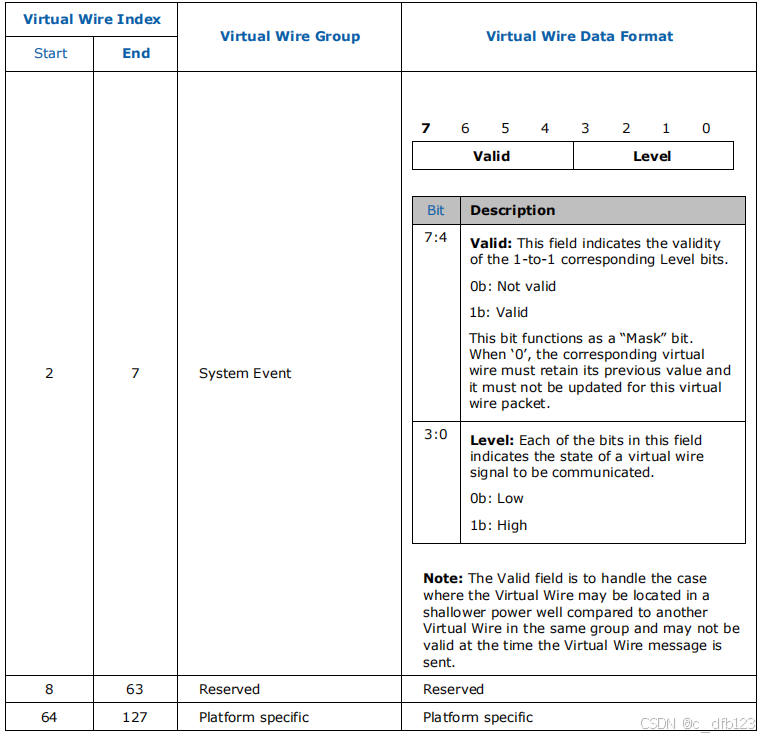

VW通道传输信息,总是以Index和Data成对出现,Index在Intel Spec中已经限定了使用范围。表12给出了VW Index。

Index占据一个字节,其值0-255

Data占据一个字节。

Index使用范围如下:

- 0-1:用于IRQ

- 2-7:System Event

- 8-63:保留

- 64-127:特别的平台

- 128-255:一般目的的GPIO拓展

4.2.2.2、System Event

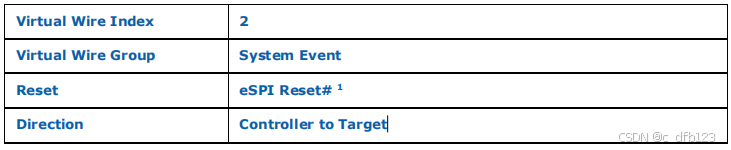

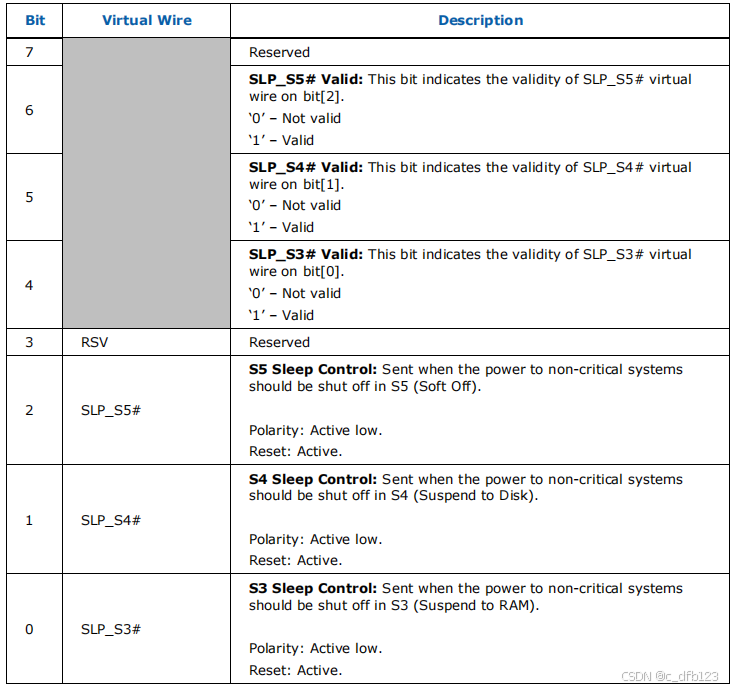

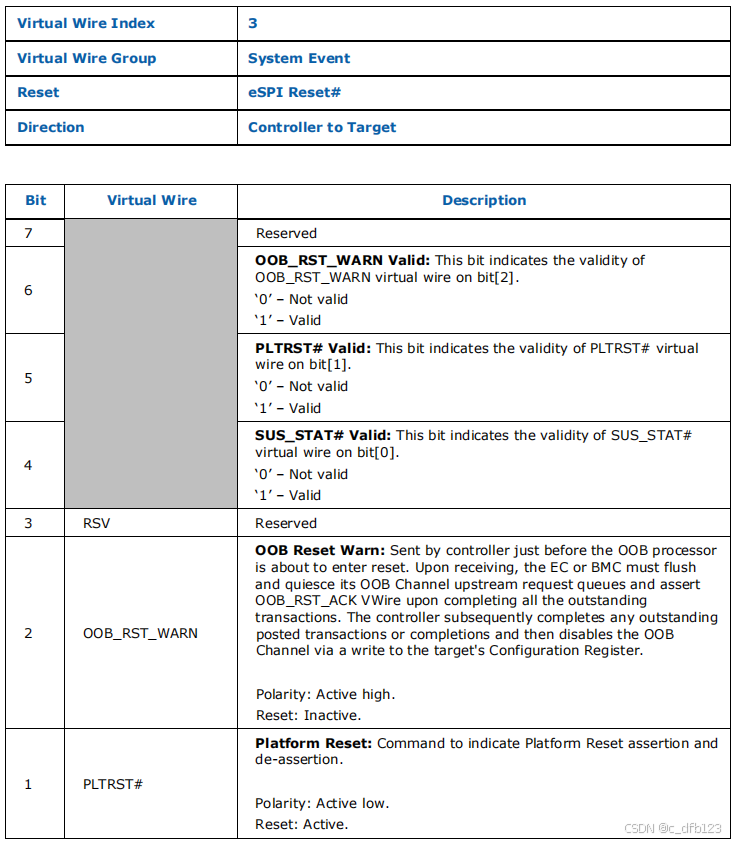

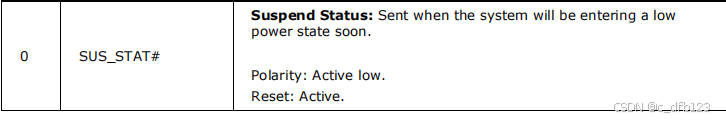

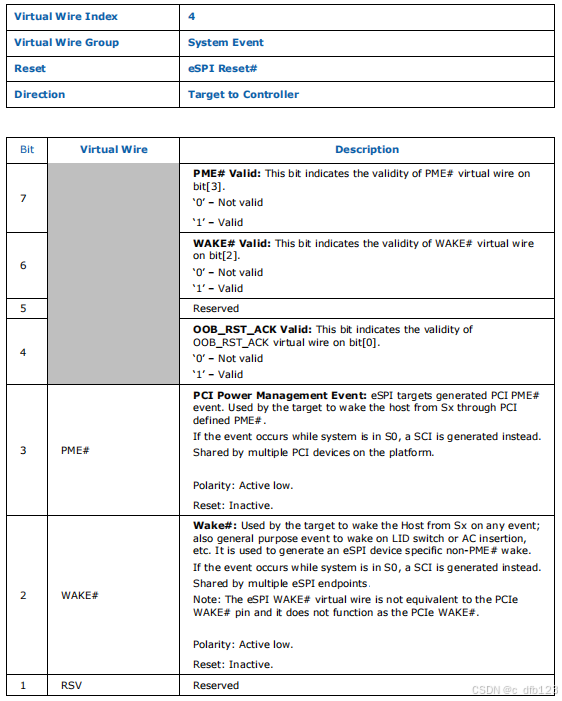

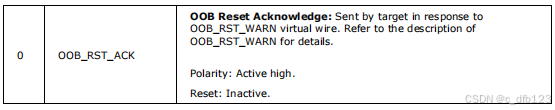

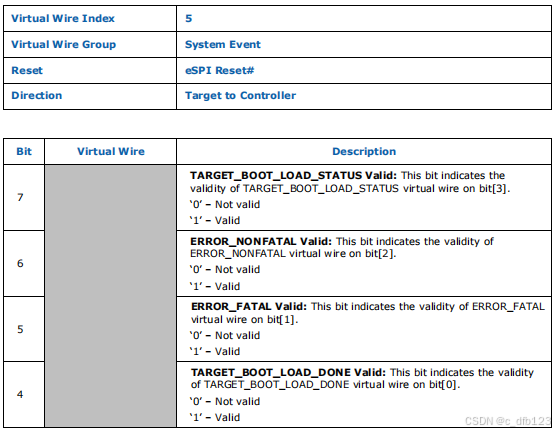

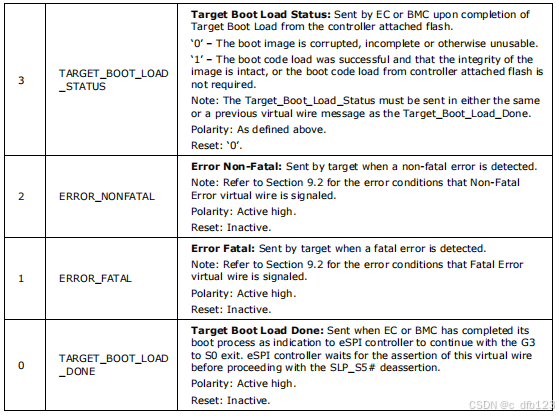

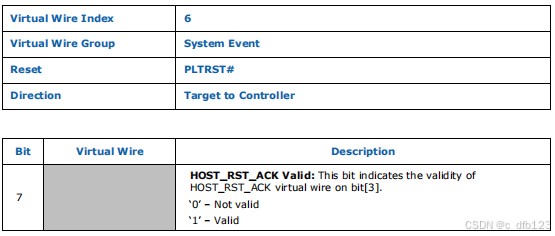

System Event透过eSPI的VW通道传递,节约了系统平台的pin脚,System Event占用了Index 0x2, 0x3, 0x4, 0x5, 0x6, 0x7, 0x41, 0x42, 0x43, 0x44,详细定义如下表。

Index 0x04, 0x05, 0x06这三个System Event 传输方向是从机到主机,其余都是主机到从机。

针对于Data中8个bit位,高四位用以表示相应低4位的状态是否有效,低4位表示实际的电平状态。

比如Index02,Data0x11,说明Slp_S3为高,且有效。其它位为低,但是无效。

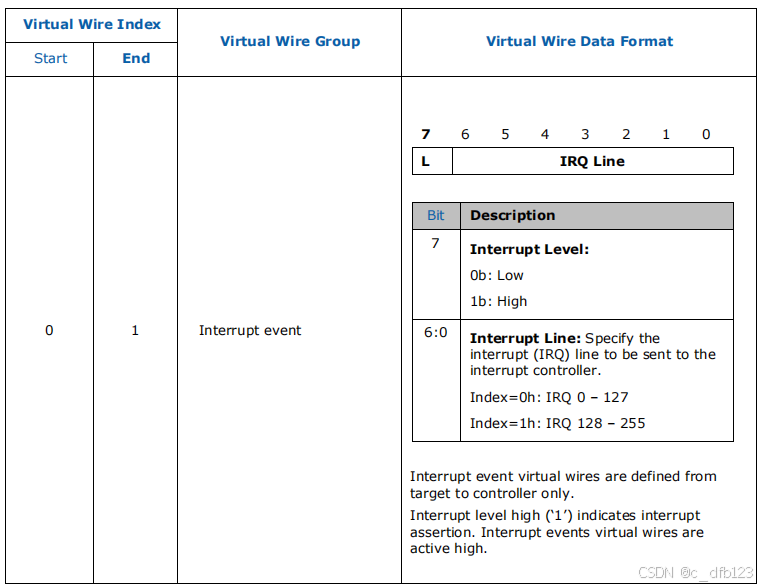

4.2.2.3、Interrupt Event

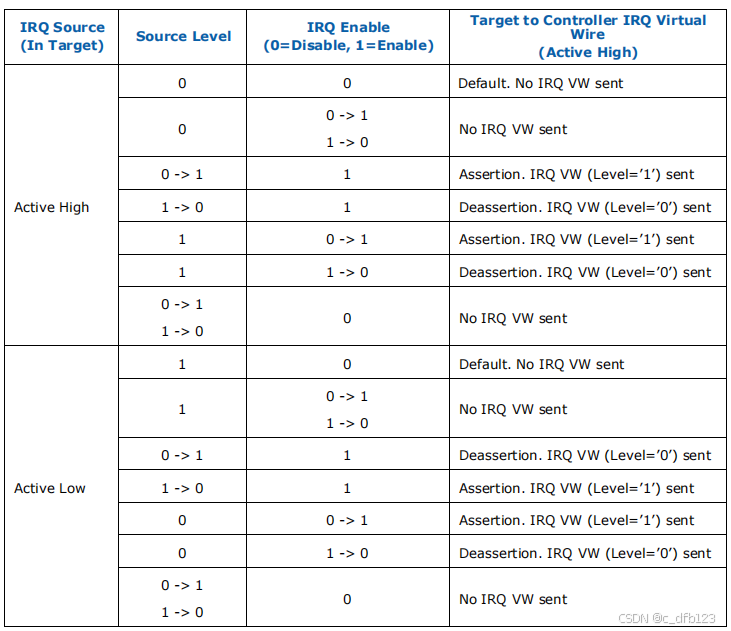

Interrupt Event占据Index 0和1,中断默认高有效。关于IRQ发送机制,下表给出了详细定义。

中断支持边沿触发和电平触发。

一般推荐使用边沿触发,边沿触发的宽度有接收者自行决定。

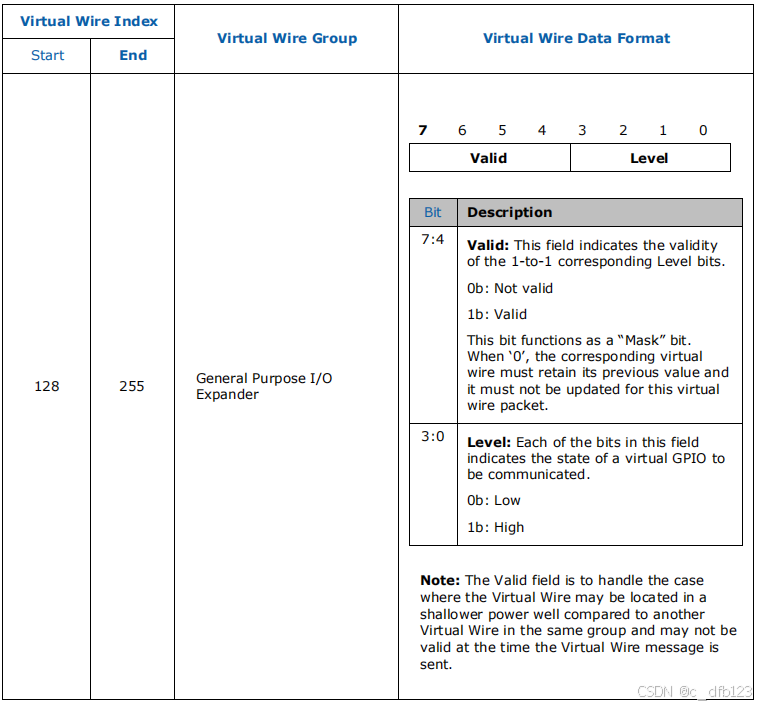

4.2.2.4、一般目的的IO拓展

允许主机通过VW通道控制从机的某些GPIO。Index限定范围在128-255。使用需注意以下几点:

- 从机的某些GPIO配置为输入,则主机通过VW通道获取从机实体IO的电平信号。

- 从机的某些GPIO配置为输出,则主机通过VW通道发送信号控制实体的IO电平。

- 从机GPIO的输入和输出不要出现在同一个Index中。

4.2.3、OOB通道

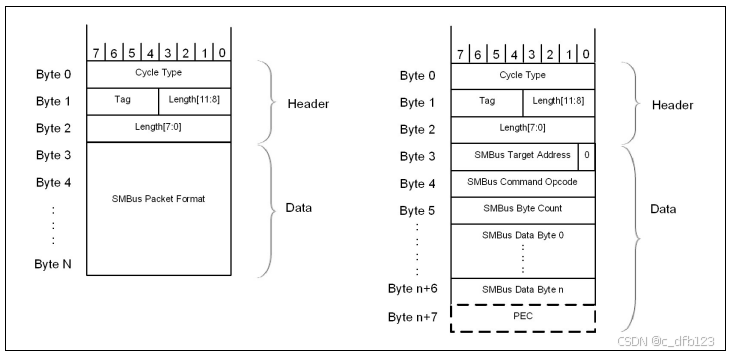

Out Of Band,带外信息,出现的目的是将SMBUS传输协议透过eSPI总线传输。OOB传输层的数据格式如下:

HDR + DATA

其中,HDR = Cycle Type + Tag + Length。

Length最大不超过73个字节大小。

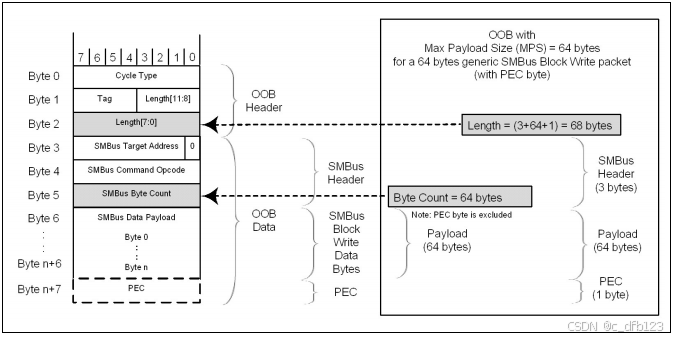

由于OOB的出现是为了将SMBUS融合进来,于是DATA里就包含了SMBUS的传输格式。具体如下图所示。

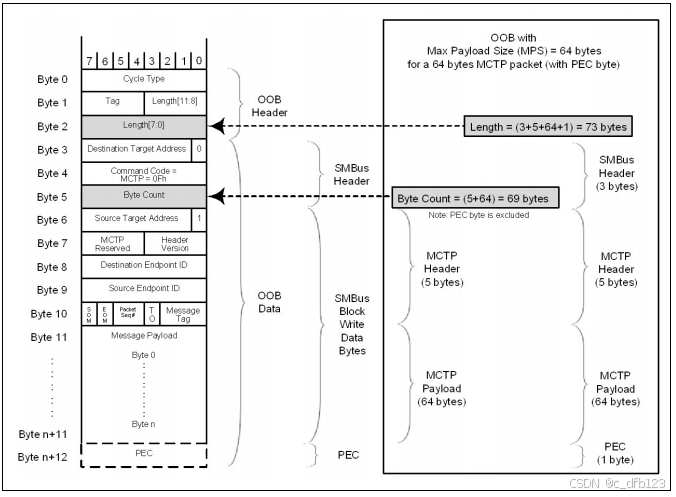

SMBus Management Component Transport Protocol (MCTP) packets也囊括在OOB传输层里。 如下图是SMBUS基于OOB协议包的数据格式。MCTP单包数据最大支持64个字节数据。

4.2.4、Flash Access Channel

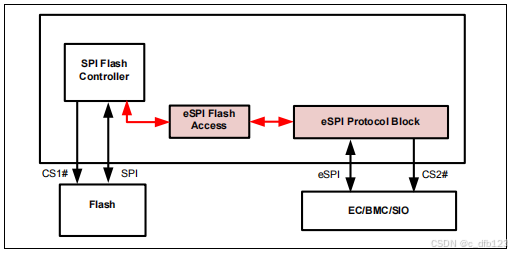

此通道主要是为了主机或者从机进入外挂SPI Flash里获取相应的数据,如果是主机外挂Flash,则从机透过eSPI的Flash通道获取EC的运行固件,现在普遍的设计是EC和PCH通过SPI共同连接到SPI Flash(Share ROM),通过SPI协议,EC可以直接获取到运行固件。

如果是从机外挂Flash,则主机透过eSPI的Flash通道获取需要的数据(包括RPMC),目前主机也支持ERPMC,从机也要求支持ERPMC,ERPMC的数据传输透过eSPI的OOB通道。所以Flash通道的使用频率在逐渐的退化。

现在的PC涉及,EC和PCH通过SPI共同连接到SPI Flash(Share ROM),因此Flash Channel使用频率较低。但是eSPI从机仍然需要具备这一功能。

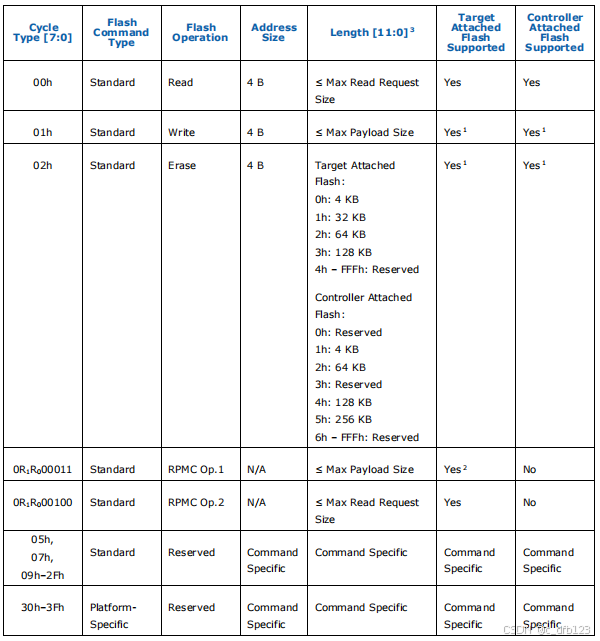

Flash支持24-bit和32-bit的地址访问,因此,不论是主机还是从机需要清楚当前外挂Flash的大小,如果只支持24-bit地址访问,则Flash通道的协议中Address[31:24]位需要忽略。

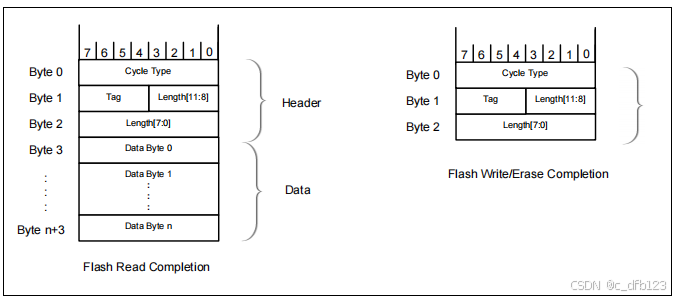

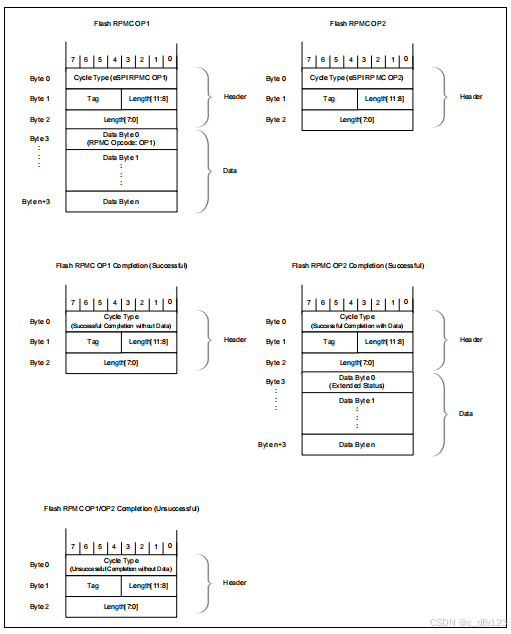

- Flash请求数据包如下

- Flash通道完成数据格式:

Flash通道的Cycle Type在4.1.1章节有介绍,下表是详细的定义。

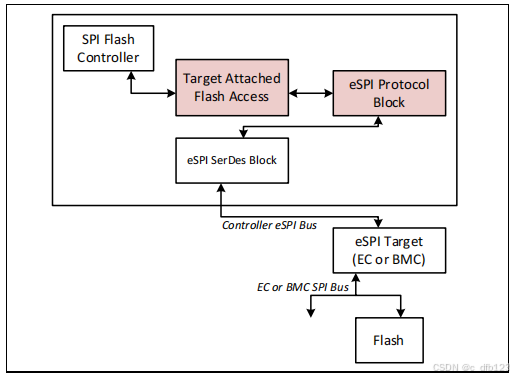

4.2.4.1、MASF

主机外挂Flash,从机获取自身运行固件只能通过eSPI的Flash通道,即使用GET_FLASH_NP和PUT_FLASH_C两个命令,结合相应的Cycle Type对Flash进行读写擦操作。

下图是主机独立外挂Flash的拓扑图。

目前业界主流做法是主机和从机都通过SPI共享SPI Flash(Share ROM)

4.2.4.2、SASF

从机单独外挂Flash,这种做法目前对于cost down而言,不是很推荐。但是也有EC单独外挂Flash用以存储EC的运行固件。同时EC单独外挂的Flash,也可以在Shell下或者系统下对EC的固件进行单独升级,主流的做法是通过外设通道进行数据传输。但是Flash通道也是支持的。同时从机外挂的Flash也可以存储RPMC,所以主机可以透过PUT_FLASH_NP 和GET_FLASH_C对从机单独外挂的Flash进行操作。

下图是从机单独外挂Flash的拓扑图。

4.2.5、从机缓冲区管理

除了VW通道,其它三个通道有消息队列要求,相应的缓冲区管理规则如下。

- 主机下命令给到从机,从机应答时必须通过状态位反应当前从机的队列状态。

- *_AVAIL置起表示从机某个通道请求主机来获取,主机依据状态位下发相应的命令来获取从机的请求。

- *_FREE置起,表示从机某个通道接收缓冲区是空闲,主机可以在该通道下命令传递信息。从机收到信息后,如果来不及处理收到的数据,该命令应答时,状态位需要把*_FREE清除。等内部数据处理完毕后,置起*_FREE,置起*_FREE时,需要产生ALERT#通知主机。

- 如果主机已获取了从机的请求,但是*_AVAIL依旧置起,说明还有请求,主机还需要根据自身消息队列情况,去获取从机的请求。

- 如果NP和PC请求同时有,从机应该先反馈PC_AVAIL,等GET_PC结束后,在把NP_AVAIL置起等待GET_NP。

- 下图展示了eSPI各通道的消息队列情况。

4.2.6、顺序规则

相同或者不同通道之前虽然没有优先级之分,但是消息有优先级之分,如下规则需要主机和从机遵守。

- Non-Posted和Non-Posted之间没有优先级之分,允许插队。

- Posted和Posted之间,需要按先到先发的顺序,不需要插队。

- Non-Posted和Posted以及Completion之间,Posted和Completion优先级最高,允许插队。

5、链路层

5.1、传输模式

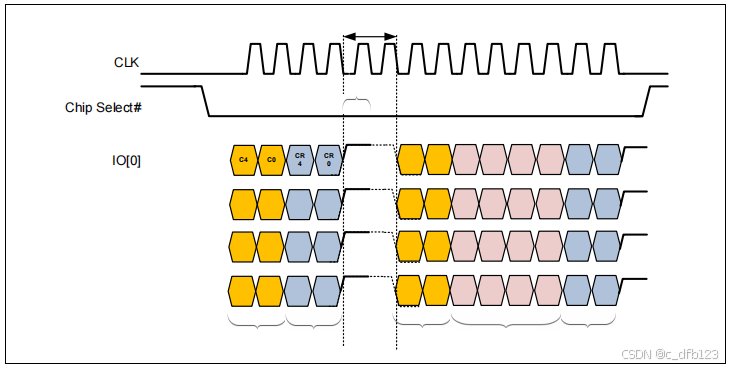

eSPI的传输模式等同于SPI,支持Single-Mode,Dual-Mode,Quad-Mode,分别是单线模式,双线模式,四线模式。

1、Single-mode:

只有CS#,CLK,IO0,IO1,Alert#(可选),Reset#,5+1根信号线

- CS#:片选,主机控制

- CLK:时钟,主机控制

- IO0:数据线0,主机控制

- IO1:数据线1,从机控制

- Alert#:中断线,从机控制,如果IO1配置了中断功能,则此信号线可不使用。

- Reset#:eSPI复位信号线,主机或者从机均可控制。

2、Dual-Mode:

只有CS#,CLK,IO0,IO1,Alert#,Reset#,6根信号线

- CS#:片选,主机控制

- CLK:时钟,主机控制

- IO0:数据线0,主机或者从机控制

- IO1:数据线1,主机或者从机控制

- Alert#:中断线,从机控制。

- Reset#:eSPI复位信号线,主机或者从机均可控制。

3、Quad-Mode:

只有CS#,CLK,IO0,IO1,IO2,IO3,Alert#,Reset#,,8根信号线

- CS#:片选,主机控制

- CLK:时钟,主机控制

- IO0:数据线0,主机或者从机控制

- IO1:数据线1,主机或者从机控制

- IO2:数据线0,主机或者从机控制

- IO3:数据线1,主机或者从机控制

- Alert#:中断线,从机控制。

- Reset#:eSPI复位信号线,主机或者从机均可控制。

- Length: From MSB (with Tag field) to LSB

- Address: From MSB to LSB. This applies to eSPI transactions with address including GET_CONFIGURATION and SET_CONFIGURATION.

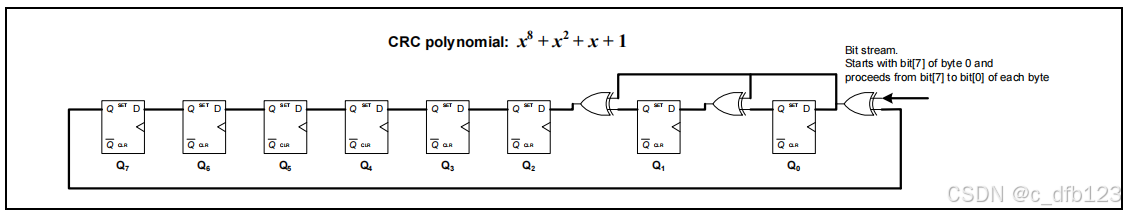

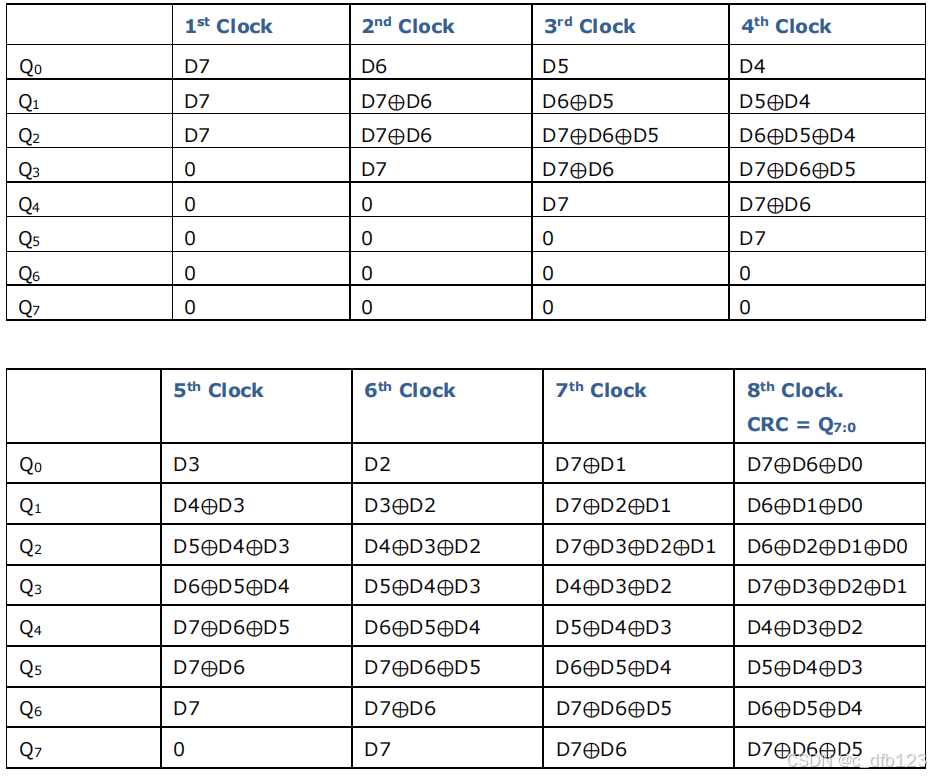

5.2、CRC

Cyclic Redundancy Check,即循环冗余校验,用以校验传输数据的准确性。

- 多项式是x8 + x2 + x + 1(表达式是0x07)。

-

输入输出不翻转。

-

从通信的第一个字节的bit7开始开始到最后一个字节的bit0结束,不包括校验的CRC值。

-

主机或者从机都需要CRC校验,且校验值跟随信息传输。

6、从机寄存器

eSPI正常工作之前,先进行握手配置,从机根据自身情况在eSPI握手之前需要先进行配置。主机根据配置顺序,对后续正常通信先配置,确保后续正常工作的通信是稳健的。

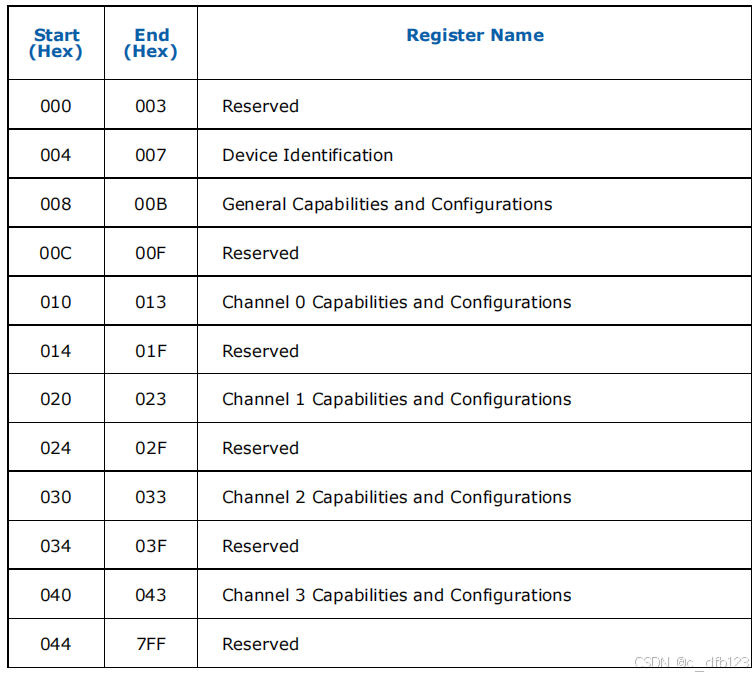

通道能力配置只涉及到SET_CONFIGURATION和GET_CONFIGURATION这两个命令,命令后面携带的16bit地址是从机寄存器的偏移量。

6.1、状态寄存器

从机的状态寄存器详见3.4.2的状态章节。

6.2、配置寄存器

eSPI通道能力配置寄存器的偏移量和描述如下表。

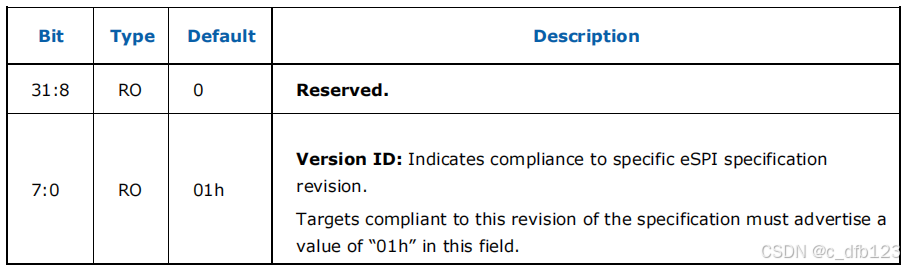

6.2.1、设备标识符

默认值为0x01,指示eSPI版本。

offset:0x04

size:0x04

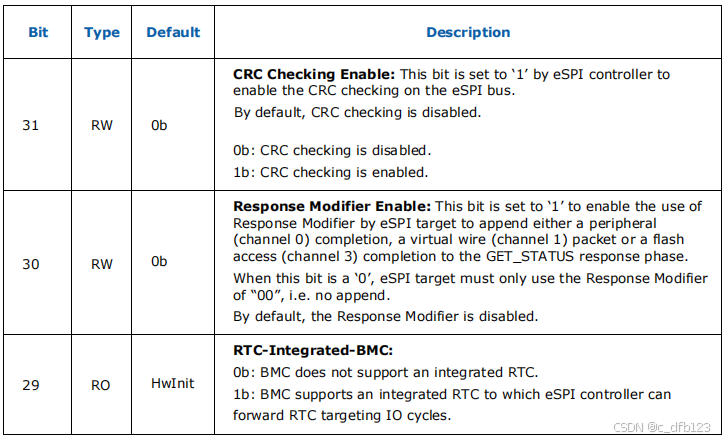

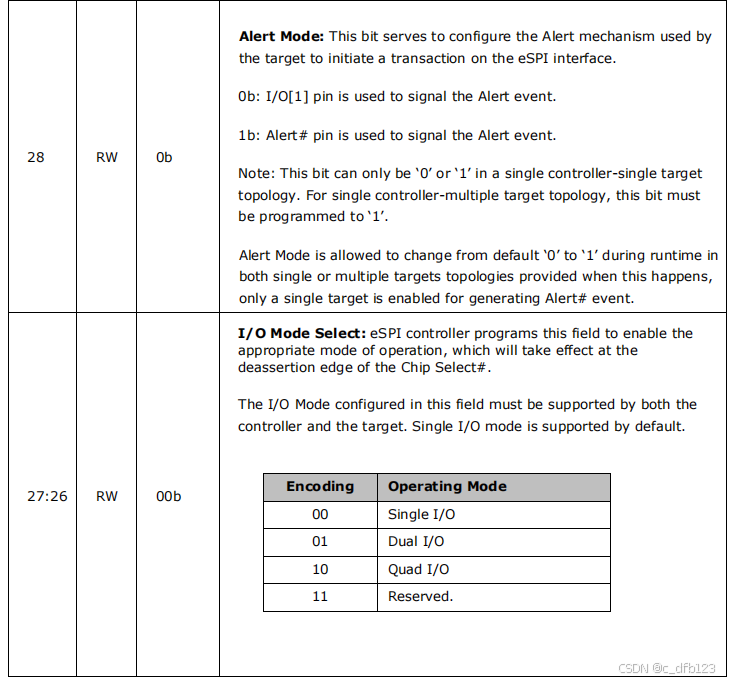

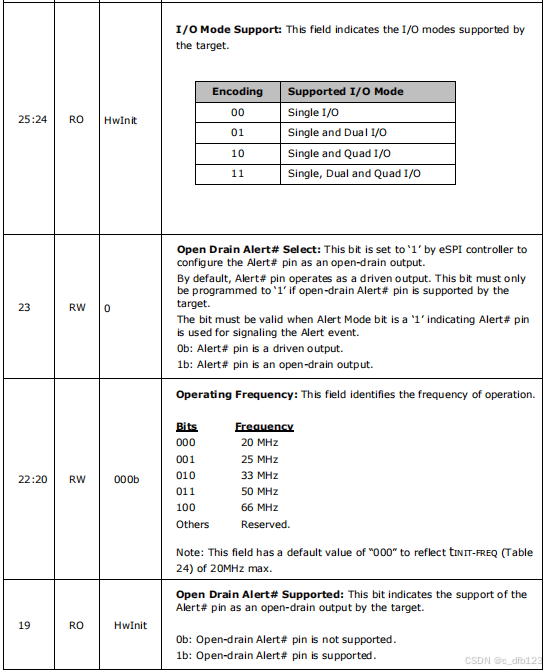

6.2.2、一般能力和配置寄存器

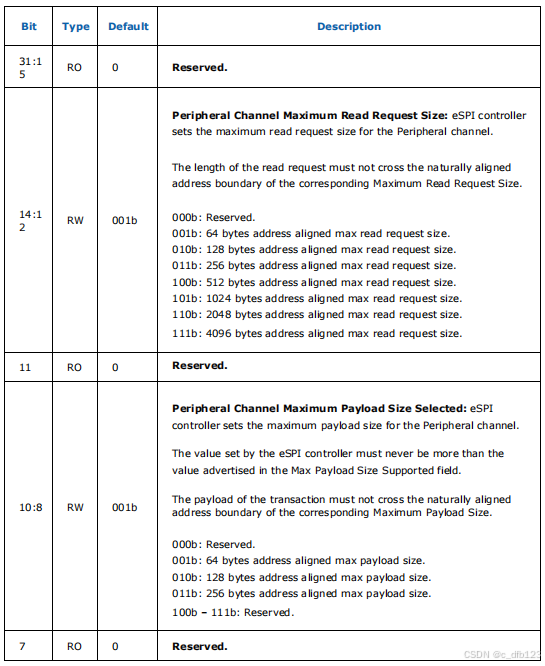

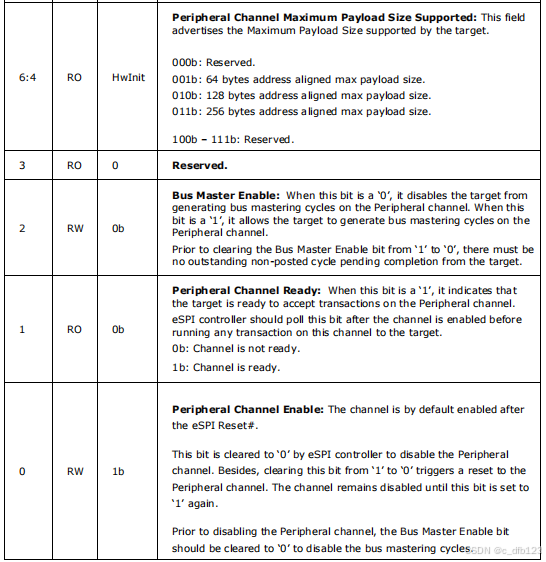

该寄存器主要用来配置通道的传输能力,比如,通信速率,各通道最大的payload等,以及通道是否需要开启等。

Offset: 0x08

Size: 0x04

6.2.3、外设通道配置寄存器

Offset: 0x10

Size: 0x04

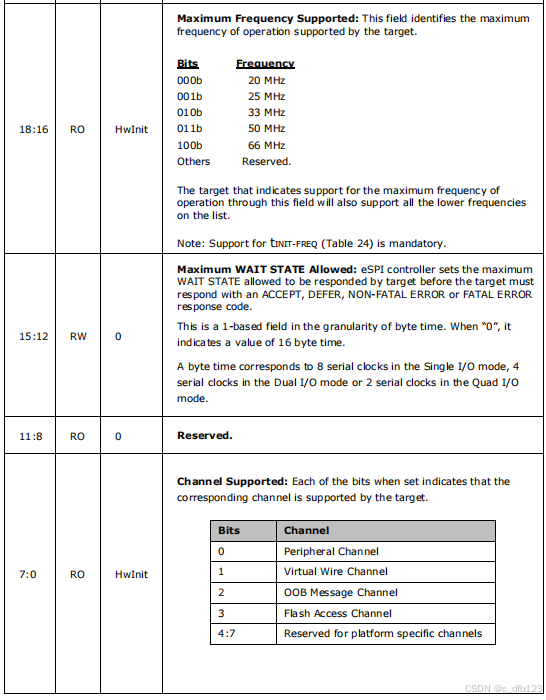

6.2.4、VW通道配置寄存器

Offset: 0x20

Size: 0x04

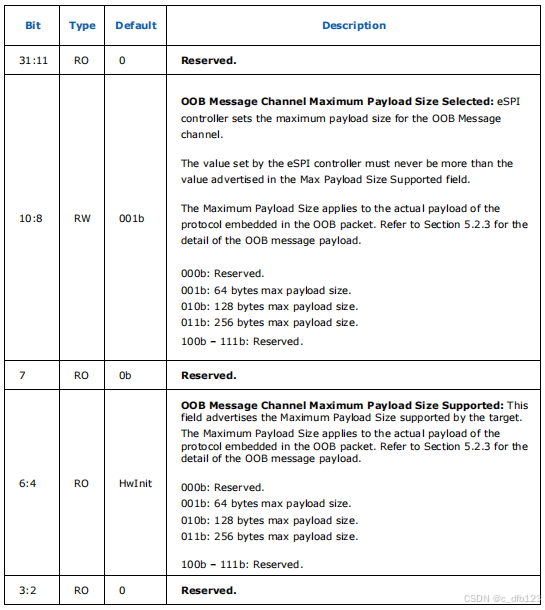

6.2.5、OOB通道配置寄存器

Offset: 0x30

Size: 0x04

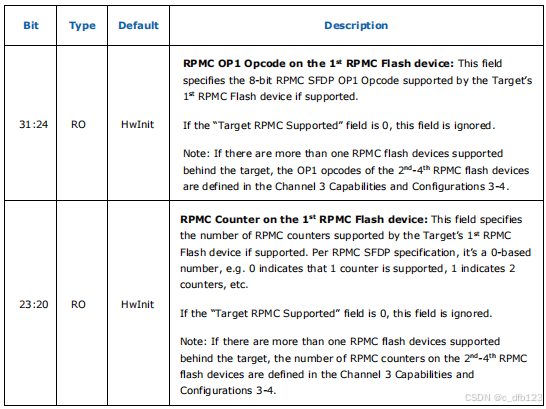

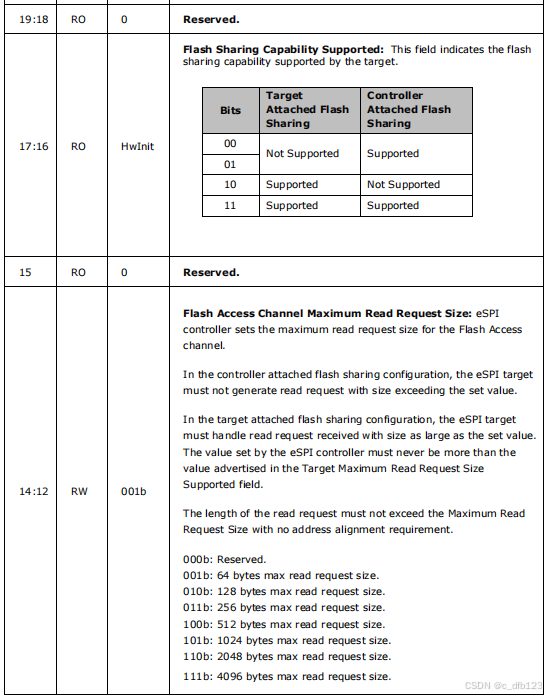

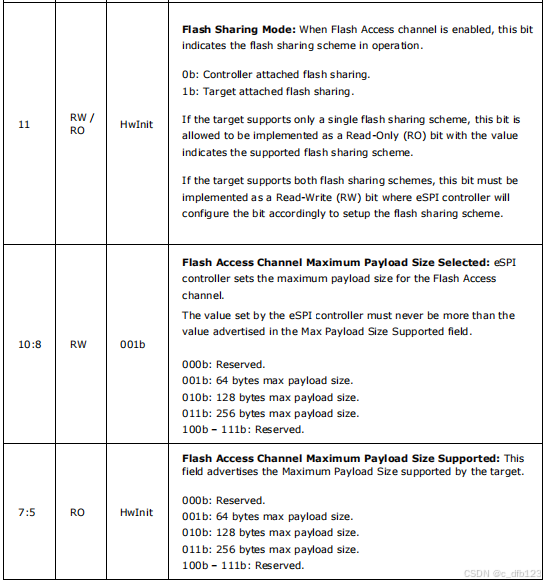

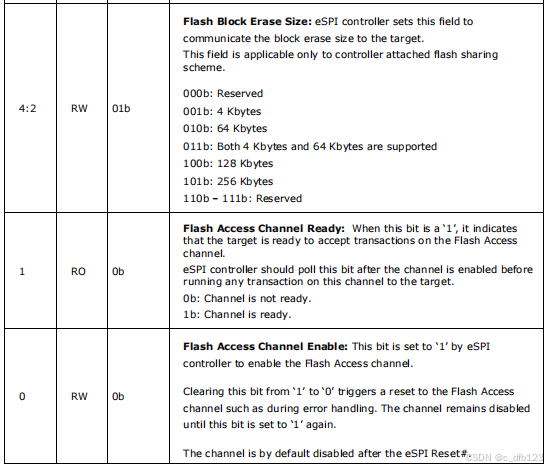

6.2.6、Flash通道配置寄存器

Flash通道能力配置寄存器还有0x44-0x4C,涉及到RPMC的配置,在EC领域,由于eRPMC的支持,Flash通道后续关于RPMC的配置将逐渐消失。

因此,本文不再列举Flash通道中关于RPMC的介绍。

Offset: 0x40

Size: 0x04

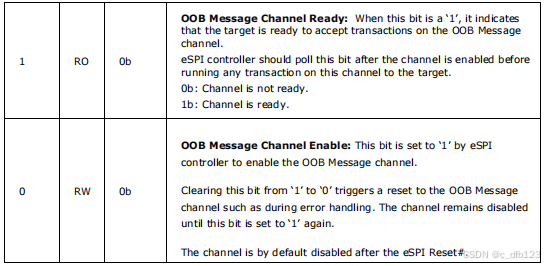

7、运行参数

7.1、电气特性参数

下表给出了eSPI的电气特性参数,工作电压在1.8V。

- 片选和数据需要弱上拉。

- 时钟需要弱下拉。

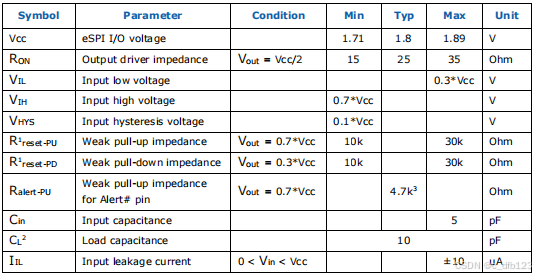

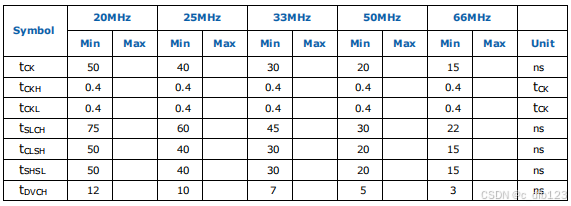

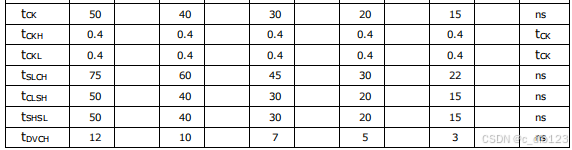

7.2、时序参数

4858

4858

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?