1 概述

1.1、信号线

Low Pin Count,是Intel于2002年提出用以替代ISA总线,总线速率最高为33MHz,一般在24MHz。该通信总线由7+6共13个信号线组成,7个必选信号和6个可选信号,其信号线如表1所示。

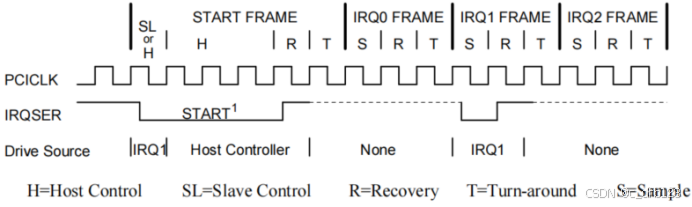

中断(Serialized IRQ)采用PCI的中断格式,具体详见1.4 Serialized IRQ

表 1 LPC信号线

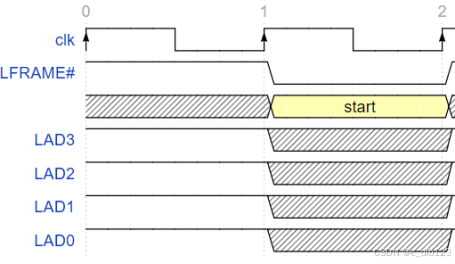

1.1.1 LFRAME#

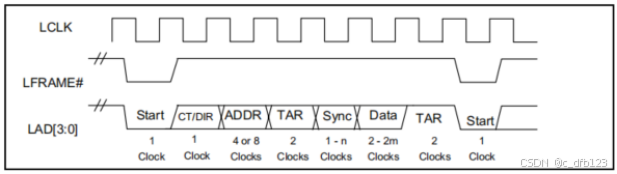

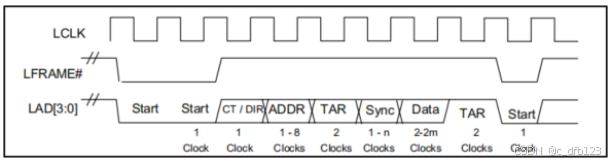

该信号线只能由主机驱动,低有效,当拉低时,指示一个Cycle即将开始或者结束,LFRAME#拉低最少占用一个clock,不超过3个clock,如果占用多个clock,那么以最后一个clock为准,LFRAME#拉低期间,从机在时钟的上升沿开始采样LAD[3:0]上的电平作为Start信号。

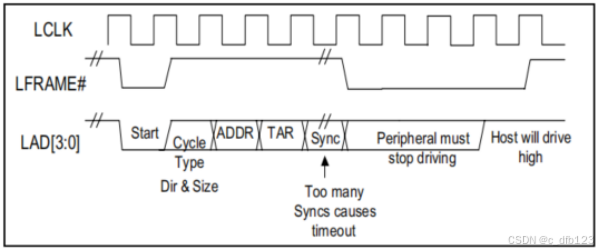

LFRAME#既可以指示Cycle通信开始,也可以终止Cycle通信,即连续拉低四个clock,指示该Cycle通信终止。

图 1典型的启动Cycle通信

图 2 拓展的启动Cycle通信

图 3 终止Cycle通信

1.1.2 LAD[3:0]

数据,指令,地址通过该组信号线传输,共四根信号线,分别是LAD3,LAD2,LAD1,LAD0,即Bit3,Bit2,Bit1,Bit0.

地址和指令传输是MSB方式,数据是LSB方式。具体传输方式如下表2。

表 2 LAD[3:0]传输方式

| 类型 |

数据值 |

LAD3(bit3) |

LAD2(bit2) |

LAD1(bit1) |

LAD0(bit0) |

clock |

| 地址/ 指令 |

0066h |

0 |

0 |

0 |

0 |

1th |

| 0 |

0 |

0 |

0 |

2th |

||

| 0 |

1 |

1 |

0 |

3th |

||

| 0 |

1 |

1 |

0 |

4th |

||

| 数据 |

34h |

0 |

1 |

0 |

0 |

1th |

| 0 |

0 |

1 |

1 |

2th |

1.1.3 LRESET#

该信号线是复位信号线,既可以是主机复位从机,也可以是从机复位主机,开漏输出。低有效,正常运行状态下,需要保持为高,否则LPC上产生的任何通信都是无效通信。

当LRESET#拉低时,从机的内部寄存器或者Buffer需要恢复默认状态。从机LPC的内部机制也要恢复至默认状态。

1.1.4 LCLK

该信号线是时钟信号线,用以同步LAD[3:0]信号线上传输的信息。LCLK只能由主机产生,从机对LCLK只能侦测,不能控制。

时钟频率最大是33.3MHz,一般在24MHz左右。

1.1.5 LDRQ#

该信号是可选信号,如果支持DMA或者Bus Master传输机制,那么LDRQ#必须支持,用以指示从机产生通信请求。该信号线是每个LPC外设单独占有,不能多个LPC外设共享一根LDRQ#信号线。一个LPC外设的DMA和Bus Master传输机制可以共用这一个LDRQ#信号线。

1.1.6 SERIIRQ

该信号线也是可选信号线,但是在LPC通信系统中,也是一个必要的信号线,它是一个用以传递中断号的信号线,具体传输协议详见1.4 章节LPC中断。

在PC中,LPC总线的中断,一般都是从机到主机的传输形式。

1.1.7 CLKRUN#

Clock Run,即让LPC时钟运行起来,该信号线是一个可选信号线,当主机进入低功耗模式,LCLK会停止,如果从机有DMA或者Bus Master请求,需要先拉高CLKRUN#通知主机把LCLK运行起来,然后拉低LDRQ#将请求传递给主机。

1.1.8 LPME#

LPC Power Management Event,该信号线是可选信号线,类似于PCI的PME信号,主要用作于从机唤醒主机,让主机推出低功耗模式。在EC与PCH的LPC总线中,该信号线可不选。

1.1.9 LPCPD#

LPC Power Down,该信号线是一个可选信号线,用作主机关机时,可告知LPC外设,让LPC外设断电或者进入设定的低功耗模式。在EC与PCH的LPC总线中,该信号线可不选。且该信号线由主机选择。

1.1.10 LSMI#

LPC System Management Interface, LPC系统管理中断,由从机到主机的传输形式。改信号是可选信号,一般使用SERIIRQ传递中断,不使用该信号线传递中断。

1.1.11 SERIIRQ

连续中断,用在LPC的通信系统中,作用是LPC的中断号传输,传输图形示意图如下:

图 4 SERIIRQ示意图

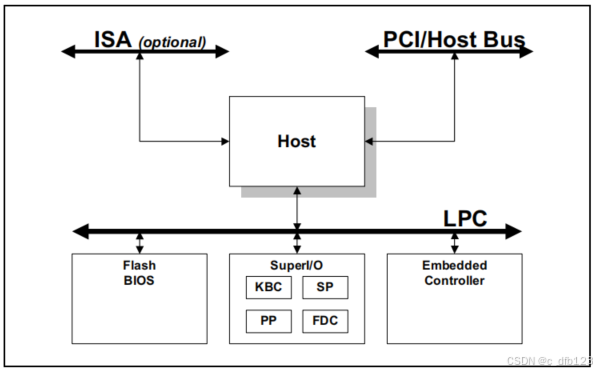

1.2、系统框图

Host Bus一般是CPU,目前SuperIO都集成到EC里,Host直接通过LPC总线访问EC的LPC从机,EC的LPC从机将信息 bypass到SuperIO。系统框图下图所示。

图 5 LPC系统框图

1.3、LPC协议

LPC协议遵循协议规范如下,底层硬件解码在时钟的上升沿采样LAD的电平值。

LFRAME#是通信的启动信号,拉低一段低脉冲后再拉高,说明主机开始与LPC外设进行通信。LPC外设在侦测到LFRAME#的下降沿后,开始准备接收信号,LFRAME#拉高表示Start信号已传输完毕,开始传输实际信息。

下表是整个LPC协议涉及到的通信协议,5种传输通道。分别是Memory,IO,DMA,Bus Master,Firmware,12种传输类型,分别是Memory R/W,IO R/W,DMA R/W,Bus Master Memory R/W,Bus Master IO R/W,Firmware Memory R/W,具体如表3所示。

表 3 LPC支持的Cycle Type

| Cycle Type |

Sizes Support |

描述 |

| Memory Read |

1 byte |

主机对LPC外设内存的读操作 |

| Memory Write |

1 byte |

主机对LPC外设内存的写操作 |

| IO Read |

1 byte |

主机对LPC外设的Super IO读 |

| IO Write |

1 byte |

主机对LPC外设的Super IO写 |

| DMA Read |

1,2,4 byte |

DMA读操作,主机和从机均可作为发起方 |

| DMA Write |

1,2,4 byte |

DMA写操作,主机和从机均可作为发起方 |

| Bus Master Memory Read |

1,2,4 byte |

LPC外设对主机的外挂内存进行读操作 |

| Bus Master Memory Write |

1,2,4 byte |

LPC外设对主机的外挂内存进行写操作 |

| Bus Master IO Read |

1,2,4 byte |

LPC外设对主机的IO进行读操作 |

| Bus Master IO Write |

1,2,4 byte |

LPC外设对主机的IO进行写操作 |

| Firmware Memory Write |

1,2,4,128 byte |

一般用于主机对从机内存的写操作 |

| Firmware Memory Read |

1,2,4,128 byte |

一般用于主机对从机内存的读操作 |

1.3.1、数据帧

1.3.1.1 Start

Start是协议开始的第一帧信息,以某个clock的高电平将LFRAME#拉低开始,下一个clock高电平将LFRAME#拉高结束,LFRAME#低脉冲阶段,读取clock上升沿时LAD[3:0]的电平值。就是Start信号的信息值。具体如表4。

表 4 Start编码定义

| Bits[3:0] |

定义 |

| 0000 |

指示IO 、Memory、DMA Cycle的开始信号 |

| 0001 |

保留 |

| 0010 |

Bus Master0 |

| 0011 |

Bus Master1 |

| 0100-1100 |

保留 |

| 1101 |

Firmware Memory Read |

| 1110 |

Firmware Memory Write |

| 1111 |

停止或终止此笔Cycle |

图 6 Start示意图

1.3.1.2 Cycle Types / Direction

Cycle Type/Direction占1 clock,数据由LAD[3:1]三个bit构成,LAD0保留且有Host或者从机驱动为0。具体定义如下表。相应的时序图详见1.3.2章节。

该数据帧仅定义在IO 、DMA、Memory这三种协议通道上。

表 5 Cycle Types/Direction 编码定义

| Bits[3:2] |

Bit1 |

定义 |

| 00 |

0 |

IO Read |

| 1 |

IO Write |

|

| 01 |

0 |

Memory Read |

| 1 |

Memory Write |

|

| 10 |

0 |

DMA Read |

| 1 |

DMA Write |

|

| 11 |

x |

保留,无论是Host还是Slave不允许驱动LAD[3:2]全为高或者是不驱动。 |

1.3.1.3 IDSEL

Device Select,设备选择,该数据帧仅用在Firmware传输通道中,该数据帧占1 clock,即LAD[3:0]上的4个bit值,该值会与固件的IC引脚上的电平值比对,一致则继续Cycle通信。该数据帧仅在主机上使用,一般是主机对外挂存储固件的访问,比如EEPROM或者Flash等。从机不需要支持Firmware传输通道。

1.3.1.4 MADDR

Memory Address,内存地址,该数据帧仅用在Firmware传输通道中。它占7 clock,28bit地址,最大支持256M的寻址范围。地址传输是MSB形式。

1.3.1.5 MSIZE

Memory Size,该数据帧仅用在Firmware传输通道中,用以指示当前Cycle通信中,传输数据的个数。占1 clock,即4 bits,具体编码如下表。

表 6 MSIZE编码定义

| Bits |

Direction |

Size |

| 0000b |

R/W |

1 byte |

| 0001b |

R/W |

2 Bytes,2字节对齐 |

| 0010b |

R/W |

4 Bytes,4字节对齐 |

| 0011b |

保留 |

|

| 0100b |

R |

16 bytes,16字节对齐 |

| 0101-0110 |

保留 |

|

| 0111 |

R |

128 Bytes,128字节对齐 |

| 1000-1111 |

保留 |

|

1.3.1.3 Size

Size用以表示传输的字节个数,占1 clock,该数据帧定义在Firmware,DMA,Bus Master三种传输通道上。Size在LAD[1:0]上具体定义如下表:

表 7 Size 编码定义

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

464

464

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?