C o r t e x − M Cortex-M Cortex−M系列处理器有32比特存储寻址,因此有4 G B GB GB的存储空间。指令和数据共享同一个地址空间,4 G B GB GB的地址空间被划分为了不同的一些区域做不同的用途。 C o r t e x − M 3 Cortex-M3 Cortex−M3和 C o r t e x − M 4 Cortex-M4 Cortex−M4系列处理器有以下一些特征:

- 多总线接口使得可以同时接入数据和指令(哈弗总线架构)

- 基于 A M B A , A d v a n c e d M i c r o c o n t r o l l e r B u s A r c h i t e c t u r e AMBA,Advanced\quad Microcontroller\quad Bus\quad Architecture AMBA,AdvancedMicrocontrollerBusArchitecture的总线接口设计,一个事实上的总线标准: A H B L i t e AHB\quad Lite AHBLite( A M B A AMBA AMBA高性能总线)协议用来进行存储和系统总线的流水线操作, A P B APB APB协议(高级外设总线)用来进行调试部分的通信。

- 支持小端和大端存储系统

- 支持非对齐数据传输

- 支持独占接入(用于嵌入式操作系统应用)

- B i t b a n d Bit\quad band Bitband

- Memory attributes and access permissions for different memory regions

- An optional Memory Protection Unit (MPU). Memory attributes and access permission configurations can be programmed at runtime if the MPU is available.

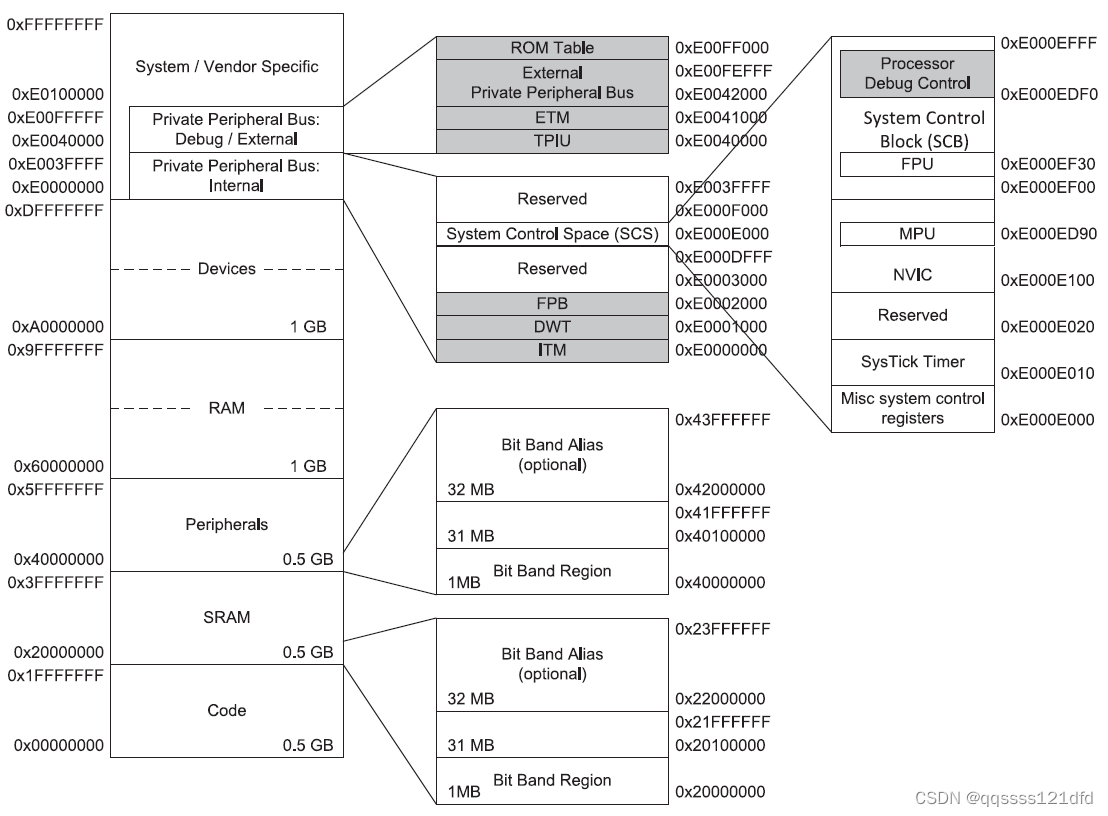

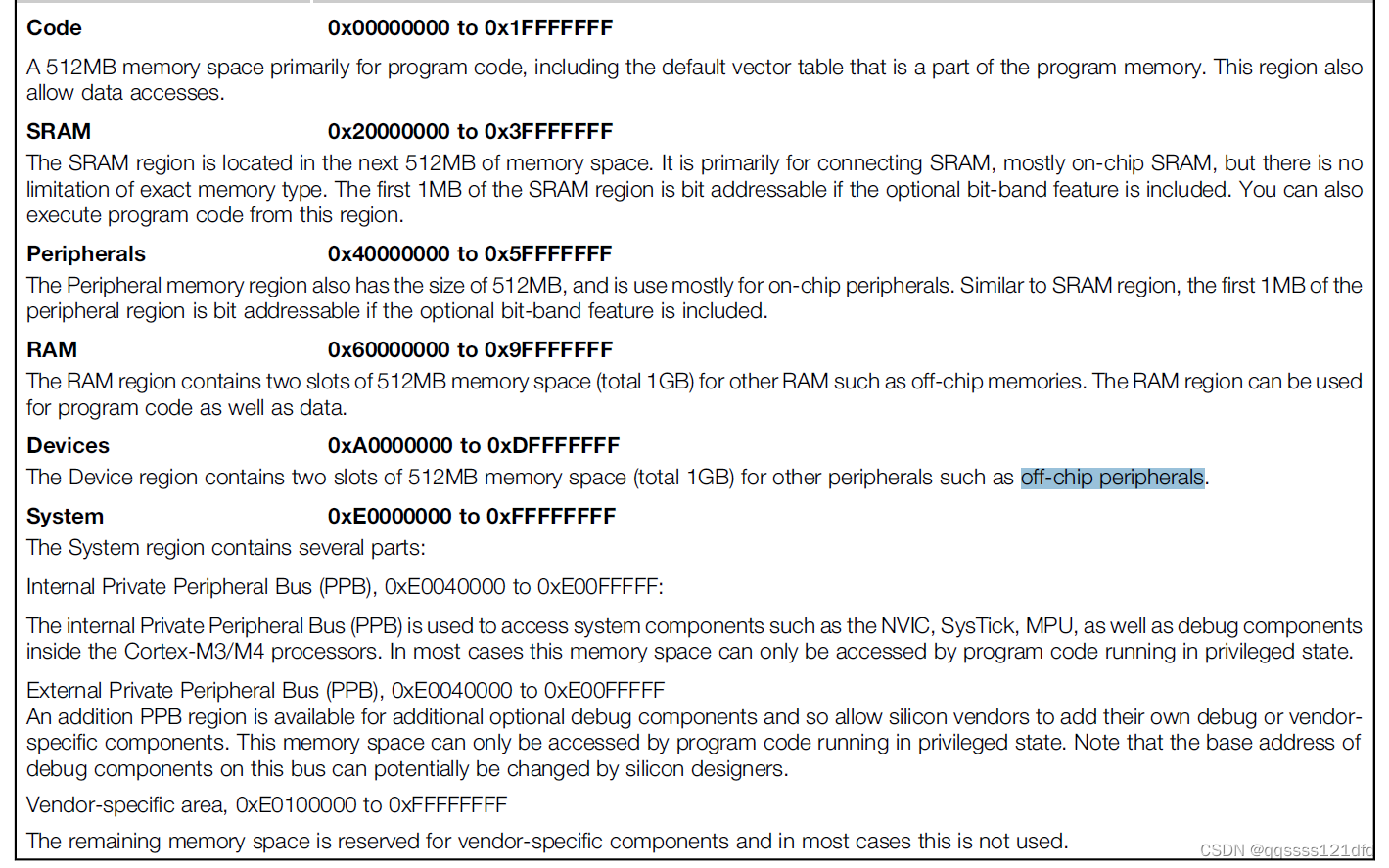

在这4 G B GB GB的可寻址的存储空间中,一部分被分配给例如 N V I C NVIC NVIC和调试部件这样处理器内部的外设,这些分配给内部外设的地址空间都是固定不变的,存储空间的大致划分如图1所示,各部分的介绍如图2所示。但是芯片设计公司可以设计不同的外设和储存器。

C o r t e x − M Cortex-M Cortex−M系列处理器基于 A M B A , A d v a n c e d M i c r o c o n t r o l l e r B u s A r c h i t e c t u r e AMBA,Advanced\quad Microcontroller\quad Bus\quad Architecture AMBA,AdvancedMicrocontrollerBusArchitecture提供了通用的总线接口。 A M B A AMBA AMBA支持几种不同的总线协议,在 C o r t e x − M 3 Cortex-M3 Cortex−M3和 C o r t e x − M 4 Cortex-M4 Cortex−M4系列处理器中, A H B L i t e AHB\quad Lite AHBLite协议用来作为主要的总线接口, A P B APB APB协议用来作为 P P B , P r i v a t e P e r i p h e r a l B u s PPB,Private\quad Peripheral\quad Bus PPB,PrivatePeripheralBus(它主要用于调试部分)。基于 A P B APB APB协议的另外的总线部分可以通过使用另外的总线桥部分而被加到系统总线中。

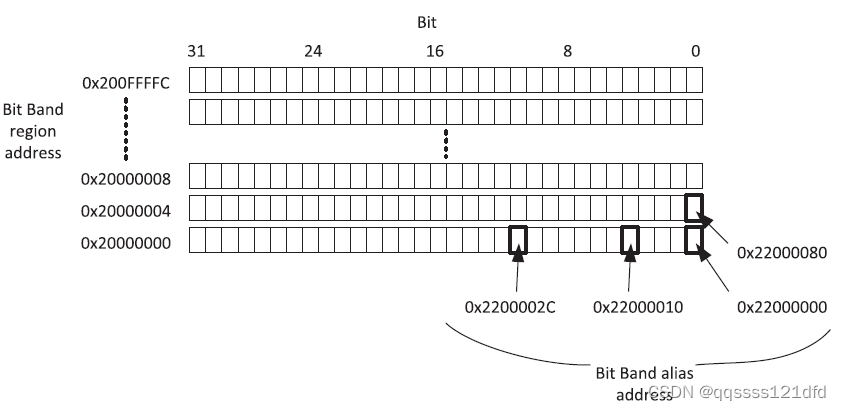

B i t − b a n d (位带) Bit-band(位带) Bit−band(位带)操作,简单的说就是可以通过一个32位地址的读写(当然这里读写的值只能是0或者1,因为一个比特位的取值范围也只有这两个值)来操作一个对应的比特位的读写。在 C o r t e x − M 3 Cortex-M3 Cortex−M3和 C o r t e x − M 4 Cortex-M4 Cortex−M4系列处理器中,有两个区域支持位带操作,就是 S R A M SRAM SRAM区域开始的 1 M B 1MB 1MB空间和 P e r i p h e r i a l s Peripherials Peripherials区域开始的 1 M B 1MB 1MB空间,如图1所示,其中 B i t − b a n d − A l i a s Bit-band-Alias Bit−band−Alias区域就是对应的 B i t − b a n d Bit-band Bit−band区域的每一个比特位对应的32位地址的区域。因为这里 B i t − b a n d Bit-band Bit−band区域的大小为 1 M B 1MB 1MB,1个比特又对应一个字,32个比特位,因此 B i t − b a n d Bit-band Bit−band区域对应的 B i t − b a n d − A l i a s Bit-band-Alias Bit−band−Alias区域的大小为 32 M B 32MB 32MB。在图3中为 S R A M SRAM SRAM区域的 B i t − b a n d Bit-band Bit−band区域的一个示意图,从图中我们可以看出,这片 B i t − b a n d Bit-band Bit−band区域的第5个比特位对应的 B i t − b a n d − A l i a s Bit-band-Alias Bit−band−Alias区域的32位地址为 0 x 22000010 = 0 x 22000000 + 4 × 4 0x22000010=0x22000000+4×4 0x22000010=0x22000000+4×4。

如果我们想将 S R A M SRAM SRAM区域开始的第4个比特位设置为0或1,通过位带操作我们的代码可以这样写:

- ∗ ( ( u 32 ∗ ) ( 0 x 22000010 ) ) = 0 *((u32 *)(0x22000010))=0 ∗((u32∗)(0x22000010))=0,设置为0

- ∗ ( ( u 32 ∗ ) ( 0 x 22000010 ) ) = 1 *((u32 *)(0x22000010))=1 ∗((u32∗)(0x22000010))=1,设置为1

如果我们不使用位带操作,而是直接操作比特位实际的地址的话,需要的操作步骤更多,一般需要先将所在的比特位的字读出来,然后去设置对应比特位的值,然后将设置好对应比特位的值得字再写回去。具体如下:

- ∗ ( ( u 32 ∗ ) ( 0 x 20000000 ) ) = ∗ ( ( u 32 ∗ ) ( 0 x 20000000 ) ) & ( 0 x F F F F F F E F ) *((u32 *)(0x20000000))=*((u32 *)(0x20000000))\quad \&\quad (0xFFFFFFEF) ∗((u32∗)(0x20000000))=∗((u32∗)(0x20000000))&(0xFFFFFFEF),设置为0

- ∗ ( ( u 32 ∗ ) ( 0 x 20000000 ) ) = ( ∗ ( ( u 32 ∗ ) ( 0 x 20000000 ) ) & ( 0 x F F F F F F E F ) ) ∣ ( 0 x 00000010 ) *((u32 *)(0x20000000))=(*((u32 *)(0x20000000))\quad \&\quad (0xFFFFFFEF))\quad |\quad (0x00000010) ∗((u32∗)(0x20000000))=(∗((u32∗)(0x20000000))&(0xFFFFFFEF))∣(0x00000010),设置为1

使用位带操作,除了上面提到的需要的操作指令少了这一优点,另一个优点是位带操作是原子操作,是不会被中断程序所打断的。但是如果不使用位带,而是直接操作比特位实际的地址的话,也许对应地址的值读取出来之后,还没有再次写进去之前就被中断打断并把这个即将写入的值给修改了,这样就会导致最后写进去的值和预期写进去的值不一致而造成问题。

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?