本来blog是打算写点关于启动相关的东西的,无奈yocto的虚拟机文件迟迟没有下载完,petalinux需要在linux环境下编译目前我的机器虚拟机跑的巨慢无比,打算字符界面操作省一些内存,现在环境还没搭好(解决了共享文件夹就OK了)。所以先搞了一些和linux启动相关不大的东西。

昨晚跑通了不带linux启动的SD卡启动流程。这里跟linux启动相比就是没有了u-boot以及对应的linux kernel和文件系统。在生成boot.bin文件的时候只需要加入fsbl.elf,system.bit,application.elf即可。这里application用的是diligent的官方例程zybo_base_system(也顺便测试了一下HDMI接口以及audio接口)。

这里diligent例程源代码工程是EDK14.7的,而我机器上目前装的是14.6版本,没法打开工程,我就想自己建一个工程。之前实验室用过了嵌入microblaze软核的架构,对EDK开发有了一定的了解,以为这个XPS工程源代码只有.mhs和.ucf来描述。但其实忽略了一个地方就是对于芯片选型的一些配置信息其实在mhs和ucf文件里都是没有描述的,具体放在哪里是不知道的,但是对工程肯定是有用的。开始选择了avnet的zed工程和自己自建空的工程,然后复制zybo_base_system里面的mhs和ucf代码,都不能正常编译。提示的是ps_system的配置有问题。google了一下发现这个zybo本身是有一个Board Definition File描述文件来描述ps_system相关信息的。如果用zed的描述信息来配zybo的源代码自然无法编译通过。因此自己建EDK工程只要导入zybo的官方Board Definition File文件即可(因为EDK原生不配ZYBO的板子)。

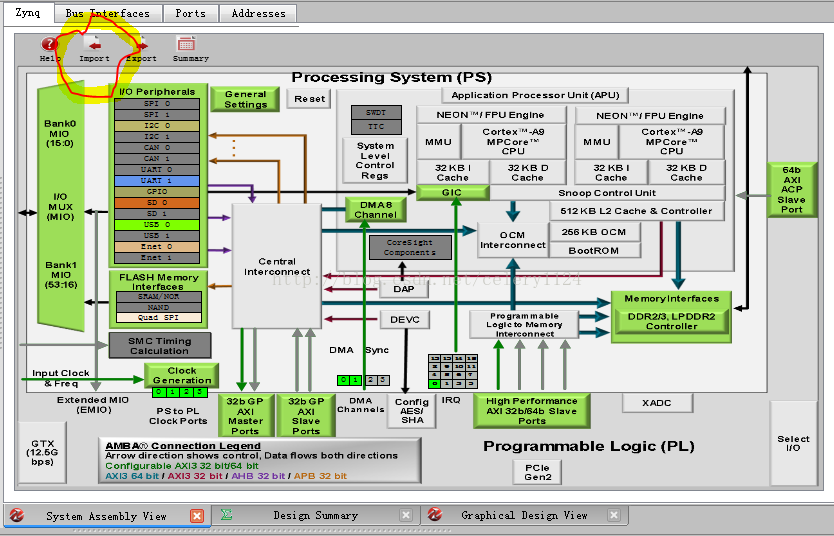

那么怎么导入这个Board Definition File还是花了点功夫,查了手册,google都没有。后来自己摸索了一下XPS发现原来在这里:(建工程的时候选择空白工程即可)

接下来就一路顺利了。。

编译过程中发现一个问题,diligent给的这个工程如果用xc7z010-clg400-1的话时序是有问题的,换成-2是可以无时序错误编译成功的。这个官网上zybo信息给的FPGA是xc7z010-clg400-1,但是Board Definition File里面是-2。这个回头要给他们技术支持发封邮件问问,可以要来他们HDMI和VGA的相关IP核的源代码优化一下。

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?