AM包络检调制解调,Vivado源码

FPGA的AM调制解调源码,其中FIR滤波器根据MATLAB设计。

【AM_jietiao】文件是基于zynq-7000系列,但没有涉及AD与DA,只是单纯的仿真。

【AM包络检调制解调_Vivado源码】文件基于Artix-7系列,从AD读入信号后,进行AM调制,并解调DA输出。

AM调制是一种常见的调制技术,广泛应用于通信系统中。在这篇文章中,我们将聚焦于FPGA中的AM调制解调源码,特别是在Vivado环境下的实现。

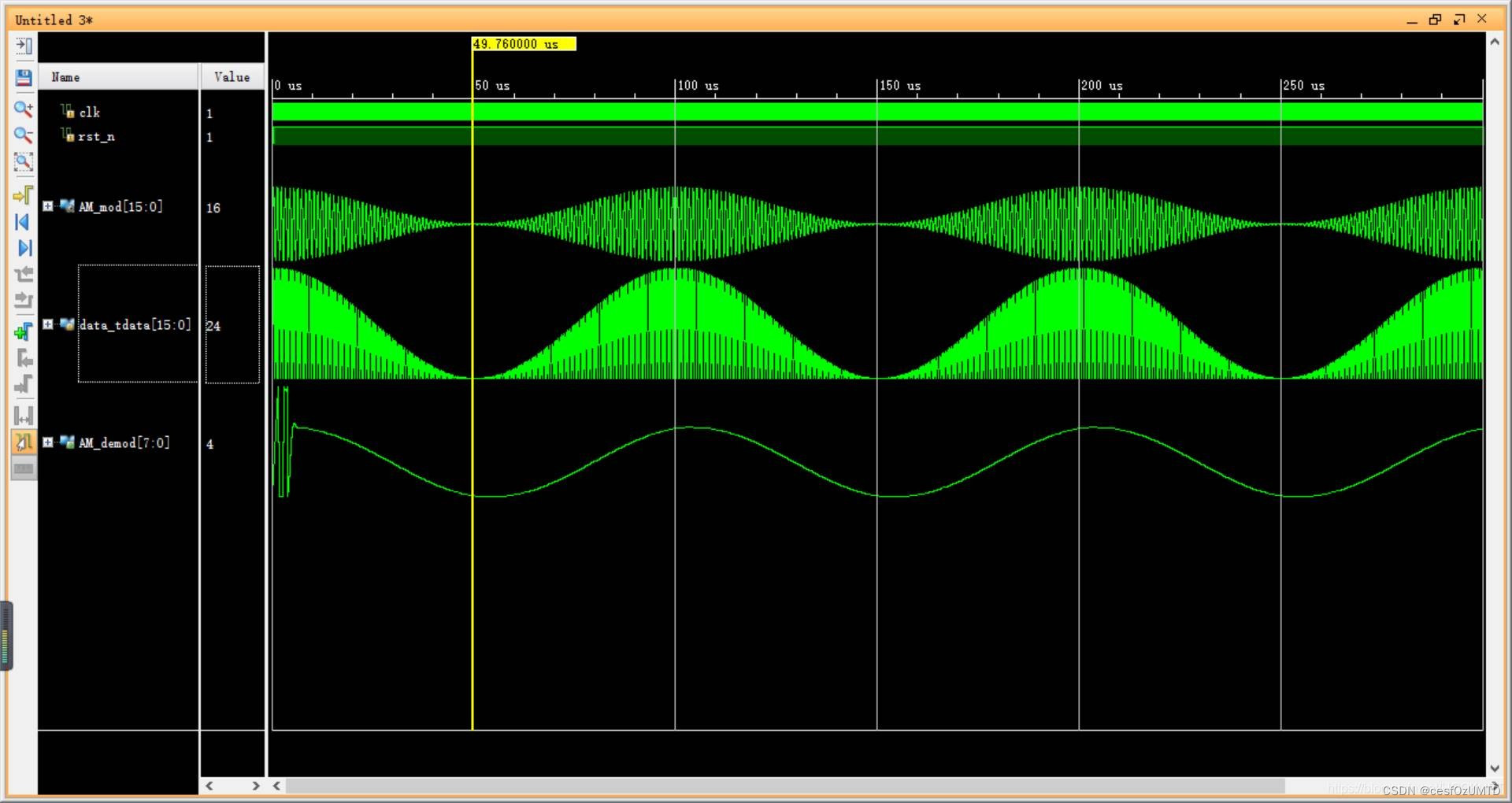

首先,我们提到的是基于zynq-7000系列的AM调制解调仿真。在这个仿真实验中,我们并没有涉及AD和DA的使用,而是将重点放在了纯粹的仿真过程上。通过对FPGA中AM调制解调模块的仿真,我们能更好地理解其工作原理及性能。

接下来,我们将介绍基于Artix-7系列的AM调制解调Vivado源码。与前面的仿真不同,这次实现中涉及到了AD和DA的使用。在信号处理过程中,我们需要从AD模块中读入信号,经过AM调制后再经过DA模块进行解调输出。通过在FPGA上实际运行这个源码,我们能够验证我们的算法设计和硬件实现的正确性。

在具体的实现过程中,我们首先需要设计FIR滤波器。为了方便设计和验证,我们采用了MATLAB来设计FIR滤波器,并将其转化为FPGA可识别的源码。通过在Vivado中导入这段MATLAB源码,我们能够快速搭建出滤波器模块。

在AM调制过程中,我们需要将输入信号与载波信号相乘,然后经过滤波器进行滤波。为了实现这个过程,我们需要设计乘法器和滤波器模块,并将其连接起来。在Vivado中,我们可以通过使用HDL语言如Verilog或VHDL来编写这些模块,并将其综合为FPGA可识别的源码。

一旦AM调制完成,我们需要进行解调以恢复原始信号。解调过程中,我们需要将AM调制后的信号与载波信号进行相乘,然后再次经过滤波器进行滤波。最后,我们将解调后的信号通过DA模块输出。在Vivado中,我们可以通过设计乘法器和滤波器模块,并将其与AD、DA模块连接起来来实现解调功能。

综上所述,本文围绕AM调制解调的FPGA源码展开了详细的介绍。通过在zynq-7000系列和Artix-7系列上的仿真和实现,我们能够更深入地了解和验证AM调制解调模块的工作原理和性能。在实际项目中,我们可以根据需求进行相应的调整和优化,以满足不同的应用场景。希望本文能为广大程序员提供一些关于AM调制解调在FPGA中实现的思路和方法,以及一些实践经验。

相关代码,程序地址:http://lanzouw.top/693163373842.html

8125

8125

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?