总线接口

1. PCI

2. USB

3. SPI

参考:https://blog.csdn.net/bleauchat/article/details/84821031

https://blog.csdn.net/fly__chen/article/details/52724109

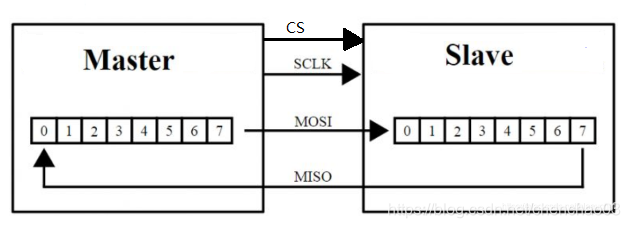

SPI(serial peripheral interface)是一种同步串行通信协议,由一个主设备和一个或多个从设备组成,主设备启动与从设备的同步通信,从而完成数据的交换。SPI是一种高速全双工同步通信总线,标准的SPI仅仅使用4个引脚,主要应用在 SPI Flash, 实时时钟(RTC)等。

SPI总线接口

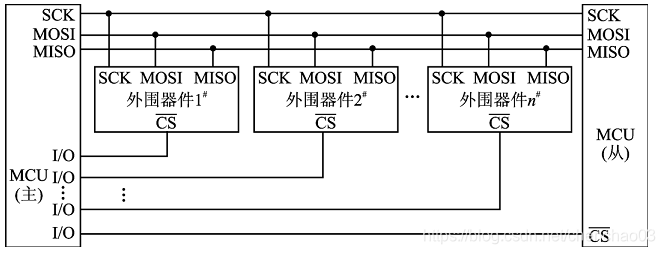

SPI 规定了两个 SPI 设备之间通信必须由主设备 (Master) 来控制次设备 (Slave). 一个 Master 设备可以通过提供 Clock 以及对 Slave 设备进行片选 (Slave Select) 来控制多个 Slave 设备, SPI 协议还规定 Slave 设备的 Clock 由 Master 设备通过 SCK 管脚提供给 Slave 设备, Slave 设备本身不能产生或控制 Clock, 没有 Clock 则 Slave 设备不能正常工作。

3.1 接口信号

SCLK 时钟信号,提供SPI的时钟信号。

CS 片选信号,提供Master选择哪个SPI Slave设备。

MOSI 数据输出信号,Master向Slave传输。

MISO 数据输入信号,Slave向Master传输。

3.2 时序

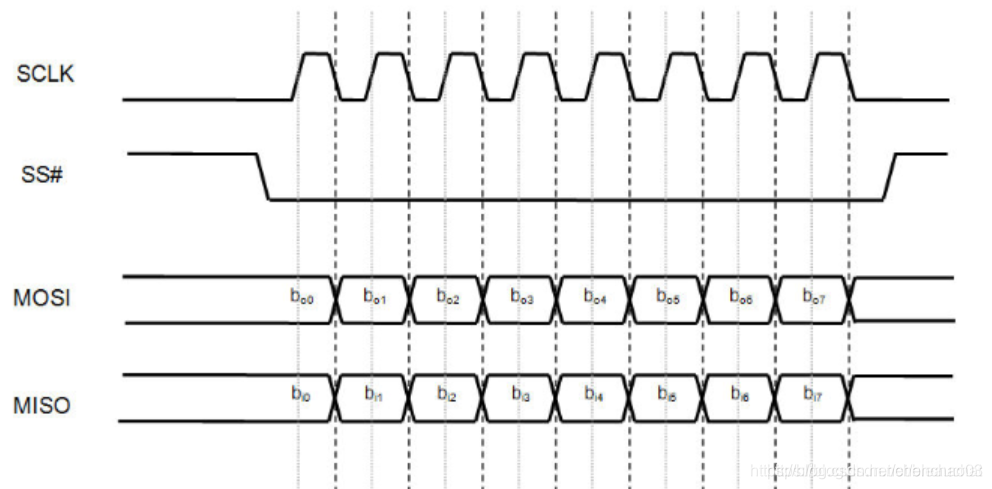

SPI传输模式有4种。不同的模式下,时序逻辑有所区别,这里仅描述一种参考时序。

在空闲状态下,SCK串行时钟线为低电平,当SS被主机拉低以后,数据传输开始,数据线MOSI和MISO的数据切换(Toggling)发生在时钟的下降沿(上图的黑色虚线),而数据线MOSI和MISO的数据的采样(Sampling)发生在数据的正中间(上图中的灰色实线)。

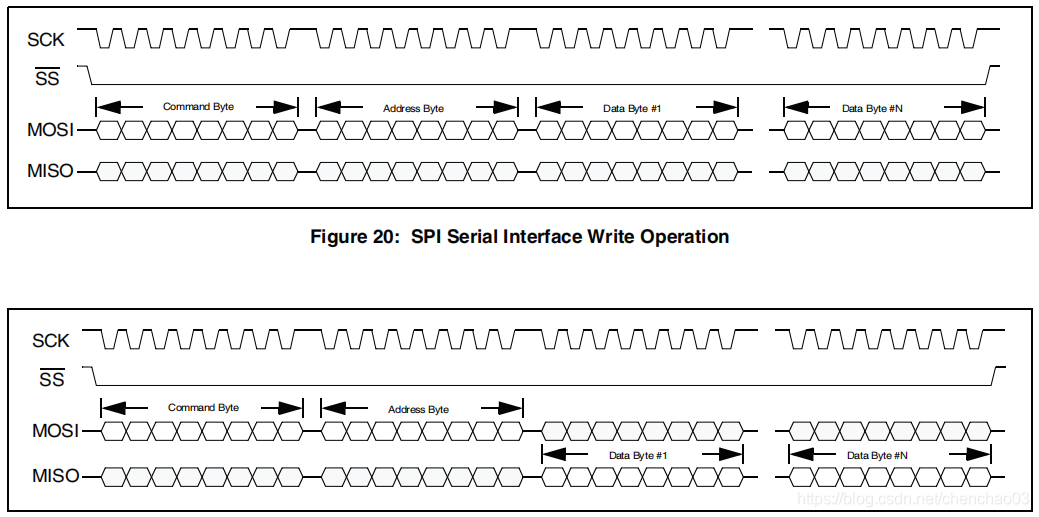

3.3 数据帧格式

以下为BCM交换芯片的SPI操作时序图。

Command Byte 操作命令字

Address Byte 操作地址

Data Byte 数据字节,读写的数据值

在写操作上,全部都在MOSI上传输,主控设备传输到从设备上。

在读操作上,操作命令字与操作地址在MOSI上,数据字节在MISO上。

3.4 操作模式

SPI支持中断模式及DMA操作。具体需要根据SPI控制器来确定。

4. IIC

参考:https://blog.csdn.net/u010650845/article/details/73467586

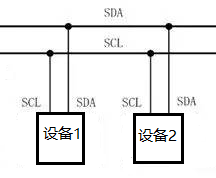

IIC总线分别由SDA(串行数据线)和SCL(串行时钟线)及上拉电阻组成。通信原理是通过对SCL和SDA线高低电平时序的控制,来产生I2C总线协议所需要的信号进行数据的传递。在总线空闲状态时,这两根线一般被上面所接的上拉电阻拉高,保持着高电平。

I2C通信方式为半双工,只有一根SDA线,同一时间只可以单向通信,485也为半双工,SPI和uart为双工。

I2C总线数据传输速率在标准模式下可达100kbit/s,快速模式下可达400kbit/s,高速模式下可达3.4Mbit/s。

4.1 接口信号

SDA 串行数据线,空闲时高电平

SCL 串行时钟,空闲时高电平

4.2 时序

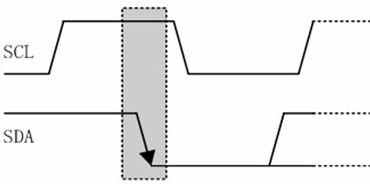

起始位:SCL为高电平期间 SDA出现下降沿

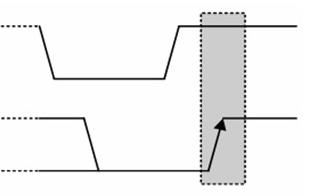

终止位:SCL为高电平期间 SDA出现上升沿

4.3 数据帧格式

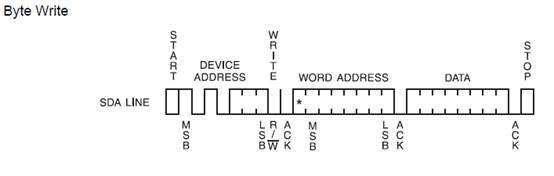

写操作

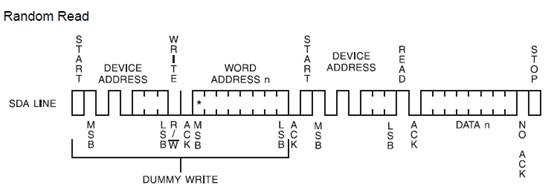

读操作

START 起始位,表示IIC传输开始。

DEVICE ADDRESS 设备地址,表示IIC设备的一个访问地址,一般为设备特有的固定的,或通过硬件来调整的。

WRITE/READ 读写操作位

WORD ADDRESS 数据地址,寄存器地址,存储数据的地址。

DATA 数据,传输的数据。

5. MDIO

参考:http://www.elecfans.com/emb/jiekou/202009291319033.html

MDIO接口,是Management Data Input/Output的缩写。MDIO接口包含在IEEE802.3协议中,是专用于以太PHY的管理的串行总线接口。

5.1 接口信号

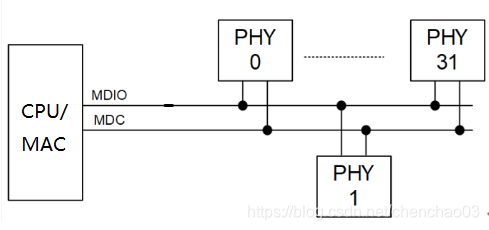

MDIO接口包含两根信号线:时钟线MDC、数据线MDIO。

MDC为MDIO接口时钟信号,来自主控(CPU,MAC),用来对MDIO的数据采样。MDC可以是非周期性信号。协议对MDC的高低电平的最大宽度并没有限制,仅限制了MDC的最小高低电平宽度不能小于160ns,最小周期不能小于400ns。这意味着MDC最高频率不能超过2.5MHz。

MDIO为MDIO接口数据信号,为双向信号,MAC和PHY均可以接管。用来在PHY控制芯片和PHY芯片之间的传递控制和状态信息。

5.2 接口时序

以MDC上升沿为基准。当MDIO由MAC输出时,需要满足建立时间、保持时间均大于10ns。当MDIO由PHY输出时,需要满足输出延迟不超过300ns。

5.3 帧格式

MDIO有两种模式:俗称1G MDIO和XG MDIO。

1G MDIO由IEEE 802.3 Clause22定义,主要应用于千兆/百兆的以太PHY。

XG MDIO由IEEE 802.3 Clause45定义,主要用于千兆以上的以太PHY。

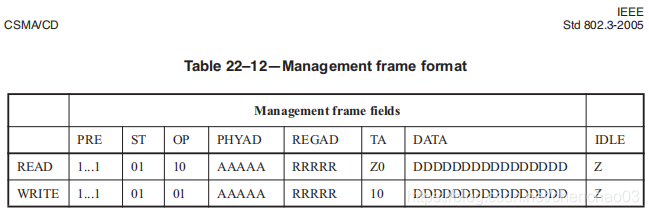

5.3.1 Clause22格式

主要描述MDIO信号线的数据帧格式:(MDIO发送bit序为高比特先传)

IDLE:空闲域。无MDIO帧发送时,MDIO接口输出高阻(外部有上拉电阻,总线上看到的是高电平)。

PRE:Preamble,前导。每帧发送前,STA通过MDIO连续发送32个MDC周期的高电平,同时通过MDC输出32个时钟周期。前导的作用是为PHY建立同步提供时间。如果STA能够确定PHY可以接收管理帧,可以压缩前导的发送。

ST:2bit,Start of Frame。帧起始符,2’b01代表帧起始。

OP:2bit,操作码。2’b10代表读,2’b01代表写。

PHYAD:5bit,PHY地址。因此1个MDIO最多管理32个PHY。MDIO在访问PHY之前,需要提前知晓各个PHY的地址。所有PHY均需要对地址0进行响应。

REGAD:5bit,寄存器地址。总共32个寄存器地址,协议对前16个寄存器地址进行了详细的定义。其中地址0为控制寄存器,地址1为状态寄存器,其他14个地址为扩展寄存器。

TA:2bit,Turnaround。TA是地址传输和数据传输转换时的空闲时间。因为读操作的时候,地址传输和数据传输控制方不同,设置2bit TA的目的就是为了防止MDIO总线上产生竞争。读情形,TA第1bit,PHY和STA均释放总线控制输出高阻。TA第2bit,总线交由PHY控制,输出0,即读操作时TA为2‘bZ0(由于总线有上拉电阻存在,从总线上看到的依然是2’b10)。写情形,TA由STA输出2‘b10。

DATA:16bit,数据域。写操作的时候,STA用来发送写数据。读操作的时候,PHY用来发送读数据。

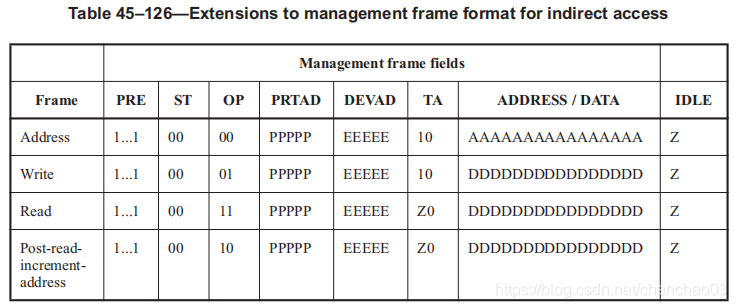

5.3.2 Clause45格式

MDIO Clause45在Clause22基础上做了一些扩展,目的是为了访问更多的寄存器。主要修订增加如下:

ST由01修改为00。

OP进行了重新定义。00:地址帧 01:写 11:读 10:增量读(Post-read-increment-address)。

PHYAD域修改名称为PRTAD,端口地址但仍代表PHY地址。

REGAD修改为DEVAD,Clause45将PHY内部子模块的地址进行细分,这些子模块用DEVAD寻址。子模块内部的寄存器则使用地址帧进行寻址。

Clause45的修改大大扩展了访问地址范围,但是由于地址和读写操作的分离,导致访问效率降低一半。为了解决该问题,Clause45新增了增量读模式,允许先发送一次地址帧,后续仅发送增量读操作。在每次读完成后,PHY会自动将地址移动到下一个相邻的寄存器地址,这样就能完成从指定地址开始顺序读取设备内部的寄存器,而无需重新发送地址帧,访问效率可以和Clause22相当。

6. NAND Flash

7. CAN

8. 高速收发器SerDes

高速收发器技术就 SerDes。SerDes 是 SERializer (串行器)/ DESerializer (解串器)的简称,是一种串行收发技术,串行器在发送端将接收多行并行输入数据,并将其压缩成较少的数据行再串行输出;而解串器就是在接收端,将序列化的串行数据作为输入、恢复并输出原始并行数据。收发通道独立,直接从数据线中提取时钟,所以这种技术只需要两对差分线就能完成全双工高速数据收发,减少了芯片的引脚数和外围 PCB 布线的数量,减少设计的成本及外围电路的布线空间,特别适用于现代高速数字系统。同时,SerDes 架构通过将单端 TTL 和 CMOS 信号转换为低电压差分信号,这样可以很好地减少信号的噪声和电磁干扰的影响,进而可以实现高速率、远距离传输。大量常见高速接口都是基于Serdes技术实现的,如PCIe,USB3.0等。

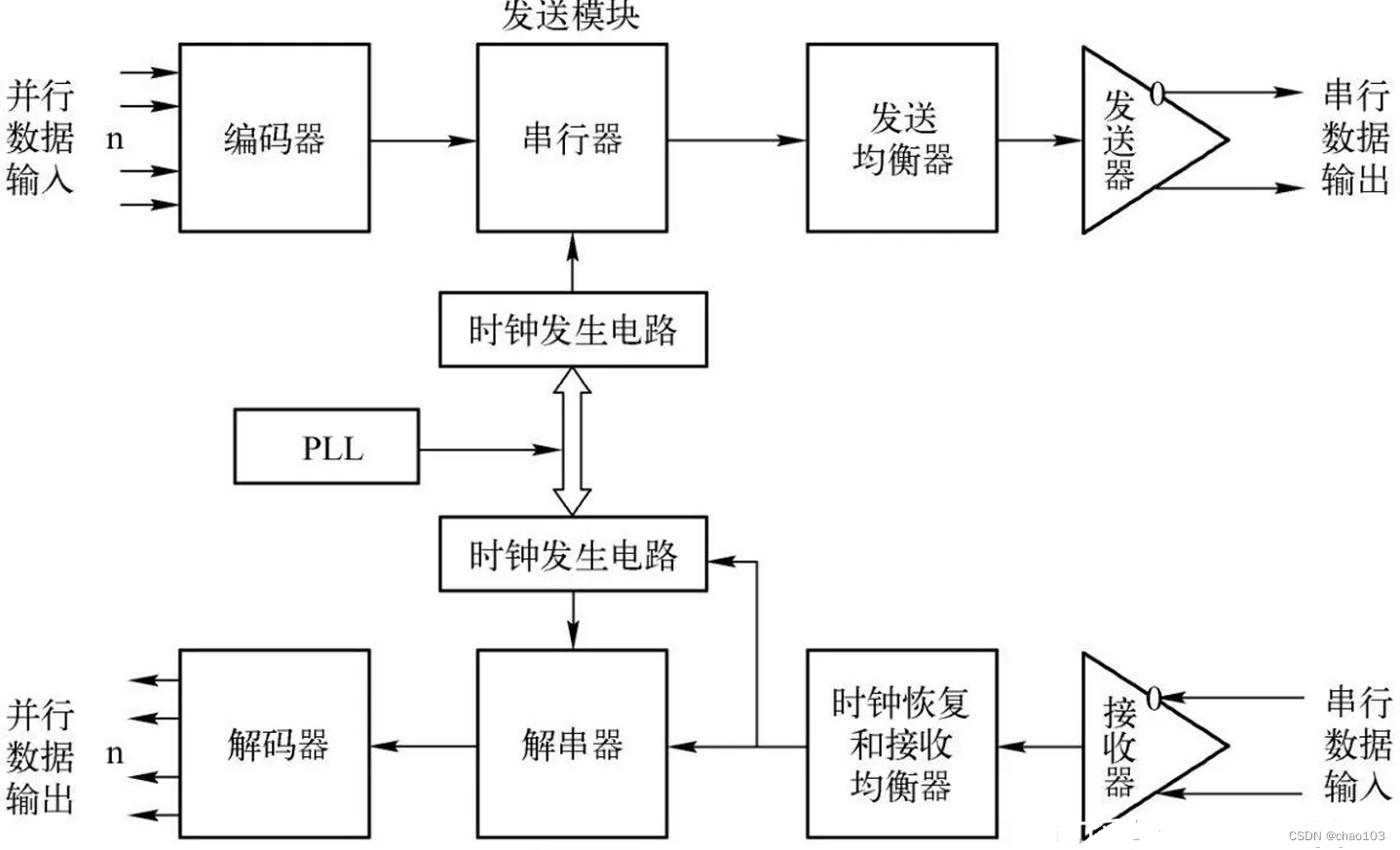

SerDes 的主要构成分为 3 部分:锁相环( Phase Locking Loop :PLL)模块、发送模块和接收模块。

8.1 SerDes与SGMII

- 外接接口

SGMII模式通常用来连接GE电模块,支持10/100/1000BASE-T电模块,如强制1000M电模块或者10/100/1000M自适应电模块。

SerDes模式通常用来接GE光模块,支持1000BASE-X光模块。

2.传输

SGMII模式下,GE端口速率为1.25Gbps,需要插入2bit控制信号变成10b;除去报文控制信息,实际传输速率为1Gbps。

SerDes模式下,GE端口速率为1.25Gbps,但是需要做8B/10B编解码,因此实际传输速率也是1Gbps。

3.原理

SGMII模式的8B/10B编解码工作通过PHY芯片完成。

SerDes模式的8B/10B编解码工作由MAC芯片完成。

通过8B/10B编码后的数据在物理线或光传输。

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?