离开微电子行业有一年时间了,最近准备返回老本行,因此想先把Verilog捡起来。

最简单的Verilog例子就是时钟分频,此处写了个整数分频,可以实现偶数分频,50%占空比,奇数分频,非50%占空比。

代码是参数化,分频数可调整。

代码如下:

//===========================================================

// Author: seuchenrui@126.com

//

// Description:

// This is a simple verilog code for clock frequency division

// this code can be used to get

// 1. even integer division (duty = 50%)

// 2. odd inetger division (duty !=50%)

//===========================================================

module clock_div_integer

#(parameter DIV_NUMBER=31)

(

input iCLK,

input iRESET,

output reg oCLK

);

reg [clogb2(DIV_NUMBER)-1:0] count;

always@(posedge iCLK or negedge iRESET)

begin

if(!iRESET)

count <= 'd0;

else if(count == DIV_NUMBER -1)

count <= 'd0;

else

count <= count + 1'b1;

end

always@(posedge iCLK or negedge iRESET)

begin

if(!iRESET)

oCLK <= 1'b0;

else if(count == DIV_NUMBER/2-1)

oCLK <= ~oCLK;

else if(count == DIV_NUMBER -1)

oCLK <= ~oCLK;

else

oCLK <= oCLK;

end

//================================

// this function is used to check

// bitwidth of the data

//================================

function integer clogb2;

input [31:0] depth;

begin

for(clogb2 = 0; depth>0;clogb2=clogb2+1)

depth = depth>>1;

end

endfunction

endmodule

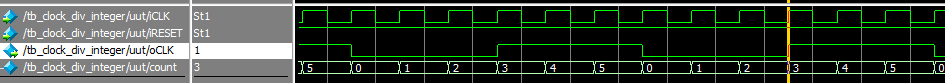

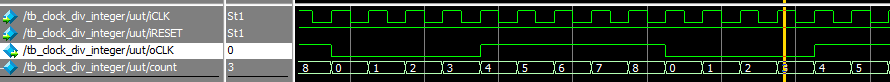

奇数仿真波形

明天继续谢谢时钟分频的代码

2038

2038

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?